先給大家出一個題目:當x為5時,y=x << 6 + x <<3 + x << 2 + x的結果為多少,即y的值是多少?

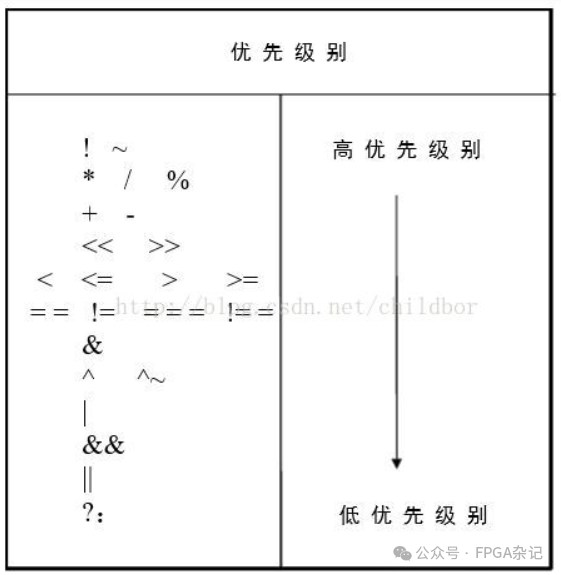

我先不給出答案,先貼上正確的運算符優先級順序,如下圖所示:

俗話說溫故而知新,今天回顧一下verilog的運算符的優先級。

說一下回顧這個原因:今天打算用verilog實現一個乘法器,即:y=77*x。為了加快運算時間,將77轉換為二級制(1001101),然后使用了移位寄存器來實現乘法運算,具體代碼如下:y=x << 6 + x <<3 + x << 2 + x。但是仿真結果不對,仿真結果為0的概率比較大。之前還以為是x的位寬太小導致的,但是修改位寬之后還是不行,所以又重新審視了一下這段代碼,懷疑是運行操作符的優先級有問題導致的,查閱書籍發現確實是這樣的:加法的優先級高于左移運算,導致先進行加法運算再進行移位運算,所以結果和預期不一致。

實際上,要實現y=77*x運算,正確的verilog代碼如下:y=(x << 6)+(x <<3)+(x << 2)+ x。

所以說,剛開始給出題目的答案不是我不給出,實際上按照正確優先級計算的結果沒有太多的意義。

審核編輯:湯梓紅

-

Verilog

+關注

關注

28文章

1351瀏覽量

110390 -

乘法器

+關注

關注

8文章

206瀏覽量

37192 -

運算符

+關注

關注

0文章

172瀏覽量

11107

原文標題:考題

文章出處:【微信號:FPGA雜記,微信公眾號:FPGA雜記】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

verilog運算符的優先級

verilog運算符的優先級

評論