RZ/G2L串口簡介

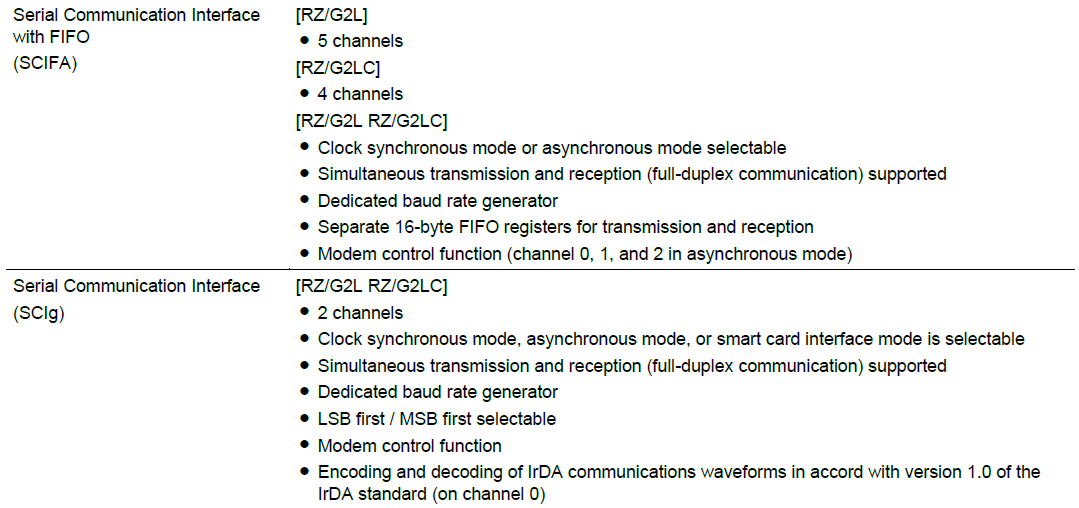

瑞薩RZ/G2L的串口簡稱SCI,全稱Serial Communication Interface。

RZ/G2L有兩種串口,一種帶FIFO叫SCIFA,另一種不帶FIFO叫SCIg。

所以,RZ/G2L有5路SCIFA和2路SCIg總共7路的串口。

RZ/G2L串口驅(qū)動

包含驅(qū)動代碼和設(shè)備樹兩部分:

內(nèi)核中的驅(qū)動文件sh-sci.c

該源碼文件路徑:drivers/tty/serial/sh-sci.c,該驅(qū)動代碼包含SCIFA和SCIg兩種型號的完整驅(qū)動代碼。

編譯內(nèi)核的時候需進行以下配置

左右滑動查看完整內(nèi)容

egrep -rin "CONFIG_SERIAL_SH_SCI" .out/.config 2180:CONFIG_SERIAL_SH_SCI=y 2181:CONFIG_SERIAL_SH_SCI_NR_UARTS=18 2182:CONFIG_SERIAL_SH_SCI_CONSOLE=y 2183:CONFIG_SERIAL_SH_SCI_EARLYCON=y 2184:CONFIG_SERIAL_SH_SCI_DMA=y

該配置能夠確保sh-sci.c的驅(qū)動代碼能夠被編譯包含到Image中。

github上提供的內(nèi)核源碼的defconfig中默認已包含SCI驅(qū)動代碼的編譯。

SCI串口的設(shè)備樹節(jié)點在r9a07g044.dtsi中定義,分別定義了scif0~4, sci0~1共7路。

左右滑動查看完整內(nèi)容

scif0: serial@1004b800 {

compatible = "renesas,scif-r9a07g044";

reg = <0 0x1004b800 0 0x400>;

interrupts = ,

,

,

,

,

;

interrupt-names = "eri", "rxi", "txi",

"bri", "dri", "tei";

clocks = <&cpg CPG_MOD R9A07G044_SCIF0_CLK_PCK>;

clock-names = "fck";

dmas = <&dmac 0x4e79>, <&dmac 0x4e7a>;

dma-names = "tx", "rx";

power-domains = <&cpg>;

resets = <&cpg R9A07G044_SCIF0_RST_SYSTEM_N>;

status = "disabled";

};

scif1: serial@1004bc00 {

compatible = "renesas,scif-r9a07g044";

reg = <0 0x1004bc00 0 0x400>;

interrupts = ,

,

,

,

,

;

interrupt-names = "eri", "rxi", "txi",

"bri", "dri", "tei";

clocks = <&cpg CPG_MOD R9A07G044_SCIF1_CLK_PCK>;

clock-names = "fck";

dmas = <&dmac 0x4e7d>, <&dmac 0x4e7e>;

dma-names = "tx", "rx";

power-domains = <&cpg>;

resets = <&cpg R9A07G044_SCIF1_RST_SYSTEM_N>;

status = "disabled";

};

scif2: serial@1004c000 {

compatible = "renesas,scif-r9a07g044";

reg = <0 0x1004c000 0 0x400>;

interrupts = ,

,

,

,

,

;

interrupt-names = "eri", "rxi", "txi",

"bri", "dri", "tei";

clocks = <&cpg CPG_MOD R9A07G044_SCIF2_CLK_PCK>;

clock-names = "fck";

dmas = <&dmac 0x4e81>, <&dmac 0x4e82>;

dma-names = "tx", "rx";

power-domains = <&cpg>;

resets = <&cpg R9A07G044_SCIF2_RST_SYSTEM_N>;

status = "disabled";

};

scif3: serial@1004c400 {

compatible = "renesas,scif-r9a07g044";

reg = <0 0x1004c400 0 0x400>;

interrupts = ,

,

,

,

,

;

interrupt-names = "eri", "rxi", "txi",

"bri", "dri", "tei";

clocks = <&cpg CPG_MOD R9A07G044_SCIF3_CLK_PCK>;

clock-names = "fck";

dmas = <&dmac 0x4e85>, <&dmac 0x4e86>;

dma-names = "tx", "rx";

power-domains = <&cpg>;

resets = <&cpg R9A07G044_SCIF3_RST_SYSTEM_N>;

status = "disabled";

};

scif4: serial@1004c800 {

compatible = "renesas,scif-r9a07g044";

reg = <0 0x1004c800 0 0x400>;

interrupts = ,

,

,

,

,

;

interrupt-names = "eri", "rxi", "txi",

"bri", "dri", "tei";

clocks = <&cpg CPG_MOD R9A07G044_SCIF4_CLK_PCK>;

clock-names = "fck";

dmas = <&dmac 0x4e89>, <&dmac 0x4e8a>;

dma-names = "tx", "rx";

power-domains = <&cpg>;

resets = <&cpg R9A07G044_SCIF4_RST_SYSTEM_N>;

status = "disabled";

};

sci0: serial@1004d000 {

compatible = "renesas,r9a07g044-sci", "renesas,rz-sci";

reg = <0 0x1004d000 0 0x400>;

interrupts = ,

,

,

;

interrupt-names = "eri", "rxi", "txi", "tei";

clocks = <&cpg CPG_MOD R9A07G044_SCI0_CLKP>;

clock-names = "fck";

power-domains = <&cpg>;

resets = <&cpg R9A07G044_SCI0_RST>;

status = "disabled";

};

sci1: serial@1004d400 {

compatible = "renesas,r9a07g044-sci", "renesas,rz-sci";

reg = <0 0x1004d400 0 0x400>;

interrupts = ,

,

,

;

interrupt-names = "eri", "rxi", "txi", "tei";

clocks = <&cpg CPG_MOD R9A07G044_SCI1_CLKP>;

clock-names = "fck";

power-domains = <&cpg>;

resets = <&cpg R9A07G044_SCI1_RST>;

status = "disabled";

};

設(shè)備樹文件路徑

arch/arm64/boot/dts/renesas/r9a07g044.dtsi

根據(jù)項目需要,使能需要使用的設(shè)備節(jié)點,如欲使用SCIFA2:

左右滑動查看完整內(nèi)容

&scif2 {

pinctrl-0 = <&scif2_pins>;

pinctrl-names = "default";

uart-has-rtscts;

status = "okay";

};

注意需通過scif2_pins正確處理IO口復(fù)用問題。如果不使用DMA需要將設(shè)備節(jié)點中的dmas和dma-names刪除。

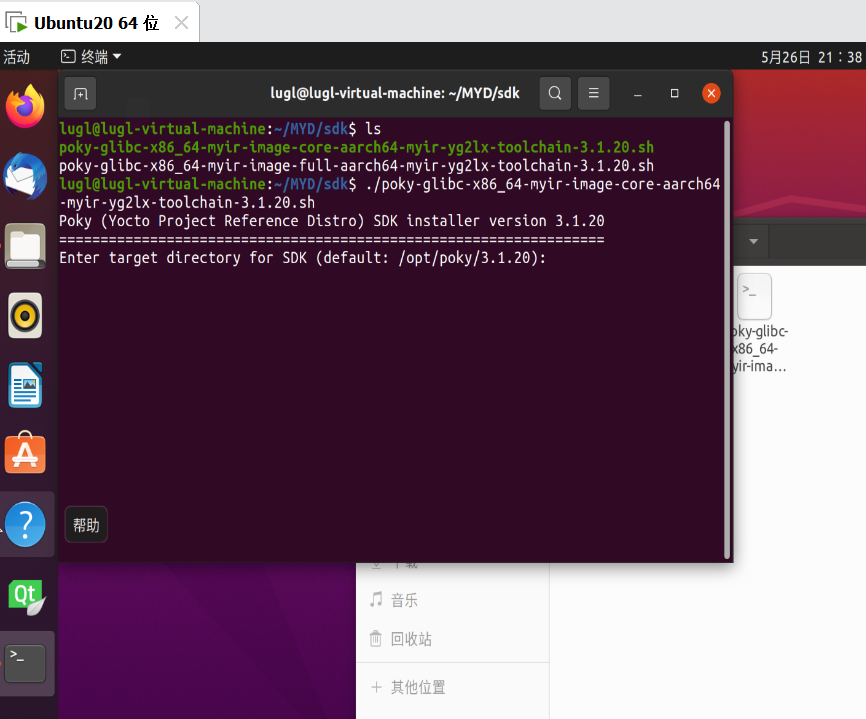

編譯內(nèi)核:

左右滑動查看完整內(nèi)容

export ARCH=arm64 export CROSS_COMPILE=aarch64-none-elf- export PATH=$PATH:/opt/arm/gcc-arm-10.2-2020.11-x86_64-aarch64-none-elf/bin make defconfig O=.out && make -j8 O=.out

使用當前編譯生成的內(nèi)核Image和dtb

左右滑動查看完整內(nèi)容

.out/arch/arm64/boot/Image .out/arch/arm64/boot/dts/renesas/r9a07g044l2-smarc.dtb

啟動板子后就能在系統(tǒng)路徑下生成/dev/ttySC2節(jié)點。

Linux應(yīng)用層使用RZ/G2L的串口SCI

RZ/G2L的串口設(shè)備節(jié)點在Linux應(yīng)用層遵循POSIX標準,使用方法和PC端的Ubuntu系統(tǒng)并無差別。

RZ/G2L除了支持市面上常用的串口波特率如9600/115200/921600等,實際上除POSIX系統(tǒng)定義的波特率都支持外,RZ/G2L能夠支持的最大串口波特率是12.5Mbps,下一篇我們將介紹如何在內(nèi)核驅(qū)動代碼中實現(xiàn)RZ/G2L的最大波特率12.5Mbps。

審核編輯:湯梓紅

-

內(nèi)核

+關(guān)注

關(guān)注

3文章

1382瀏覽量

40421 -

瑞薩

+關(guān)注

關(guān)注

35文章

22310瀏覽量

86736 -

串口

+關(guān)注

關(guān)注

14文章

1557瀏覽量

77033 -

SCI

+關(guān)注

關(guān)注

1文章

56瀏覽量

20172

原文標題:RZ/G2L串口SCI的使用(上)

文章出處:【微信號:瑞薩MCU小百科,微信公眾號:瑞薩MCU小百科】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

基于瑞薩電子RZ/G2L的FET-G2LD-C核心板和OK-G2LD-C開發(fā)板評測

瑞薩RZ/G2L串口SCI的使用(下)

RZ/G2L高速虛擬串口方案 基于瑞薩RZ/G2L SMARC開發(fā)板的虛擬(Virtual UART)實現(xiàn)方案

瑞薩RZ/G2L串口SCI的使用(上)

瑞薩RZ/G2L串口SCI的使用(上)

評論