光互連CPU技術

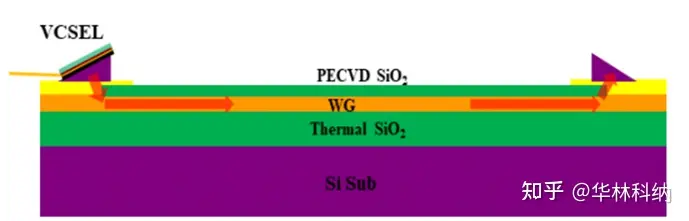

實驗演示了三種可以實現與集成在光網絡芯片(ONC)上的CPU核心的光互連的技術。該粘合劑技術具有>99%的透明度、高達400℃的耐高溫性、耐清洗溶劑性以及GaP棱鏡與波導之間的折射率匹配的特性。

聚酰亞胺微透鏡具有準直25Gbps VCSEL的輸出光束以將光耦合到光波導中的特性。VCSEL或光電二極管的封裝尺寸具有0.4mm2的面積和0.64mm的高度,可以連接到棱鏡。除了棱鏡處的反射損耗外,從VCSEL到波導的凈耦合損耗被測量為0.855dB。通過腔型波導的傳播損耗被測量為0.258dB/cm。要與8核CPU芯片集成的光學設備的面積比可用面積174mm2小得多,<30mm2,該可用面積是根據臺式CPU的當前管芯面積估計的。

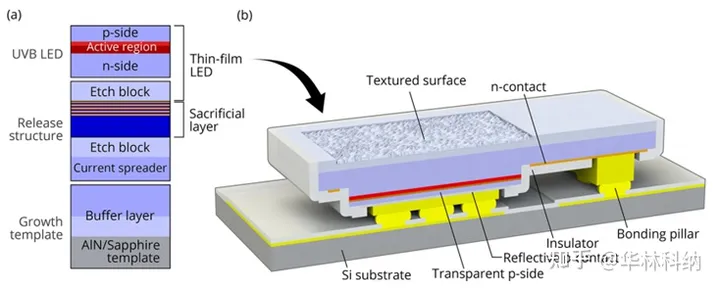

通過表面紋理化增加薄膜倒裝UVB發光二極管的光提取

紫外線發光二極管(LED)的壁插效率較低,這在很大程度上受到較差的光提取效率(LEE)的限制。具有粗糙的N極性AlGaN表面的薄膜倒裝芯片(TFFC)設計可以顯著改善這一點。我們在這里展示了一種實現在UVB范圍(280?320 nm)內發射TFFC LED的使能技術,其中包括標準LED處理與電化學蝕刻相結合以去除襯底。

電化學蝕刻的集成通過外延犧牲層和蝕刻阻擋層與LED的封裝相結合來實現。當TFFC LED的N極性AlGaN側被化學粗糙化時,LEE增強了約25%,達到2.25%的外量子效率。通過進一步優化表面結構,我們的光線追蹤模擬預測TFFC LED比倒裝芯片LED的LEE更高,從而獲得更高的壁插效率。

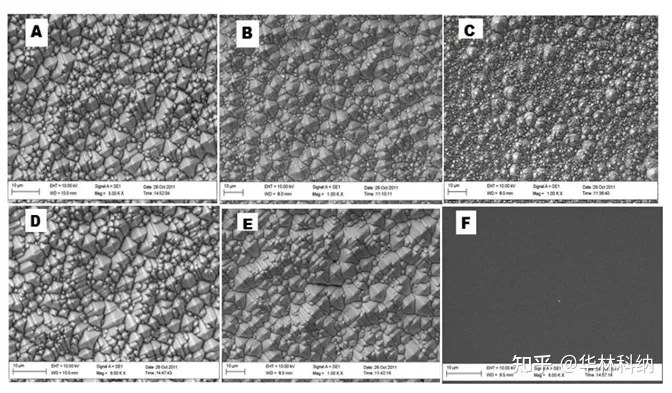

晶硅片各向異性表面制絨工藝實驗分析

本研究報告了使用氫氧化鉀(KOH)水溶液和異丙醇(IPA)的混合物作為絡合劑來增強光吸收并降低可見光譜中的光學反射率的硅片表面紋理化的實驗研究。實驗中使用了直徑100 mm、2“<100>取向、n型、電阻率(Ωcm)為7-21、表面拋光和研磨的Crochralski(CZ)硅片。所研究的工藝變量包括溫度(60–90)°C,蝕刻時間(30–60)分鐘,KOH和IPA的濃度分別為(1–4)mg/l和(2–8)mg/l。

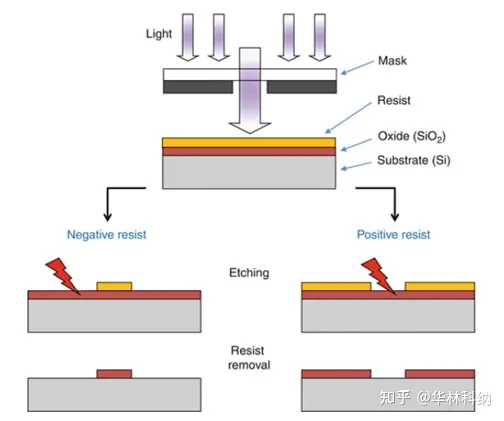

基于氫氧化鉀各向異性刻蝕的高固硅微針制備

本文研究了基于KOH各向異性刻蝕的高固體硅微針的制備,旨在找到一種可控的方法來制備具有良好高度均勻性和尖端銳度的500μm高微針。在本研究中,使用200nm低應力LPCVD SiNx作為KOH蝕刻掩模;掩模形狀為正方形,其側面沿著硅片的<100>方向;在29wt%的KOH溶液中,在79℃下進行濕法刻蝕

關鍵詞:光子集成電路、光互連、硅光子學、光接收器、垂直腔面發射激光器、發光二極管,AlGaN,電化學蝕刻,表面紋理,光提取,表面制絨工藝,氫氧化鉀,各向異性刻蝕

審核編輯 黃宇

-

集成電路

+關注

關注

5392文章

11623瀏覽量

363189 -

二極管

+關注

關注

147文章

9706瀏覽量

167575 -

cpu

+關注

關注

68文章

10904瀏覽量

213026

發布評論請先 登錄

相關推薦

半導體資料丨光子集成電路,發光二極管,制絨工藝,氫氧化鉀

半導體資料丨光子集成電路,發光二極管,制絨工藝,氫氧化鉀

評論