在高速信號傳輸中,信號傳輸線上的反射是一個重要的問題。當信號從信號源發送到終端設備時,信號在傳輸線上會遇到線路特性不連續的變化,如端口、接口或連接器的變化。這種變化導致信號的部分能量被反射回傳輸線中,形成反射波。這種反射波可能會干擾原始信號,引發信號完整性問題,如時序錯誤、眼圖閉合不良等。

如何進行高速信號反射仿真

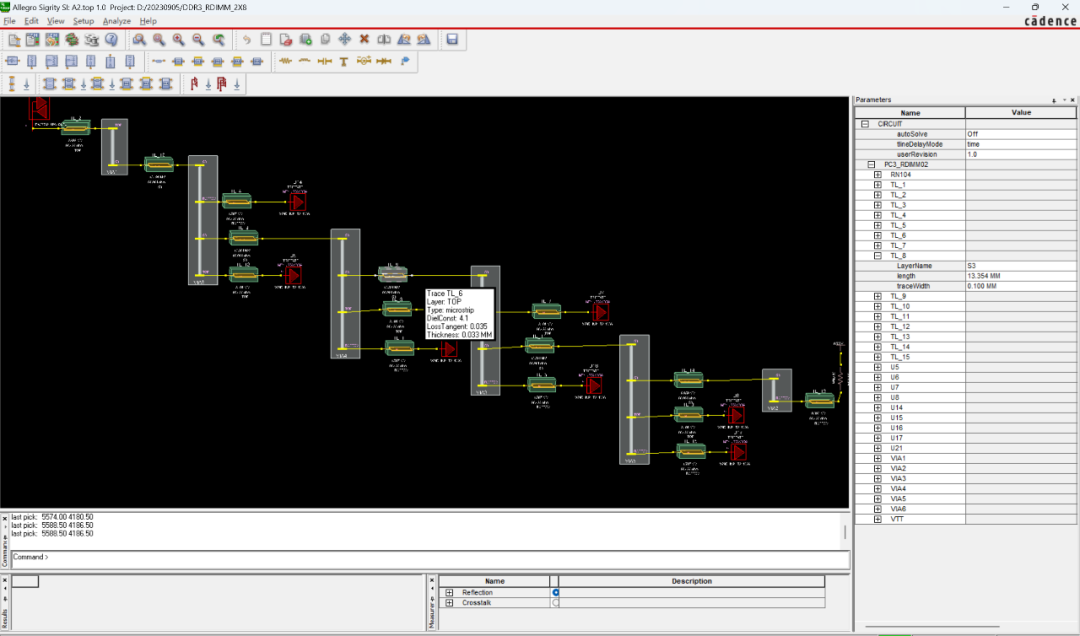

接下來我們使用SigXplorer來學習如何進行高速信號反射仿真。

Cadence SigXplorer軟件是一種用于高速信號完整性分析和信號完整性的解決方案。它主要用于設計和驗證電子產品中的高速信號傳輸線路,以確保信號的可靠性和穩定性。

SigXplorer可以對高速信號傳輸線路進行電磁仿真分析,包括考慮反射、傳輸線損耗、散射參數等因素。通過仿真,可以分析信號的傳輸特性,如延遲、振幅、眼圖、時域波形等,幫助設計師評估信號完整性。

SigXplorer可以幫助設計師分析和優化信號傳輸線路的工程參數,例如線路幾何、終端阻抗匹配、負載和驅動器配置等,以降低反射、串擾、眼圖閉合等問題的風險。通過對不同設計方案進行仿真和比較,設計師可以選擇最優的方案來提高信號完整性。

在高速信號傳輸時,傳輸線非理想線,包含分布參數如電容、電感和電阻,此時對于信號來講這些參數形成的阻抗就是瞬時阻抗值。當信號在傳輸過程中遇到阻抗突變時,會導致部分能量返回,形成反射。

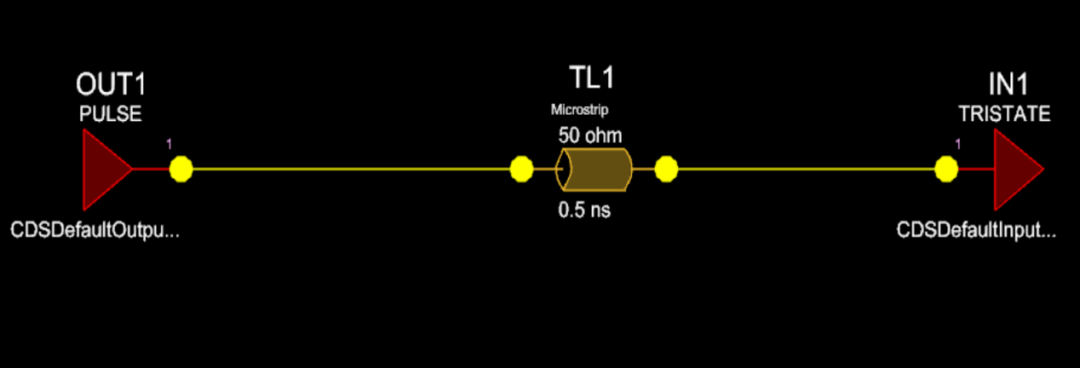

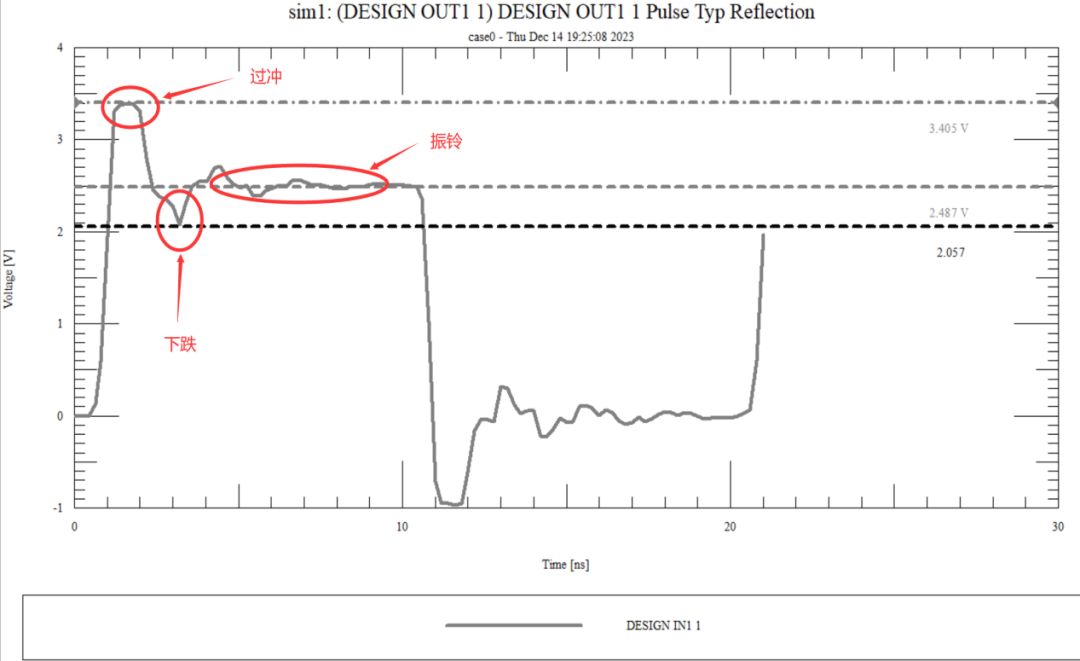

圖 1

反射會造成過沖、過跌、振鈴(信號來回反射)等問題。嚴重的過沖、過跌問題會導致信號傳輸錯誤。

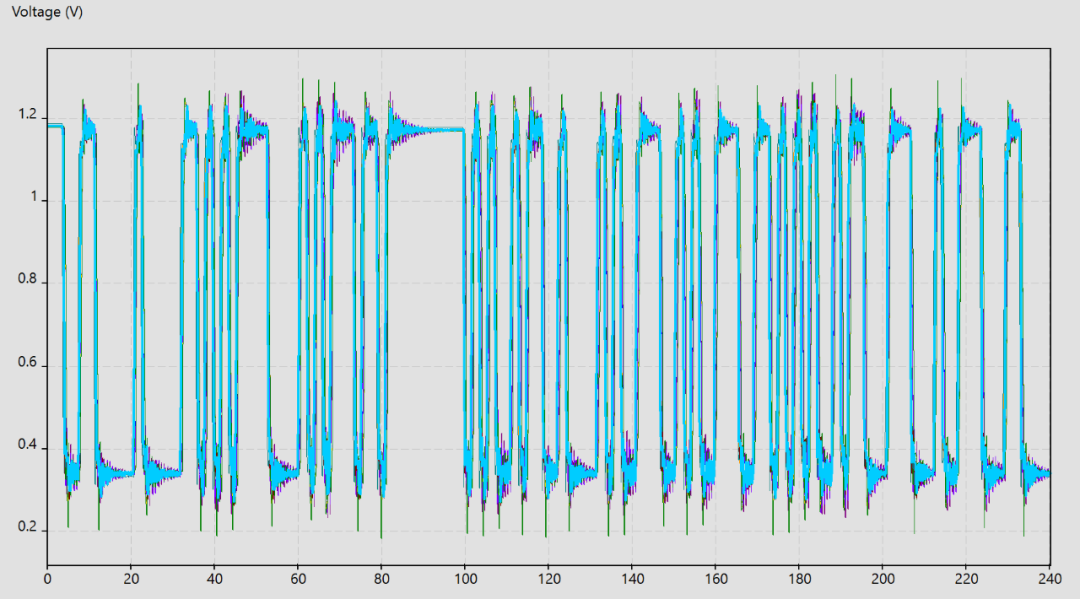

圖 2

在圖1的傳輸鏈路中,OUT1輸入,內阻約10 Ohm,IN1端輸出,內阻無窮大,傳輸線TL1阻抗50 Ohm。當發射端激勵為2.5v,50MHz的方波時,接收的信號波形如圖2所示。信號過沖到3.4V,然后下跌到2v,再經過反復震蕩后穩定在2.5v。

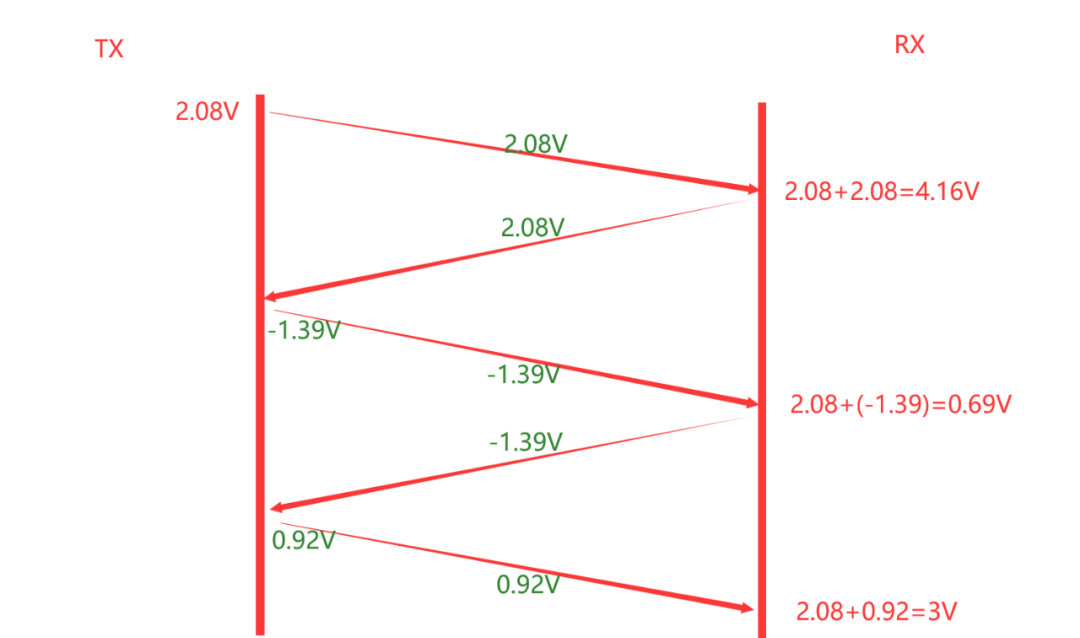

反射系數為(末端阻抗-始端阻抗)/(末端阻抗+始端阻抗),初始電壓為發射端內阻10 Ohm與傳輸線50 Ohm的分壓,即2.08V。具體反射過程如圖3所示。(由于傳輸線損耗問題,理想情況下的理論計算與實際會有偏差)

圖 3

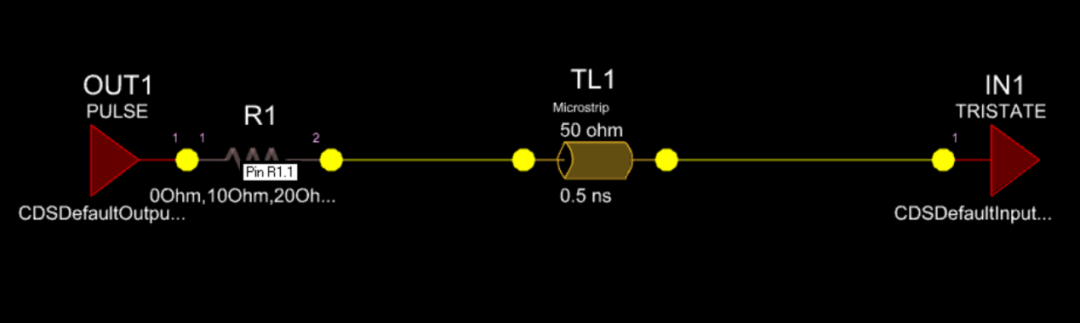

為了減少信號反射,可以采取一些措施,例如使用串聯端接電阻。如圖4所示。

圖 4

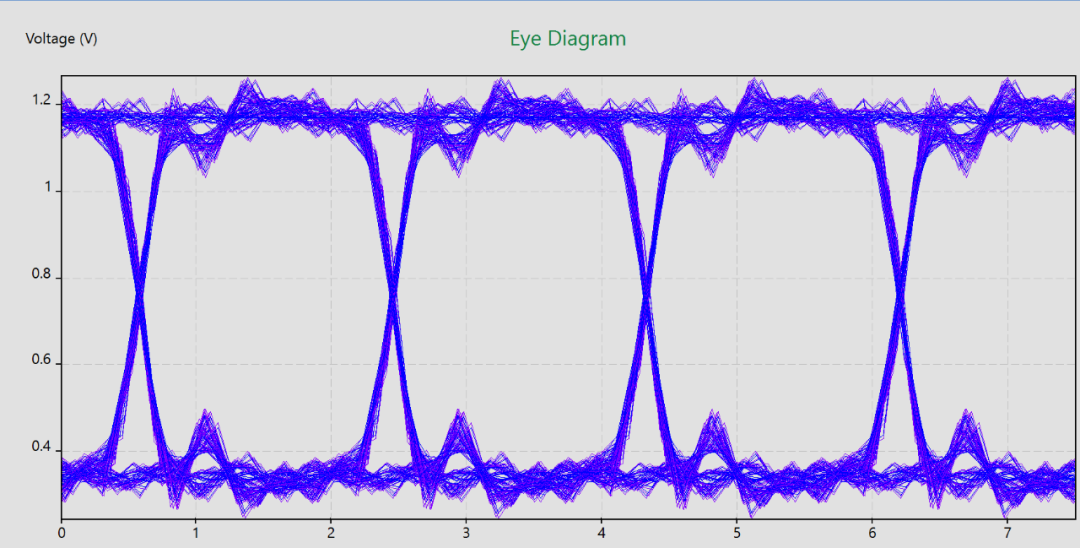

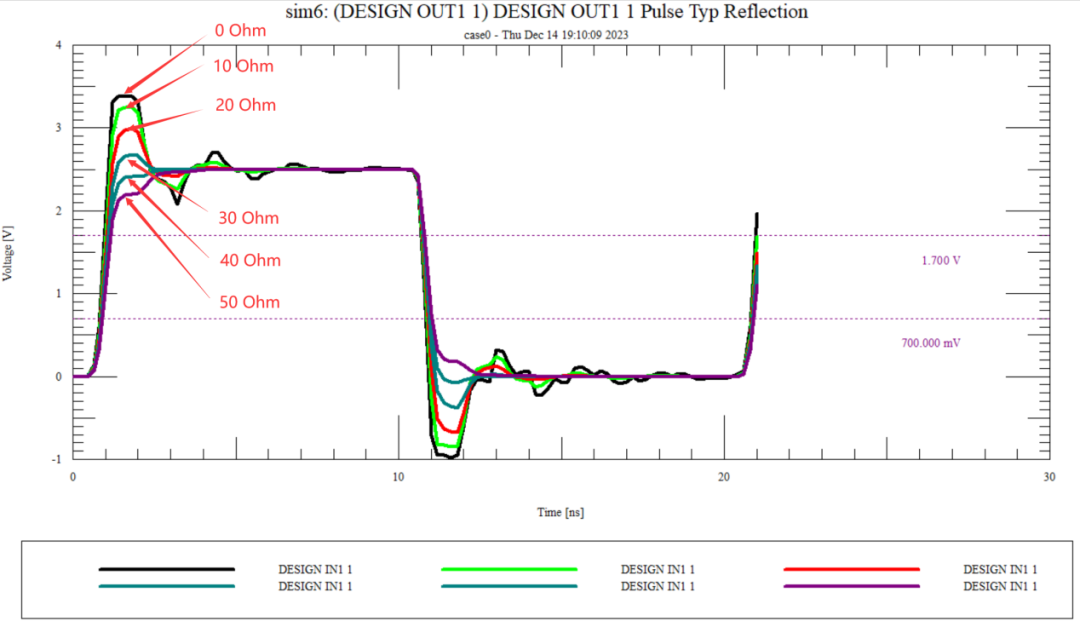

當串聯的電阻阻值從0 Ohm到50 Ohm之間變化時,信號的反射也會相應變化,接收端的信號波形如圖5所示。可以看出,當串聯電阻為40 Ohm時,發射端內阻與40 Ohm電阻之和約等于傳輸線阻抗50 Ohm,從上述反射系數的計算方法可知,發射端一側反射系數為0,而接收端一側的反射系數仍然是1,所以,信號在接收端全部反射回來,在發射端不在反射,信號只經歷一次反射,從而使信號的傳輸更穩定。

圖 5

圖 5

通常,發射端的輸出阻抗較低,接收端的輸入阻抗遠高于傳輸線特性阻抗,如果不做任何處理,信號就會產生反射,影響信號傳輸質量。阻抗突變是產生反射的主要原因,在PCB設計過程中,需要盡可能避免阻抗突變,來提高信號傳輸質量。

SigXplorer軟件主要用于高速信號完整性分析和優化。它幫助設計師評估和改進信號傳輸線路的性能,確保信號的可靠性和穩定性,以滿足高速系統設計的要求。進行高速信號反射仿真分析可以幫助設計師更好地了解信號的傳輸特性和反射問題,從而優化設計,提高信號的完整性和可靠性。

上述過程是在SigXplorer中實現的仿真過程,目前Sigrity 2021最新版本的最新工具SigrityTopology Explorer不僅具有SigXplorer的拓撲自動提取、仿真與規則管理器集成等功能,還使用了與Sigrity SystemSI相同的模塊設計和交互方式,IO model也可以直接使用IBIS模型,大大優化了SigXplorer的使用體驗。

-

仿真

+關注

關注

50文章

4124瀏覽量

133991 -

傳輸線

+關注

關注

0文章

377瀏覽量

24130 -

高速信號

+關注

關注

1文章

231瀏覽量

17762

發布評論請先 登錄

相關推薦

高速設計與PCB仿真流程

請教關于利用simulink進行脈沖反射法仿真研究的問題

信號反射的幾個基本問題分析

【轉載】Allegro SI 高速信號完整性仿真連載之三(附詳細流程)

如何讓信號反射仿真分析更加便捷高效?

避雷!高速信號和高速PCB理解誤區

千兆SFP光信號收發卡高速電路PCB仿真設計

高速電路信號完整性分析與設計|—高速信號的反射分析

基于Hyperlynx的反射仿真與分析

如何使用SigXplorer進行高速信號反射仿真

如何使用SigXplorer進行高速信號反射仿真

評論