當人工智能 (AI) 下沉到各式各樣的應用當中,作為市場上最大量的物聯網設備也將被賦予智能性。Arm Helium 技術正是為基于Arm Cortex-M 處理器的設備帶來關鍵機器學習與數字信號處理的性能提升。

本周起,小編將為您送上 Helium 技術系列文章,為您深入解析 Arm 的這一矢量處理技術及其優勢。今天,我們將介紹 Helium 品牌名的由來以及“節拍式”執行。若您想要了解如何高效利用 Helium,千萬別錯過文末視頻,通過 Arm 技術專家的實例演示,詳解 Helium 如何為端點設備引入更多智能。

Arm Helium 技術誕生的由來

為何不直接采用 Neon?

作者:Arm 架構與技術部 M 系列首席架構師兼研究員 Thomas Grocutt

經過 Arm 研究團隊多年的不懈努力,Arm 于 2019 年推出了適用于 Armv8?M 架構的 Arm Cortex-M 矢量擴展技術 (MVE)——Arm Helium 技術。起初,當我們面臨 Cortex?M 處理器的數字信號處理 (DSP) 性能亟待提升的需求時,我們首先想到的是采用現有的 Neon 技術。然而,面對典型的 Cortex?M 應用的面積限制條件下又需要支持多個性能的需求,意味著我們仍需從頭開始。作為一種較輕的惰性氣體,以氦氣 (Helium) 作為研究項目的名稱似乎再合適不過了。該研究項目主要針對中端處理器,旨在實現數據路徑寬度增加兩倍的情況下將性能提高四倍,而這正與氦氣的原子量 (4) 和原子序數 (2) 不謀而合。最終,在許多數字信號處理 (DSP) 和機器學習 (ML) 內核上,我們成功地實現了提升四倍的目標。毋庸置疑,“Helium” 已經深入人心,成為 Cortex-M 處理器系列 MVE 的品牌名。

要想打造具備良好 DSP 性能的處理器,主要關鍵在于可為其提供足夠的數據處理帶寬。在 Cortex?A 處理器上,128 位 Neon 負載可以輕松地從數據緩存中直接提取。但是,Cortex?M 處理器通常沒有緩存,而是使用低延遲靜態隨機存取存儲器 (SRAM) 作為主內存。對于許多系統來說,無法將 SRAM 路徑(通常只有 32 位)拓寬到 128 位,因此導致面臨內存操作停滯長達四個周期的可能性。同樣,乘加 (MAC) 指令中使用的乘法器需要很大的面積,在小型 Cortex?M 處理器上使用四個 32 位乘法器是不切實際的。就面積限制層面而言,最小的 Cortex-M 處理器與能夠亂序執行指令且功能強大的 Cortex?A 處理器的大小可能相差幾個數量級。因此,在創建 M 系列架構時,我們必須認真考慮充分利用每一個 gate。為了充分利用現有硬件,我們需要確保高成本資源(如通往內存的連接和乘法器)在每個周期都保持同時繁忙的狀態。在高性能處理器(如 Cortex?M7)上,可以通過矢量 MAC 雙發射來達成這一目標。此外,還有一個重要的目標,即在一系列不同的產品上提高 DSP 性能,而不僅局限于高端產品上。想要解決以上這些問題,需要借鑒參考幾十年前的矢量鏈理念中的一些技術。

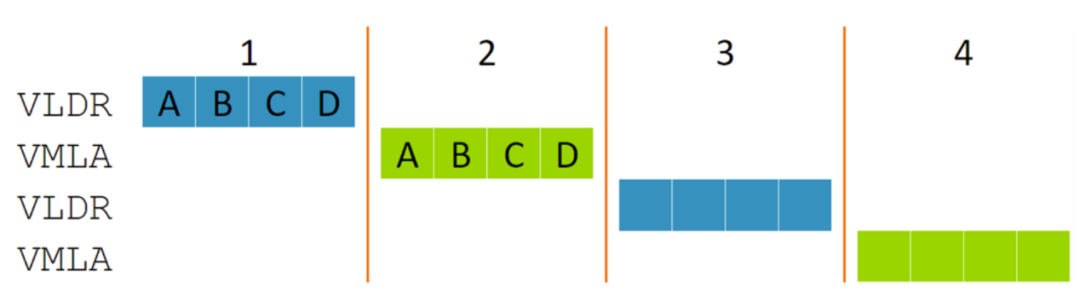

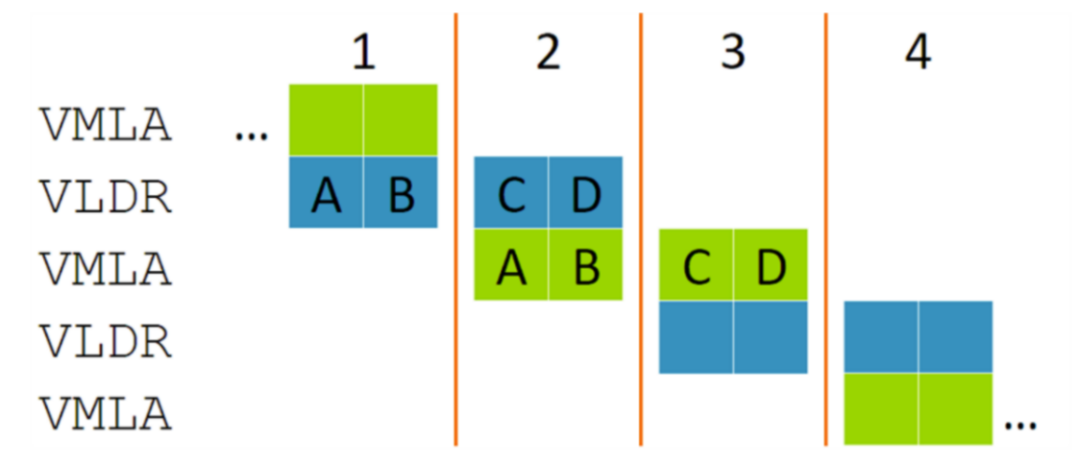

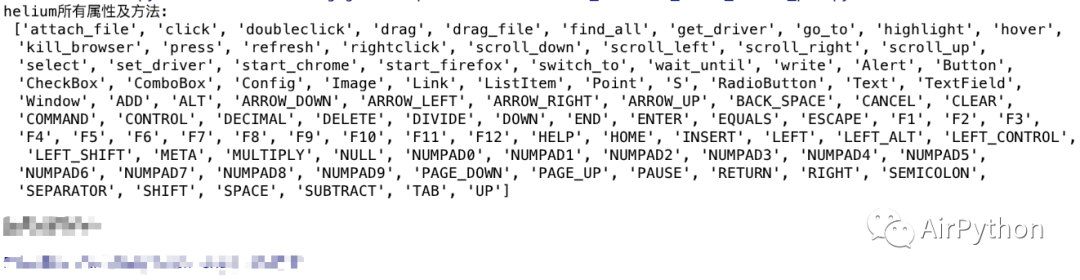

上圖顯示了在四個時鐘周期內交替執行的矢量負載 (VLDR) 和矢量 MAC (VMLA) 指令序列。這需要 128 位寬的內存帶寬和四個 MAC 塊,并且它們有一半時間處于空閑狀態。可以看到,每條 128 位寬的指令被分成大小相等的四個片段,MVE 架構稱之為“節拍”(標為 A 至 D)。無論元素大小如何,這些節拍始終是 32 位計算值,因此一個節拍可以包含一個 32 位 MAC,或四個 8 位 MAC。由于負載和 MAC 硬件是分開的,這些節拍的執行可以重疊,如下圖所示。

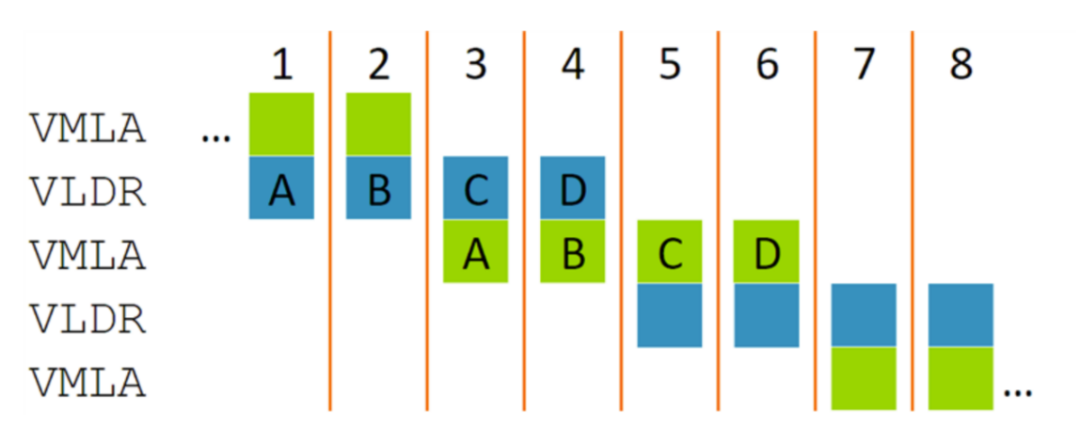

即使 VLDR 加載的值被隨后的 VMLA 使用,指令仍可以重疊。這是因為 VMLA 的節拍 A 只依賴于上一個周期發生的 VLDR 的節拍 A,因此節拍 A 和 B 與節拍 C 和 D 便會自然重疊。在這個例子中,我們可以獲得與 128 位數據帶寬處理器相同的性能,但硬件數量只有后者的一半。“節拍式”執行的概念可以高效地實施多個性能點。例如,下圖顯示了只有 32 位數據帶寬的處理器如何處理相同的指令。這一點充滿吸引力,因為它能使單發射標量處理器的性能翻倍(在八個周期內對八個 32 位值加載和執行 MAC),但卻沒有雙發射標量指令那樣的面積和功耗需求。

MVE 支持擴展到每周期四拍的實現方式,此時節拍式執行將簡化為更傳統的 SIMD 方法。這有助于在高性能處理器上保持可控的實現復雜度。

節拍式執行聽起來很不錯,但也會給架構的其他部分帶來一些值得關注的挑戰。

由于多條部分執行的指令可以同時運行,因此中斷和故障處理可能會變得相當復雜。例如,如果上圖中 VLDR 的節拍 D 出現故障,通常情況下,實施必須回滾 VMLA 的節拍 A 在上一周期對寄存器文件的寫入。我們的理念是讓每個 gate 都物盡其用,而在回滾的情況下緩沖舊數據值與這一理念相悖。為了避免這種情況,處理器會針對異常情況存儲一個特殊的 ECI 值,用于指示已經執行了后續指令的哪些節拍。在異常返回時,處理器便以此來確定要跳過哪些節拍。能夠快速跳出指令而無需回滾或等待指令完成,基于此保持 Cortex-M 具備的快速和確定性中斷處理能力。

如果指令會跨越節拍邊界,我們又會遇到時間跨越問題。這種交叉行為通常出現在拓寬/縮窄運算中。Neon 架構中的 VMLAL 指令就是一個典型的例子,它可以將 32 位值矢量乘加到 64 位累加器中。遺憾的是,為了保持乘法器輸出的完整范圍,通常需要進行這類拓寬運算。MVE 使用通用的 “R” 寄存器文件來處理累加器,從而解決了這一問題。此外,這樣還減少了對矢量寄存器的寄存壓力,使 MVE 只需使用 Neon 架構中一半的矢量寄存器就能獲得良好的性能。在矢量架構中,通常不會像 MVE 一樣廣泛使用通用的寄存器文件,因為寄存器文件往往與矢量單元相距甚遠。在亂序執行指令的高性能處理器上尤為如此,因為物理距離過大會限制性能。不過,正因如此,我們恰恰能夠將典型 Cortex?M 處理器的較小規模特性轉化為我們的優勢。

為確保重疊執行達到良好的平衡且無停滯,每條指令都應嚴格描述 128 位的工作,不能多也不能少。由此也會帶來一些挑戰。

憑借研究員們辛勤不懈的努力,以及充分參考架構書籍中所涉的所有內容,MVE 成功地將一些非常苛刻的功耗、面積和中斷延遲限制轉化為優勢。

您是否想要更深入了解 Helium 技術?由 Arm 物聯網事業部技術管理總監 Mark Quartermain 與 Arm 物聯網事業部嵌入式工具集成高級經理 Matthias Hertel 共同為大家錄制了 Helium 技術視頻,通過實例演示詳解如何高效利用 Helium。

我們將在下一篇 Helium 技術文章中深入探討一些復雜而又有趣的交錯加載/存儲指令。持續關注 Helium 技術講堂,我們下期再見!

審核編輯:湯梓紅

-

處理器

+關注

關注

68文章

19407瀏覽量

231180 -

ARM

+關注

關注

134文章

9165瀏覽量

369185 -

Cortex

+關注

關注

2文章

203瀏覽量

46599 -

人工智能

+關注

關注

1796文章

47666瀏覽量

240276 -

Helium

+關注

關注

0文章

12瀏覽量

4837

原文標題:Helium 技術講堂 | 為何不直接采用 Neon?

文章出處:【微信號:Arm社區,微信公眾號:Arm社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

IAR Systems率先支持集成AI技術的Arm Cortex-M55 內核

Arm Helium技術手冊

Arm宣布推出基于M-Profile Vector Extension (MVE)矢量擴充方案的Arm Helium技術

晶體管誕生的由來是什么

Cortex-M55的單片機AI技術Helium權威指南電子書發布(2020-09-08)

使用Helium開發工具包和Cayenne進行GPS跟蹤

什么是Arm Helium矢量處理技術?

Helium 是什么?優缺點有哪些?

Arm Helium技術誕生的由來 為何不直接采用Neon?

Arm Helium技術誕生的由來

Arm Helium技術誕生的由來

評論