DDS簡介:

DDS 同 DSP(數字信號處理)一樣,是一項關鍵的數字化技術。DDS 是直接數字式頻率合成器(Direct Digital Synthesizer)的英文縮寫。與傳統的頻率合成器相比,DDS 具有低成本、低功耗、高分辨率和快速轉換時間等優點,廣泛使用在電信與電子儀器領域,是實現設備全數字化的一個關鍵技術。

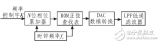

DDS 芯片的功能主要包括頻率控制寄存器、高速相位累加器和正弦計算器三個部分。頻率控制寄存器可以串行或并行的方式裝載并寄存用戶輸入的頻率控制碼;而相位累加器根據頻率控制碼在每個時鐘周期內進行相位累加,得到一個相位值;正弦計算器則對該相位值計算數字化正弦波幅度(芯片一般通過查表得到)。

DDS 芯片輸出的一般是數字化的正弦波,因此還需經過高速 D/A 轉換器和低通濾波器才能得到一個可用的模擬頻率信號。關于想了解更多的 DDS 的相關知識, 大家可以到百度直接搜索。

下面主要來給大家介紹FPGA 程序的設計, DDS IP 的配置和調試。

編寫 dds_wave 的 verilog 程序

`timescale1ns/1ps ////////////////////////////////////////////////////////////////////////////////// //Company: //Engineer: // //CreateDate:103307/17/2018 //DesignName: //ModuleName:dds_wave //ProjectName: //TargetDevices: //Toolversions: //Description: // //Dependencies: // //Revision: //Revision0.01-FileCreated //AdditionalComments: // ////////////////////////////////////////////////////////////////////////////////// moduledds_wave(clk,key1,data,da_clk ); inputclk,key1; output[7:0]data; outputda_clk; reg[15:0]key1_cout; reg[7:0]data_o; regdds_we; reg[28:0]dds_data; reg[3:0]dds_freq=0; regdds_we_req; wire[7:0]sine; assignsine_reg=sine[6:0]; assignda_clk=clk; assigndata=data_o; //有符號數轉化為無符號輸出到DA always@(posedgeclk) begin if(sine[7]==1'b1) data_o<=?sine?-?128; ?else ??data_o?<=?sine?+?128; end //控制DDS輸出不同 always?@(negedge?clk) begin ?dds_we?<=?dds_we_req; ?case(dds_freq) ?4'd0: ??dds_data?<=?29'd107;??//10Hz:(dds_data*2^29/50*1000000) ?4'd1: ??dds_data?<=?29'd1074;?//100Hz:(dds_data*2^29/50*1000000) ?4'd2: ??dds_data?<=?29'd10737;?//1kHz:(dds_data*2^29/50*1000000) ?4'd3: ??dds_data?<=?29'd53687;?//5kHz:(dds_data*2^29/50*1000000) ?4'd4: ??dds_data?<=?29'd107374;?//10kHz:(dds_data*2^29/50*1000000) ?4'd5: ??dds_data?<=?29'd536871;?//50kHz:(dds_data*2^29/50*1000000) ?4'd6: ??dds_data?<=?29'd1073742;?//100Hz:(dds_data*2^29/50*1000000) ?4'd7: ??dds_data?<=?29'd5368709;?//500Hz:(dds_data*2^29/50*1000000) ?4'd8: ??dds_data?<=?29'd10737418;?//1mHz:(dds_data*2^29/50*1000000)?? ?4'd9: ??dds_data?<=?29'd21474836;?//2mHz:(dds_data*2^29/50*1000000) ?4'd10: ??dds_data?<=?29'd32212255;?//3mHz:(dds_data*2^29/50*1000000) ?4'd11: ??dds_data?<=?29'd42949672;?//4mHz:(dds_data*2^29/50*1000000) ?4'd12: ??dds_data?<=?29'd53687091;?//5mHz:(dds_data*2^29/50*1000000) ?4'd13: ??dds_data?<=?29'd64424509;?//6mHz:(dds_data*2^29/50*1000000) ?4'd14: ??dds_data?<=?29'd75161928;?//7mHz:(dds_data*2^29/50*1000000) ?4'd15: ??dds_data?<=?29'd85899346;?//8mHz:(dds_data*2^29/50*1000000) ?default: ??dds_data?<=?29'd107;?//?1kHz:(dds_data*2^29/50*1000000) ?endcase end ? //按鈕處理程序,改變DDS的輸出頻率 always?@(posedge?clk) begin ?if(key1?==?1'b0) ??key1_cout?<=?0; ?else?if((key1?==?1'b1)?&?(key1_cout?<=?16'hc350)) ??key1_cout?<=?key1_cout?+?1'b1; ? ?if(key1_cout?==?16'hc349) ?begin ??dds_freq?<=dds_freq?+?1'b1; ??dds_we_req?<=?1'b1; ?end ?else?begin ??dds_freq?<=dds_freq; ??dds_we_req?<=?1'b0; ?end end? ? //DDS?IP產生sin/cos波形 sin_cos?sin_cos_inst( ?.clk(clk), ?.we(dds_we), ?.data(dds_data), ?.cosine(cosine), ?.sine(sine), ?.phase_out() ); ? endmodule

程序通過檢測開發板上按鍵 KEY1 ,如果按鍵 KEY1 每按下一次,寄存器 dds_freq 的值就會加 1, 程序就會對 DDS IP 寫入一個 data 數據來改變相位的增加量,從而改變輸出波形的頻率。程序中設置了 16 種相位的增加量,所以可以讓 DDS 產生 16 個不同頻率的正弦波。在本實驗的 DDS IP 的配置中,相位增加的數據寬度為 29 位,所以最小的頻率輸出為50Mhz/2^29, 約 0.093Hz。如果想讓 DDS 輸出 1Khz 的波形,就需要寫入相位增加值10737 。相位增加值和頻率的計算公式如下:

相位增加值=( fhz * 2^29 )/( 50 * 1000000)

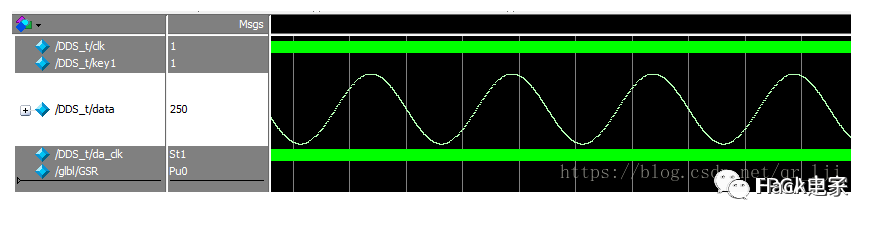

仿真圖如下:

審核編輯:湯梓紅

-

合成器

+關注

關注

0文章

273瀏覽量

25445 -

正弦波發生器

+關注

關注

1文章

26瀏覽量

15703 -

Verilog

+關注

關注

28文章

1351瀏覽量

110389 -

DDS

+關注

關注

21文章

636瀏覽量

152931

原文標題:Verilog實現DDS 正弦波發生器

文章出處:【微信號:ZYNQ,微信公眾號:ZYNQ】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于DDS技術的高頻正弦波發生器的設計

基于DDS技術的高頻正弦波發生器的設計

基于Verilog實現的DDS任意波形發生器

Verilog實現DDS正弦波發生器

Verilog實現DDS正弦波發生器

評論