大型芯片制造商專注于芯粒,將其視為將更多功能集成到電子設備中的最佳途徑。現(xiàn)在的挑戰(zhàn)是如何拉動芯片行業(yè)的其他部分,為第三方芯粒創(chuàng)建一個市場,可以使用特定標準從菜單中進行選擇,這些標準可以加快上市時間,幫助控制成本,并讓其他芯片和內(nèi)部開發(fā)的芯粒一樣可靠地運行。。

到目前為止,第三方chiplet的使用情況參差不齊。普遍的共識是,第三方芯粒市場將在某個時候蓬勃發(fā)展,部分原因是購買芯粒比構建它們更便宜,前提是有足夠的互操作性標準。最大的未知數(shù)是,與內(nèi)部開發(fā)的芯粒相比,這些芯粒的性能如何,這反過來又會影響采用的速度、可用的市場機會總量以及隨后的市場整合速度。這是由于幾個變量造成的:

1、據(jù)估計,所有新啟動的芯片設計中有 30% 至 35% 供大型系統(tǒng)公司內(nèi)部使用。因此,這些公司不是使用現(xiàn)成的處理器和 IP,而是從頭開始設計系統(tǒng)來優(yōu)化其內(nèi)部流程或數(shù)據(jù)類型。為這些應用開發(fā)的一些芯粒是高度專業(yè)化且具有競爭力的秘密武器,但這些系統(tǒng)中還有許多其他功能可以由第三方芯粒開發(fā)商開發(fā)。

2、小型聯(lián)盟正在圍繞不同領域形成,例如生物或汽車應用。其中一些涉及代工廠和 OSAT,它們開始為本質上是裝配設計套件制定標準,而另一些則正在有機開發(fā)。但在所有情況下,重點都是基于芯粒設計的大規(guī)模生產(chǎn),并具有可預測的產(chǎn)量。

3、與必須符合特定工藝技術的軟IP不同,芯粒可以在任何工藝節(jié)點上開發(fā)。它們是否可以從一家晶圓廠互換到另一家晶圓廠還有待觀察。然而,混合和匹配流程節(jié)點的能力為更多選擇打開了大門。例如,開發(fā)人員可以在任何工作效果最好的節(jié)點上創(chuàng)建完全模擬的芯粒,而不是最先進節(jié)點的平面 SoC 所需的大部分數(shù)字芯片和一些模擬芯片。這開辟了一個基于 PPAC 的全新潛在市場。

芯粒代表了摩爾定律誕生以來最根本的轉變之一。這個想法已經(jīng)存在了數(shù)十年,但在 finFET 推出之前,平面微縮的好處始終超過了改造供應鏈、設計和制造工藝、更新或添加新設備以及因故障而造成的中斷所帶來的巨大挑戰(zhàn)。所有這些仍然是一個巨大的挑戰(zhàn),也是難以預測變化速度的主要原因之一。

AMD、英特爾和 Marvell 等大型芯片制造商已經(jīng)證明芯粒的有效性,并且他們正在從其開創(chuàng)性工作中獲益。但如果歷史可以說明事情將如何演變,那么這些公司自己開發(fā)所有本質上是硬化的知識產(chǎn)權在經(jīng)濟上并不有利。這是他們支持新的互操作性標準(尤其是 UCIe)并推廣商業(yè)市場理念的原因之一。此外,各個政府機構還制定了利用現(xiàn)成的商用芯粒作為加快上市時間并最終降低成本的一種方式的目標。

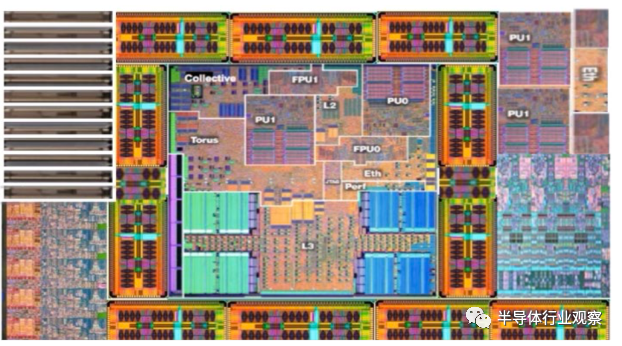

圖 1:NIST 的芯粒架構。

盡管如此,正如這些初始實現(xiàn)所證明的那樣,集成芯粒和組裝它們比聽起來要困難得多。大型芯片制造商通過構建芯粒的底盤來實現(xiàn)這一目標。這允許在特定參數(shù)內(nèi)設計芯粒,例如面積、噪聲(電磁、功率、基板等)、互連位置、材料相互作用和許多其他特性。但他們也使用一組對他們的設計很重要的狹窄參數(shù)來解決問題。

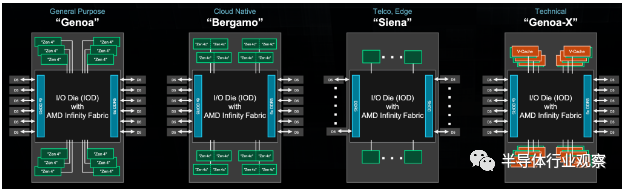

圖 2:AMD 的 EPYC Gen 4 處理器使用芯粒來實現(xiàn)不同應用的可擴展性。

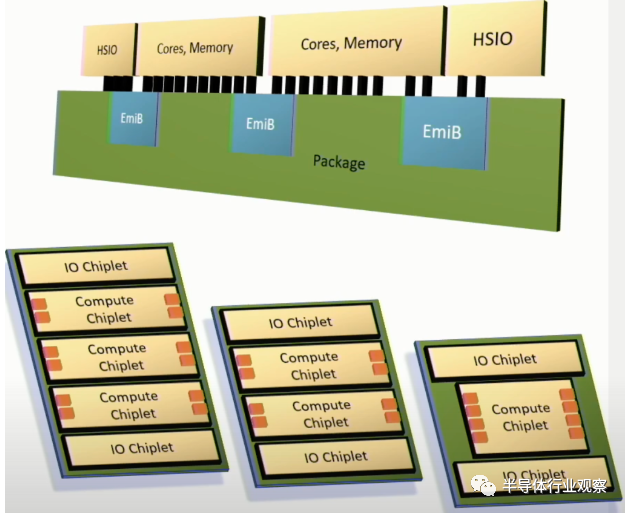

英特爾的芯粒方法類似。(參見下圖 3)

圖 3:英特爾基于計算芯粒及其多芯片互連橋 (EMIB) 的可擴展至強架構

“即使你有一套能夠很好地協(xié)同工作的芯粒的指南,您仍然會遇到各種工藝變化、封裝變化等等,”Advantest America的美國應用研究副總裁 Ira Leventhal 說道。“您可以提供芯片匹配和支持左移等功能,以便更快地發(fā)現(xiàn)缺陷,這樣就不會產(chǎn)生大量的封裝成本和廢料。但在這個更復雜的環(huán)境中,如何優(yōu)化良率?這確實很重要,即使您有一組可以一起發(fā)揮作用的最佳事物。需要在各個步驟中采取更多行動才能完成這一任務。”

芯粒還被高度針對性地用于其他設計,OSAT將它們集成到高級封裝中。在這些情況下,它們的使用方式類似于強化 IP,而不是作為基于芯粒設計的一部分。

“我們看到我們的客戶使用芯粒進行高性能計算以及網(wǎng)絡交換機,”ASE 高級工程總監(jiān)Ou Li,在最近的 CHIPCon 小組會議上。“他們關心性能和信號完整性。例如,您可以使用光纖 I/O 來替代高速 SerDes。因此,現(xiàn)在芯粒正在多個市場和多種應用中使用,并且未來的采用率將會越來越高。”

對于商業(yè)市場,關于芯粒如何準確表征的標準仍在制定中。盡管如此,這種方法還是有一些明顯的優(yōu)點。由于芯粒比光罩尺寸的 SoC 更小,因此良率通常更高。真正的集成挑戰(zhàn)來自芯粒的外部。還存在一些挑戰(zhàn),包括如何在組裝后單獨測試和檢查它們,以及如何測量芯片移位等內(nèi)容。例如,特定用例的動態(tài)功率密度可能會因電阻和靜態(tài)漏電流而增加熱量。這反過來會導致翹曲,從而對將芯粒固定到位的鍵產(chǎn)生壓力。處理所有這些問題需要新的流程來在設計周期的早期解決這些問題,以及新的設備和全新的工藝步驟。

芯粒的優(yōu)勢

使用芯粒有三個主要原因。首先,無論工藝節(jié)點如何,它們都可以混合搭配,這大大降低了開發(fā)半導體器件的成本。

“隨著這些特定領域的架構越來越專業(yè)化,如果它真正推動我們?yōu)槊糠N架構采用差異化技術,它有可能對晶圓廠、設備制造商和其他行業(yè)產(chǎn)生巨大的顛覆性影響。Lam Research 計算產(chǎn)品副總裁 David Fried 在 SEMI 最近關于計算未來的小組討論中說道。“如果你回顧 15 到 20 年前,當單片集成節(jié)點一個接一個地緩慢前進時,我們將異構集成所需的一些制程創(chuàng)新視為附加的,并且有點痛苦,這就是為什么我們繼續(xù)前進。但現(xiàn)在,如果你看看到達下一個節(jié)點的成本,特別是單片集成的成本,那么突然間這些異構集成過程看起來真的很便宜。”

其次,芯粒可以換入或換出設計,以針對特定領域和應用進行定制。這使得芯片制造商能夠創(chuàng)建高度針對特定應用的設計,為更特定的領域和用例定制類似的芯片,無需從頭開始重新創(chuàng)建所有內(nèi)容即可更新它們,并添加比單個芯片上可用的更多功能否則將受到十字線尺寸的限制。

英特爾硅架構工程師斯瓦德什·喬德里 (Swadesh Chaudry) 表示:“當我們期待擁有不同的技術節(jié)點時,我們可以將它們混合搭配在一起,并將一些模擬內(nèi)容保留在比最新技術更穩(wěn)定的技術中。” CHIPCon 2023 小組討論。“您可以將不同的加速器與相同的計算引擎集成,并可能通過針對不同應用程序的定制包加快上市時間。通過封裝中的芯粒,您可以更輕松地做到這一點。”

芯粒的第三個主要好處是,即使是首次設計,它們也可以下注加快上市時間,從而使芯片制造商能夠更快地進入市場。

“歸根結底,問題在于 PPA 和上市時間”,Amkor Technology芯粒/FCBGA 集成副總裁 Mike Kelly 說道。“這從高端開始。數(shù)據(jù)中心的人員首先推動了它,也許也是最困難的。但它正在滲透到我們今天看到的幾乎所有計算類別。它肯定在數(shù)據(jù)中心。它也出現(xiàn)在個人電腦市場和手機市場。汽車正變得計算密集型,并面臨著與其他汽車相同的限制。現(xiàn)代節(jié)點價格昂貴,晶圓成本也很高。您可以通過分解真正高性能的部分來實現(xiàn)這一點。這是否變得無處不在?嗯,這是一條很長的S曲線。但它肯定會過渡到新的地方。”

并且有充分的理由。Synopsys首席戰(zhàn)略官 Antonio Varas 指出,目前只有約 35% 的芯片設計項目按計劃進行,約 25% 的項目首次實現(xiàn)硅成功。與此同時,需求每年增加 9% 至 11%,而供應則增加 7% 至 9%。到 2030 年,需求預計將增長 17%,這主要是因為半導體被用于各種新市場和新應用。

挑戰(zhàn)

這就是芯粒發(fā)揮作用的地方。但要使這一切順利進行,需要在各個層面制定標準——而這只是一個開始。

“你肯定需要標準,”臺積電現(xiàn)場技術解決方案副總裁 Paul Rousseau 說。“這就是 3DFabric 和 3Dblox 背后的整個理念,并且有多個層次。其中一個級別是 EDA 端或 I/O,UCIe 正在成為芯片間通信的標準。除非有巨大的好處,否則為什么要使用不同類型的 I/O?另一件事是在硅本身或封裝上。我們肯定有一些我們知道可以使用的信封。挑戰(zhàn)之一是每個人都有一個奇特的想法。“這將是自sliced bread以來最好的東西。”但這需要大量的開發(fā)時間才能證明。因此,我們正在努力讓人們采用標準解決方案。這就是我們對硅所做的事情。我們有我們知道可以發(fā)揮作用的設計規(guī)則和模型。封裝也有同樣的目標。這并不是每次都重新發(fā)明輪子。”

最初,這意味著商用芯粒的選擇更加有限。但這是否意味著不太優(yōu)化的設計更難確定,因為將 SoC 分解為不同的強化功能可以讓設計團隊更輕松地確定這些功能的優(yōu)先級并劃分設計。如果各種芯粒如何組合在一起以及如何測試它們都有標準,那么隨著時間的推移,它們也可能比一次性設計更可靠。

“必須有人將所有這些整合在一起,進行我所說的高級設計,不僅集成芯粒,還集成您正在使用的任何互連、基板或中介層技術,” Promex Industries 總裁兼首席執(zhí)行官迪克·奧特 (Dick Otte) 說道。

芯片設計的重大變化之一是關注數(shù)據(jù)如何在芯片中移動,隨著需要處理的數(shù)據(jù)量持續(xù)增長,這一點非常重要。這引發(fā)了一系列變化,例如新材料和不同的設備組裝方式。混合鍵合是人們高度關注的領域之一,而且在行業(yè)活動中幾乎總是會引發(fā)問題。由于需要比標準互連允許的速度更快地傳輸視頻和大圖像,因此該技術首先在圖像傳感器中實現(xiàn)。例如,UMC 于 2023 年 2 月與 Cadence 簽署了一項協(xié)議,提供一個可以加速這一過程的平臺,特別是對于成熟節(jié)點,這是許多芯粒將被開發(fā)的地方。

例如,當今一些最快的計算機使用諸如市售 Arm 內(nèi)核之類的組件。關鍵在于數(shù)據(jù)路徑和與內(nèi)存的物理連接、硬件-軟件協(xié)同設計以及 AI/ML 的稀疏算法。隨著計算變得更加分散,例如汽車和便攜式設備與智能城市基礎設施進行通信,真正的價值可能不再在于誰創(chuàng)造了最快的處理器,而更多地在于無縫連接。

更大的挑戰(zhàn)可能在業(yè)務方面。“問題是這是否會轉化為商業(yè)芯粒市場,您可以從第三方以低廉的價格采購它并將其集成到您的設計中,”Varas 說。“您需要的不僅僅是標準接口。這里有一個商業(yè)模式的問題。如何鑒定芯粒的資格?你如何測試它們?所以標準接口將會出現(xiàn)。但第二部分并不像IP模型的演變那么簡單。情況要復雜得多。這項技術可能是可行的,但它還包括商業(yè)模式、供應鏈協(xié)調等等。”

此外,商業(yè)芯粒還存在數(shù)據(jù)共享的問題。大型芯片制造商的一大優(yōu)勢是能夠在公司內(nèi)部共享數(shù)據(jù),以便可以針對最終應用或用例優(yōu)化芯粒。不同公司之間交換數(shù)據(jù)要困難得多,因為公司非常擔心數(shù)據(jù)泄露或被盜。

“有數(shù)據(jù)安全,也有數(shù)據(jù)共享,”Lam的Fried說。“這些并不相互排斥,人們必須消化這一點。我們開始打破使用云來完成,我們害怕使用云的事情的障礙。我們正在努力解決的是數(shù)據(jù)共享以獲得更高的價值。飛機就是一個例子。這些飛機的所有者與飛機發(fā)動機制造商共享數(shù)字孿生和數(shù)字線程的維護記錄和數(shù)據(jù),并且他們可以對故障進行建模并進行預測性維護。航空航天行業(yè)的一些公司正在與所有這些不同的公司共享其產(chǎn)品的私密數(shù)據(jù),這對所有這些公司都有好處。這種情況在我們的行業(yè)中并沒有發(fā)生太多。這種情況發(fā)生在銀行業(yè),比如當你刷信用卡時,它會立即檢查是否存在欺詐行為。這些模型建立在來自多個不同銀行的數(shù)據(jù)之上,并且全部聯(lián)合在一起。這就是我們作為一個行業(yè)失敗的地方,因為我們在整個生態(tài)系統(tǒng)的數(shù)據(jù)共享方面落后于銀行業(yè)和航空航天業(yè) 10 年。”

系統(tǒng)與芯片

設計方面還存在其他挑戰(zhàn)。將芯粒集成到封裝中使設計問題遠遠超出了單個芯片的范圍。現(xiàn)在它是需要協(xié)同工作的芯片的集合,并且不再由單個團隊在一個地點開發(fā)。

“我們已經(jīng)從設計芯片轉向設計系統(tǒng),”Synopsys 的 Varas 說。“我們正在處理三個主要問題。我們有新的復雜性向量,這需要系統(tǒng)設計的并行化。而且我們還缺乏人才。如今,60%的EDA用戶是經(jīng)典半導體公司。另外 40% 是超大規(guī)模企業(yè)、初創(chuàng)公司以及 ASIC 或 IP 供應商。2019 年至 2022 年間,先進芯片的設計啟動數(shù)量增加了 44%,但不斷擴大的生態(tài)系統(tǒng)也加劇了碎片化。有更多的選擇和復雜性,這增加了設計的破壞性。”

日月光的Li對此表示同意。“設計師需要采取與過去不同的做法,過去以 PCB 為中心,使用 GUI 為主的設計工具,”她說。“他們不需要設計扇出或有源中介層。因此,舊的封裝設計人員現(xiàn)在必須管理 LVS(布局與原理圖)、CRV(約束隨機驗證)測試的 IC 級工具,并可能運行一些 SIPO(串行輸入/并行輸出)分析。我們需要與客戶擁有相同的波長。此外,封裝變得越來越大,為了控制翹曲,需要材料和工藝技術的創(chuàng)新。我們需要擁有已知良好的芯片、已知良好的模塊,并且我們需要進行多次測試插入以確保每個過程都良好并且能夠產(chǎn)出。最后,組件級測試將不再通過,這就是我們采用和實施系統(tǒng)級測試的原因。”

結論

Chiplet 將在某個時候變得流行,因為根本沒有足夠的體積來支持縮芯粒上所有部件的成本,最終公司將專注于他們最擅長的事情——他們所謂的秘密武器——并讓其他人開發(fā)對競爭力或差異化沒有貢獻的組件他們的產(chǎn)品。

主要問題(至少在最初)與尋找將芯粒集成到設備中的標準方法有關,確保它們隨著時間的推移按預期工作,以及如何共享數(shù)據(jù)以便行業(yè)能夠快速發(fā)展。其中包括業(yè)務和技術問題,而且數(shù)量很多。盡管大型芯片制造商基本上都是單打獨斗,但隨著成本受到嚴格審查以及競爭為某些零部件創(chuàng)造了公平的競爭環(huán)境,這種情況將會發(fā)生變化。但所有這些因素變化的速度以及提供競爭優(yōu)勢的因素將因市場、公司以及整個行業(yè)出現(xiàn)的技術、商業(yè)和地緣政治的新發(fā)展而異。

Chiplet 的方向是明確的。有足夠的力量在推動它。但在短期內(nèi),甚至可能更長時間內(nèi),時機、獨特的挑戰(zhàn)和生態(tài)系統(tǒng)合作仍將更加難以應對。

-

封裝

+關注

關注

127文章

7992瀏覽量

143404 -

芯片設計

+關注

關注

15文章

1028瀏覽量

55006 -

chiplet

+關注

關注

6文章

434瀏覽量

12631

原文標題:Chiplet,困難重重

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

解鎖Chiplet潛力:封裝技術是關鍵

對話郝沁汾:牽頭制定中國與IEEE Chiplet技術標準,終極目標“讓天下沒有難設計的芯片”

Cadence推出基于Arm的系統(tǒng)Chiplet

Chiplet技術有哪些優(yōu)勢

2035年Chiplet市場規(guī)模將超4110億美元

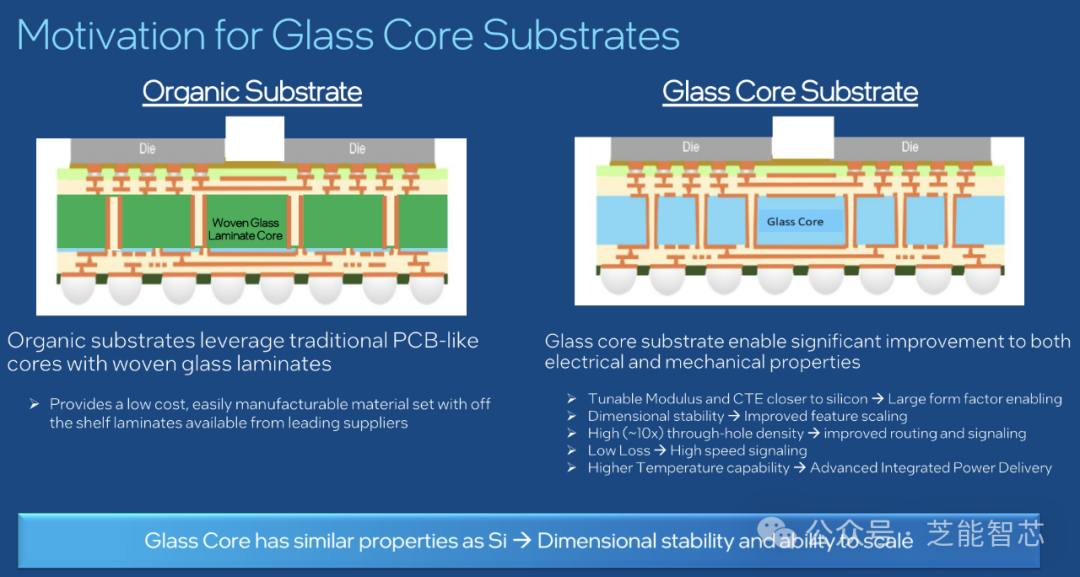

玻璃基板的技術優(yōu)勢有哪些

IMEC組建汽車Chiplet聯(lián)盟

Primemas選擇Achronix eFPGA技術用于Chiplet平臺

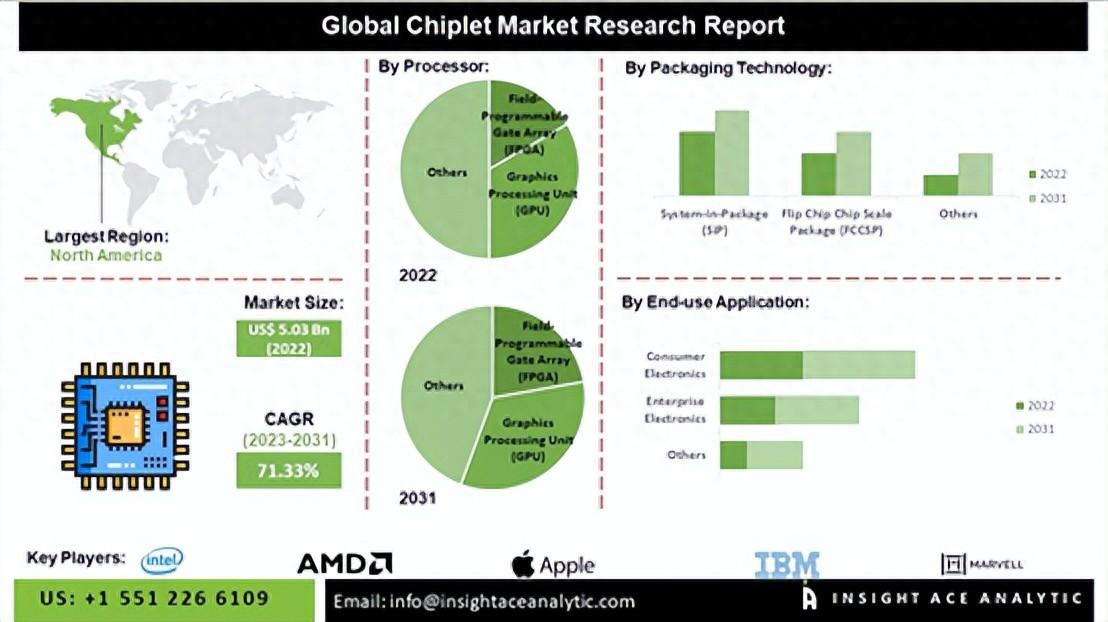

2031年全球Chiplet市場預測

創(chuàng)新型Chiplet異構集成模式,為不同場景提供低成本、高靈活解決方案

西門子EDA創(chuàng)新解決方案確保Chiplet設計的成功應用

蘋果縮小第三方瀏覽器引擎測試范圍

雷曼光電PM驅動+玻璃基技術助力Micro LED實現(xiàn)有效降本

前景一片大好的Chiplet,依然存在門檻問題

Chiplet是否也走上了集成競賽的道路?

Chiplet,困難重重

Chiplet,困難重重

評論