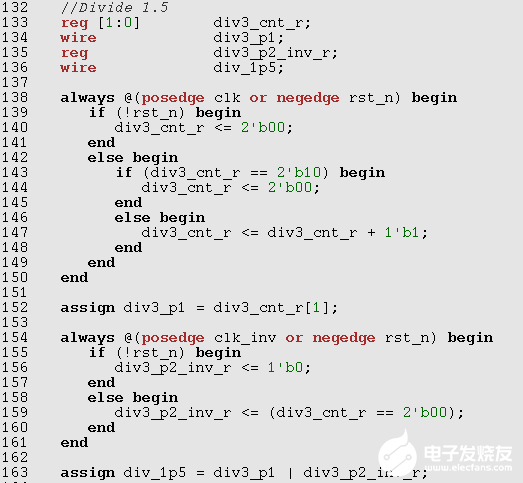

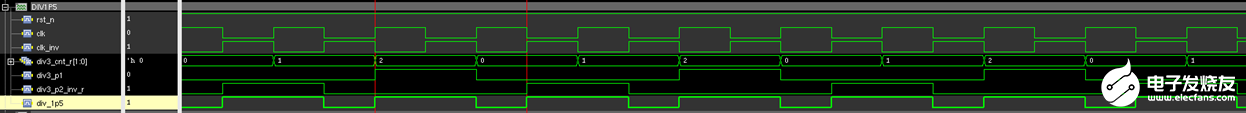

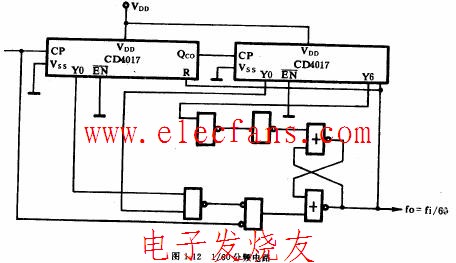

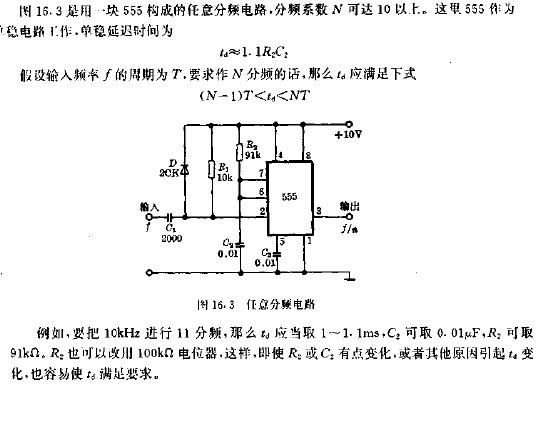

思路很簡(jiǎn)單,在3個(gè)周期里產(chǎn)生兩個(gè)脈沖,等效于分頻1.5。

第一個(gè)脈沖很容易實(shí)現(xiàn)。計(jì)數(shù)器2’b00 -- 2’b01 – 2’b10無(wú)限循環(huán),最高位就是每三個(gè)周期出現(xiàn)一次的脈沖。第二個(gè)脈沖要用到一個(gè)negedge DFF。兩個(gè)脈沖OR一下,輸出就是1.5分頻。

下面是Verilog RTL及波形。

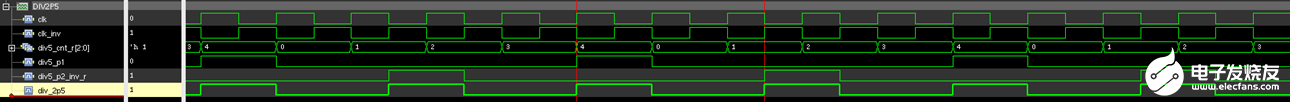

2.5分頻

一樣的思路,5個(gè)周期產(chǎn)生兩個(gè)脈沖就可以了。

其他x.5分頻可以按同樣的思路類推。

這種分頻后的輸出有幾個(gè)“缺陷“,使用的時(shí)候要注意。

-占空比無(wú)法做到50-50。

-分頻輸出有一點(diǎn)jitter。Jitter來(lái)自于兩個(gè)脈沖上升沿相對(duì)于原始時(shí)鐘的上升沿下降沿,delay是不一樣的。原始時(shí)鐘本身上升沿下降沿的jitter會(huì)疊加在上面。

要求不高的場(chǎng)合,這種數(shù)字邏輯實(shí)現(xiàn)的小數(shù)分頻輸出可以當(dāng)作時(shí)鐘用。Jitter要求高的場(chǎng)合,還是要用PLL實(shí)現(xiàn)。

審核編輯:黃飛

-

pll

+關(guān)注

關(guān)注

6文章

781瀏覽量

135333 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2261瀏覽量

94994 -

分頻

+關(guān)注

關(guān)注

0文章

241瀏覽量

24910 -

數(shù)字邏輯

+關(guān)注

關(guān)注

0文章

74瀏覽量

16701 -

數(shù)字前端

+關(guān)注

關(guān)注

0文章

9瀏覽量

7802

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

五分頻電路,四分頻電路

IC數(shù)字前端設(shè)計(jì)實(shí)戰(zhàn)案例系列pdf

尋找數(shù)字前端設(shè)計(jì)的講師

小白入門數(shù)字前端,求大神指教需要學(xué)什么知識(shí)以及用哪些軟件

如何去實(shí)現(xiàn)一種數(shù)字前端的設(shè)計(jì)?包括哪些步驟?

用VHDL語(yǔ)言實(shí)現(xiàn)3分頻電路

D觸發(fā)器實(shí)現(xiàn)二分頻電路(D觸發(fā)器構(gòu)成的2分頻電路)

用JK-FF觸發(fā)器實(shí)現(xiàn)的3分頻電路

軟件無(wú)線電中的數(shù)字前端

數(shù)字前端設(shè)計(jì)的x.5分頻實(shí)現(xiàn)思路

數(shù)字前端設(shè)計(jì)的x.5分頻實(shí)現(xiàn)思路

評(píng)論