本文介紹一個FPGA常用模塊:SRIO(SerialRapidIO)。SRIO協(xié)議是一種高速串行通信協(xié)議,在我參與的項目中主要是用于FPGA和DSP之間的高速通信。有關(guān)SRIO協(xié)議的詳細介紹網(wǎng)上有很多,本文主要簡單介紹一下SRIO IP核的使用和本工程的源代碼結(jié)構(gòu)。

由于Vivado中RapidIO IP核需要付費才能使用,因此本文提供完整工程源碼。文章末尾有該工程源碼獲取方式,有需要的小伙伴可以收藏、分享一下。

01

軟硬件平臺

軟件平臺:Vivado 2017.4;

硬件平臺:XC7K410T...;

02

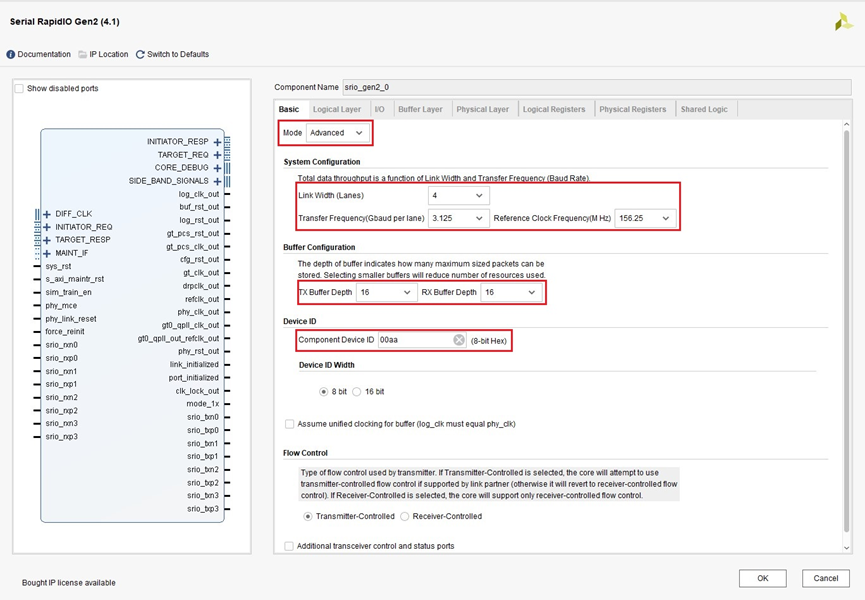

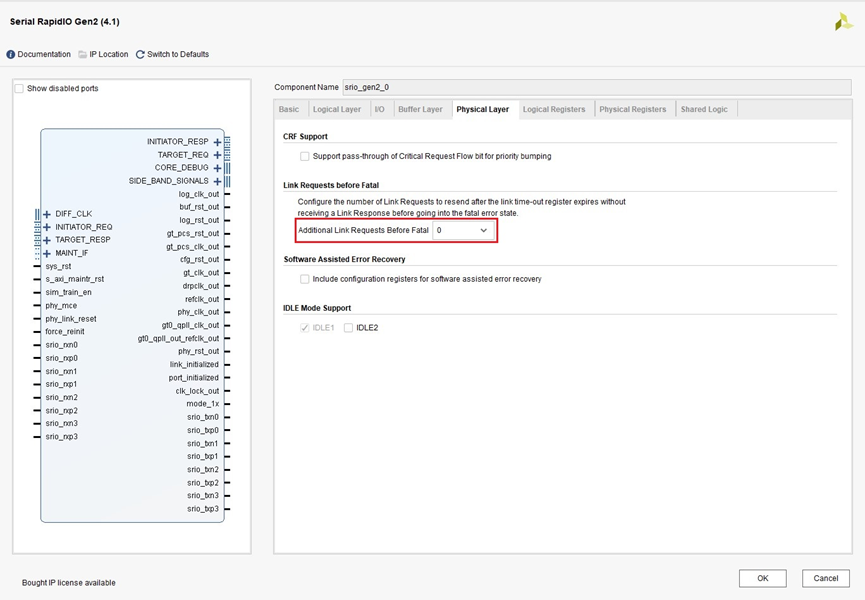

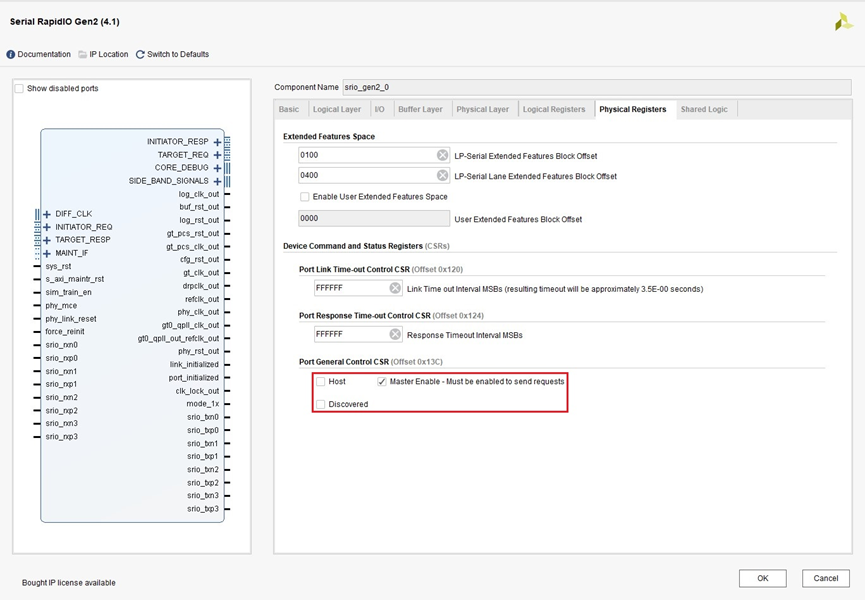

?IP核參數(shù)配置

本工程SRIO IP核參數(shù)配置如下圖所示,僅供參考:

03

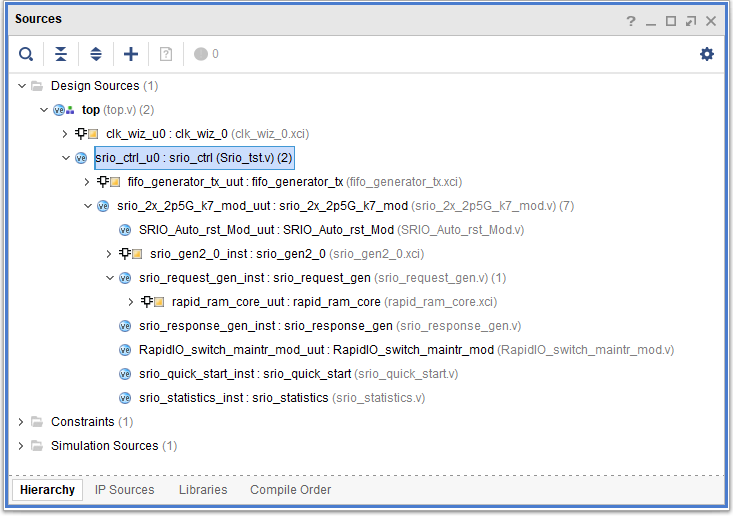

工程源碼結(jié)構(gòu)

下圖是SRIO工程源碼結(jié)構(gòu):

其中,

SRIO_Auto_rst_Mod:SRIO自動復位模塊;

srio_request_gen:SRIO請求事務生成模塊;

srio_response_gen:SRIO響應事務生成模塊;

RapidIO_switch_maintr_mod & srio_quick_start:SRIO維護事務生成模塊。

04

實現(xiàn)功能

該FPGA SRIO模塊采用NWRITE類型事務往DSP目的地址傳輸數(shù)據(jù),每包數(shù)據(jù)大小為256字節(jié)。數(shù)據(jù)寫入完畢后,通過DOORBELL事務給DSP發(fā)送數(shù)據(jù)接收中斷。另外FPGA端通過RapidIO IP核m_axis_treq接口接收來自DSP的數(shù)據(jù)。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605989 -

sRIO

+關(guān)注

關(guān)注

1文章

31瀏覽量

21062

原文標題:FPGA優(yōu)質(zhì)開源模塊 - SRIO

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

關(guān)于FPGA IP核

FPGA IP核的相關(guān)問題

采用EDA軟件和FPGA實現(xiàn)IP核保護技術(shù)

基于FPGA的IP核設計技術(shù)

FPGA實現(xiàn)基于Vivado的BRAM IP核的使用

SRIO IP核的三層協(xié)議的作用?

SRIO IP核的三層協(xié)議的作用解析

fpga ip核是什么 常用fpga芯片的型號

基于FPGA的SRIO協(xié)議設計

FPGA優(yōu)質(zhì)開源模塊-SRIO IP核的使用

FPGA優(yōu)質(zhì)開源模塊-SRIO IP核的使用

評論