1. NMOS 和 PMOS

MOSFET(金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管)或 IGFET(絕緣柵場(chǎng)效應(yīng)晶體管)是一種場(chǎng)效應(yīng)晶體管,它在柵極和主體之間利用絕緣體(如 SiO2)。如今,MOSFET 是數(shù)字和模擬電路中最常見(jiàn)的晶體管類型。

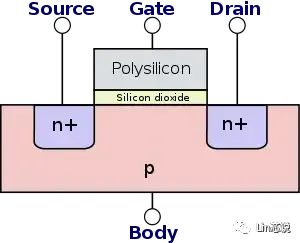

NMOS 和PMOS 的區(qū)別體現(xiàn)在其襯底和摻雜類型的不同,NMOS 的襯底為P型半導(dǎo)體,摻雜兩個(gè)高濃度的 N 型半導(dǎo)體,并用鋁金屬引出兩個(gè)電極分別為作為源極(Source)和漏極(Drain),并在半導(dǎo)體表面覆蓋一層很薄的 SiO2 作為絕緣層,在源極和漏極之間的絕緣層上添加一個(gè)多晶硅(Polysilicone)作為柵極(Gate),最后在襯底引出電極,這樣就構(gòu)成了 N 溝道增強(qiáng)型 MOS 管。

PMOS 和 NMOS 大體相同,在襯底變成 N 型半導(dǎo)體,在摻雜的為 P 型半導(dǎo)體,其余和 NMOS 如出一轍,但是僅僅就是這兩點(diǎn)區(qū)別,卻使得它們的特性完全不同。

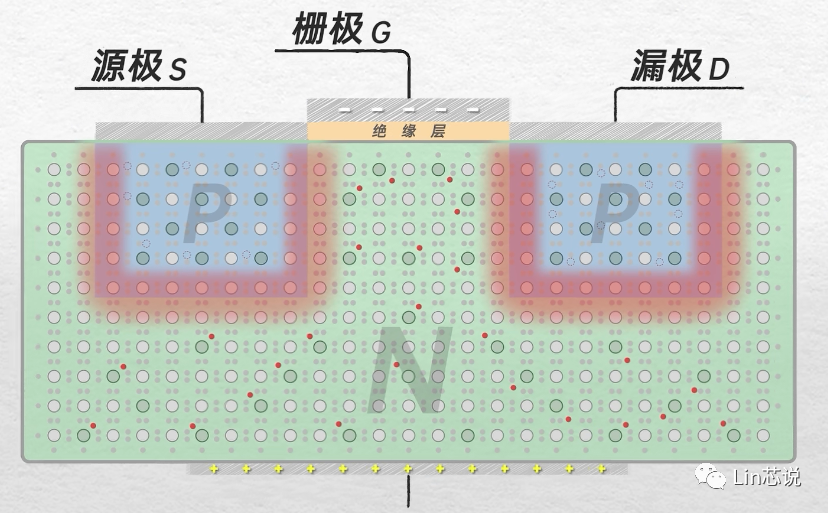

對(duì)于 NMOS 管,當(dāng)對(duì)柵極進(jìn)行正向偏壓(高于閾值電壓)時(shí),在絕緣層下方就會(huì)匯集大量的電子,由于 N 型半導(dǎo)體多電子,就會(huì)與兩側(cè)的 N 型半導(dǎo)體形成 "N 溝道",進(jìn)而實(shí)現(xiàn)整個(gè)回路的導(dǎo)通,如果施加的電壓低于閾值電壓,則無(wú)法實(shí)現(xiàn)導(dǎo)通。

同樣的對(duì)于 PMOS 管,由于襯底和摻雜物互換,如果施加的電壓高于閾值電壓,在絕緣層下方就會(huì)匯集大量空穴,在兩個(gè) P 型半導(dǎo)體之間就會(huì)形成阻隔,無(wú)法導(dǎo)通。如果施加電壓低于閾值電壓,則可以導(dǎo)通。

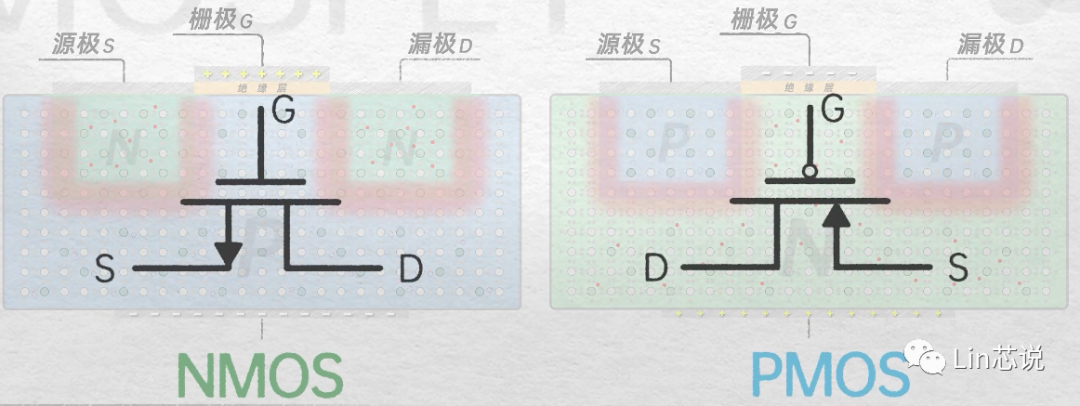

NMOS 和 PMOS 在專業(yè)電路圖如下所示,NMOS 由柵極指向源極,PMOS 由源極指向柵極,并且 PMOS 在柵極處有取反標(biāo)識(shí)。

NMOS 的特性: Vgs 大于一定的值就會(huì)導(dǎo)通,適合用于源極接地時(shí)的情況(低端驅(qū)動(dòng)),只要柵極電壓達(dá)到閾值電壓就可以了。

PMOS 的特性: Vgs 小于一定的值就會(huì)導(dǎo)通,適合用于源極接 VCC 時(shí)的情況(高端驅(qū)動(dòng))。但是,雖然 PMOS 可以很方便地用作高端驅(qū)動(dòng),但由于導(dǎo)通電阻大,價(jià)格貴,替換種類少等原因,在高端驅(qū)動(dòng)中,通常還是使用 NMOS。

同時(shí)衍生一個(gè)問(wèn)題:PMOS 管比 NMOS 管寬的原因是什么?

因?yàn)?PMOS 管是空穴導(dǎo)電,NMOS 管是電子導(dǎo)電,而電子的遷移率約是空穴的 2 倍,因此PMOS 管要寬一些增加遷移速率。

2. MOS 管搭建邏輯門

MOS 管搭建非門

將 PMOS 與 NMOS 的漏極和柵極相連,給 PMOS 的源極接 VDD,給 NMOS 的源極接 GND,給兩個(gè)的共同柵極 In 輸入高于閾值電壓,在前面介紹過(guò),此時(shí) PMOS 截止,NMOS 導(dǎo)通,所以輸出 Out 相當(dāng)于接 GND 拉低,而輸入 In 低于閾值電壓時(shí),此時(shí) PMOS 導(dǎo)通,NMOS 截止,所以輸出 Out 相當(dāng)于接 VDD 拉高。

以次可以得到其真值表:

可以發(fā)現(xiàn)就是反相器,這是最經(jīng)典的 CMOS 結(jié)構(gòu),需要消耗 2 個(gè)晶體管搭建。

基于此可以進(jìn)行更多擴(kuò)展,衍生出各種邏輯門電路。

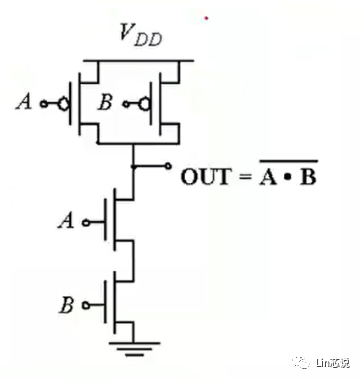

MOS 管搭建與非門

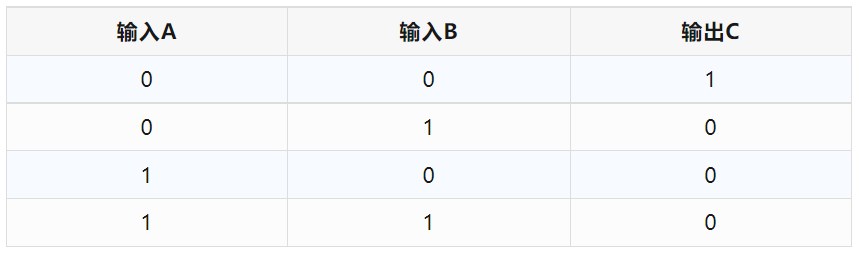

首先看與非門的真值表

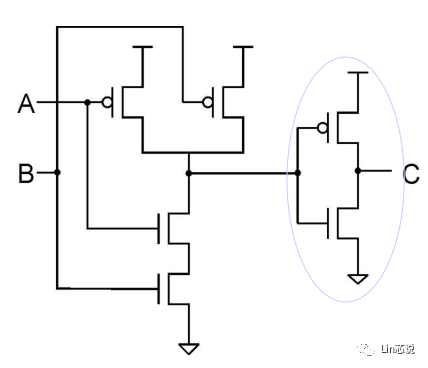

從與非門的真值表中可以看出,只有輸入 A 和 B 都為 1 的情況下,輸出才為 0,其他情況輸出均為 1,結(jié)合到 PMOS 和 NMOS 的性質(zhì)來(lái)看,對(duì)于輸出為 0 的情況,NMOS 輸入為 1 則導(dǎo)通也就是接地為 0,并且需要輸入同時(shí)為 1,相當(dāng)于把兩個(gè) NMOS 串聯(lián),而對(duì)于輸出為 1 的情況,只要兩個(gè)輸入其中有一個(gè)為 0 則輸出為 1,因此相當(dāng)于把兩個(gè) PMOS 并聯(lián),于是得到了以下的邏輯門電路。搭建與非門邏輯門需要耗費(fèi) 4 個(gè)晶體管。

MOS 管搭建或非門

同樣的先看或非門的真值表

有了上面與非門的鋪墊,或非門就更好理解了,由真值表可知,只有在輸入都為 0 的情況下輸出為 1,只要輸入有 1 則輸出為 0,和與非門恰好相反,需要將 PMOS 串聯(lián)接在上端,NMOS 并聯(lián)接在下端,便得到了或非門的邏輯門電路。同樣需要消耗 4 個(gè)晶體管。

MOS 管搭建與門

與門的真值表如下

與門就是在與非門的基礎(chǔ)上,在輸出端接上一個(gè)非門即可。可以發(fā)現(xiàn)搭建與門電路需要消耗 6 個(gè)晶體管,在一些文章或書(shū)籍中看到說(shuō)在設(shè)計(jì)中使用與非門比與門更節(jié)省資源,其實(shí)就是這個(gè)原因。

同理或門也是一樣,這里就不一一列舉了,或門所需要的晶體管同樣為 6 個(gè)。

3. 鎖存器和觸發(fā)器

3.1 交叉耦合反相器

交叉耦合反相器主要有兩種結(jié)構(gòu):

- 順序結(jié)構(gòu)

- 對(duì)稱結(jié)構(gòu)

順序結(jié)構(gòu)

這種結(jié)構(gòu)較為簡(jiǎn)單,當(dāng)輸入為 1 時(shí),經(jīng)過(guò)兩級(jí)反向器輸出仍為 1,輸出又作為輸入。

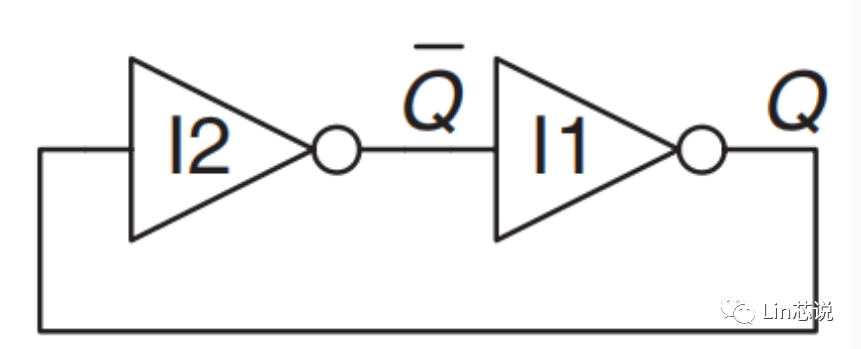

對(duì)稱結(jié)構(gòu)

在對(duì)稱結(jié)構(gòu)中,Q 的輸出作為 Q' 的輸入,同樣 Q' 的輸出作為 Q 的輸入。這里先假設(shè) I1 的輸入為 1,經(jīng)過(guò)反相器輸出得到 Q 為 0,同時(shí)作為 I2 的輸入為 0, Q' 的輸出為 1。這樣輸出就能穩(wěn)定為 1。反過(guò)來(lái)假設(shè) I1 的輸入為 0,經(jīng)過(guò)反相器輸出得到 Q 為 1,同時(shí)作為 I2 的輸入為 1, Q' 的輸出為 0。這樣輸出就能穩(wěn)定為 0。Q 和 Q' 互為對(duì)方的輸入,構(gòu)成雙穩(wěn)態(tài)結(jié)構(gòu)。

這種雙穩(wěn)態(tài)結(jié)構(gòu)雖然結(jié)構(gòu)簡(jiǎn)單,但是缺點(diǎn)在于無(wú)法控制其最終的輸出,并且在結(jié)構(gòu)上是沒(méi)有輸入的。

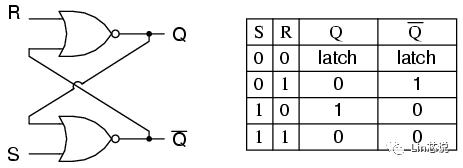

3.2 SR 鎖存器

在上面的雙穩(wěn)態(tài)結(jié)構(gòu)中形成的是閉合的回路,無(wú)法給到輸入,這樣的結(jié)構(gòu)是無(wú)法保存數(shù)據(jù)的,因此就有了下面的結(jié)構(gòu),帶有兩輸入的 SR 鎖存器結(jié)構(gòu),主體由兩個(gè)或非門構(gòu)成,設(shè)上下的或非門為 N1、N2。

以下分情況進(jìn)行討論

R = 1,S = 0

R 端輸入為 1,N1 的輸出 Q 為 0,而 Q 又作為 N2 的輸入,Q' 為 1,此時(shí)表示 R(Reset,復(fù)位)有效,Q 輸出恒為 0。

R = 0,S = 1

S 端輸入為 1,N2 的輸出 Q' 為 0,而 Q' 又作為 N1 的輸入,Q 為 1,此時(shí)表示 S(Set,置位)有效,Q 輸出恒為 1。

R = 0,S = 0

R 端和 S 端輸入為 0,假設(shè) N1 的輸出 Q 為 0,而 Q 又作為 N2 的輸入,Q' 為 1,Q' 又作為 N1 的輸入,得到 N1 的輸出仍然為 0。假設(shè) N1 的輸出 Q 為 1,而 Q 又作為 N2 的輸入,Q' 為 0,Q' 又作為 N1 的輸入,得到 N1 的輸出仍然為 1。此時(shí)表示 R(Reset,復(fù)位)和 S(Set,置位)都無(wú)效,輸出保持輸入不變(hold),也即是常說(shuō)的產(chǎn)生 latch,把數(shù)據(jù)給鎖存起來(lái)了。

R = 1,S = 1

在這個(gè)條件下是無(wú)意義的,此時(shí) Q 和 Q' 都為 0,顯然是不對(duì)的,不能同時(shí)復(fù)位和置位。

由此可以得到 SR 鎖存器的真值表

對(duì)比前面的雙穩(wěn)態(tài)結(jié)構(gòu),SR 鎖存器就有了鎖存數(shù)據(jù)的功能,即當(dāng) S 和 R 都為 0 時(shí),輸出會(huì)一直保持原有的輸入值不變。

RS 鎖存器有兩個(gè)或非門組成,所以需要消耗 4×2=8 個(gè)晶體管。

3.3 D 鎖存器

RS 鎖存器雖然可以鎖存數(shù)據(jù),但是當(dāng) S 和 R 同時(shí)為 0 時(shí)結(jié)果會(huì)出錯(cuò),對(duì)使用帶來(lái)不必要的麻煩,因此需要去規(guī)避,所以有了 D 鎖存器。

D 鎖存器在 RS 鎖存器的基礎(chǔ)上增加了一些控制,E 可以看做使能信號(hào),一般也可以為時(shí)鐘 Clk 信號(hào),基于此對(duì)此電路結(jié)構(gòu)進(jìn)行分析。

E = 0,D = 0

E = 0,則對(duì)應(yīng) R、S 輸入都為 0,參照 RS 鎖存器的真值表得到此時(shí)為 latch,可以鎖存數(shù)據(jù)。

E = 0,D = 1

E = 0 和上面的情況一樣,此時(shí)數(shù)據(jù)仍被鎖存,等效為 latch。

E = 1,D = 0

E = 1 且 D = 0,此時(shí)上面的與門由于 D 取反為 1,與門輸出為 1,相反的,下面的與門輸出為 0,對(duì)應(yīng) RS 鎖存器為 R = 1、S = 0,對(duì)應(yīng) Q 為 0。

E = 1,D = 1

E = 1 且 D = 1,此時(shí)上面的與門由于 D 取反為 0,與門輸出為 0,相反的,下面的與門輸出為 1,對(duì)應(yīng) RS 鎖存器為 R = 0、S = 1,對(duì)應(yīng) Q 為 1。

由此可以得到以下的真值表。

對(duì)上面的結(jié)果進(jìn)一步分析,可以發(fā)現(xiàn) Q 值和 E 值息息相關(guān),當(dāng) E = 1 時(shí),此時(shí) Q 輸出為 D 的值,當(dāng) E = 0 時(shí),此時(shí)數(shù)據(jù)被鎖存。這樣可以發(fā)現(xiàn) D 鎖存器是電平敏感的器件,控制信號(hào) E 一般為時(shí)鐘信號(hào),并且這個(gè)例子的 D 鎖存器為高電平敏感的。

D 鎖存器所消耗的晶體管個(gè)數(shù):

反相器(2)+ 與門(6) 2 + RS 鎖存器(8)= 22 個(gè) *

總共需要消耗 22 個(gè)晶體管。

3.4 D 觸發(fā)器

觸發(fā)器的類型有很多,這里以 D 觸發(fā)器為例

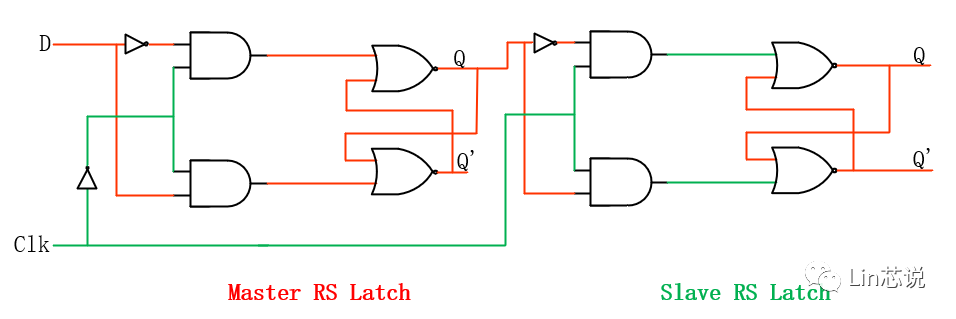

D 觸發(fā)器其實(shí)就是將兩個(gè) RS 鎖存器串聯(lián)起來(lái),第一個(gè) RS 鎖存器稱為 Master,第二個(gè) RS 鎖存器稱為 Slave,Master 的輸出作為 Slave 的輸入,但是兩個(gè) RS 鎖存器的時(shí)鐘使能輸入恰為相反。

再來(lái)分析一下 D 觸發(fā)器是如何運(yùn)作的。

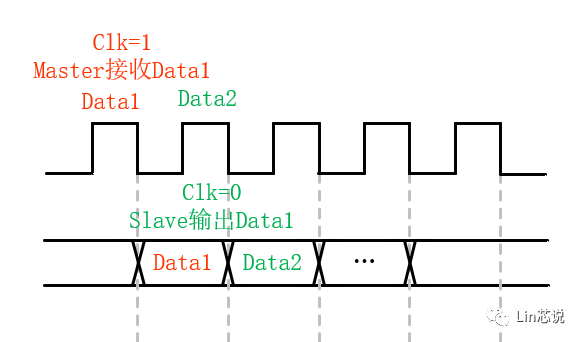

- 假設(shè)輸入為 Data1,當(dāng) Clk = 1 時(shí),此時(shí) Master 工作,Slave 鎖存。根據(jù) RS 鎖存器的真值表,Data1 順利從 Master 輸出。

- 當(dāng) Clk 由 1 變化到 0 時(shí),Clk = 0,此時(shí) Master 鎖存保持原來(lái)的數(shù)據(jù) Data1,Slave 工作,Slave RS 鎖存器將此前輸入數(shù)據(jù) Data1 輸出。

- 當(dāng) Clk 由 0 再次變化到 1 時(shí),Clk = 1,此時(shí) Slave 鎖存保持原來(lái)的輸出 Data1,Maste 鎖存器開(kāi)始工作,接收下一次輸入數(shù)據(jù) Data2,

- 當(dāng) Clk 由 1 再次變化到 0 時(shí),Clk = 0,此時(shí) Master 鎖存保持原來(lái)的輸入數(shù)據(jù) Data2,Slave 鎖存器開(kāi)始工作,將之前 Master 輸出的 Data2 輸出。

就這樣循環(huán)往復(fù)的運(yùn)作,可以看出這個(gè)例子的 D 觸發(fā)器是下降沿有效的,也就是在時(shí)鐘下降沿到來(lái)時(shí),將輸出數(shù)據(jù),其他時(shí)候數(shù)據(jù)保持不變。如果是上升沿有效的,只需要將反相器接在 Master 上。

搭建 D 觸發(fā)器所需要的晶體管數(shù):

D 觸發(fā)器組成 = RS 鎖存器×2 + 反相器 = 22×2 + 2 = 46 個(gè)

4. D 觸發(fā)器的建立、保持時(shí)間

在之前的學(xué)習(xí)中,對(duì)于觸發(fā)器的建立時(shí)間和保持時(shí)間的概念一般就是以下定義:

- 建立時(shí)間: 在時(shí)鐘有效沿到來(lái)之前,數(shù)據(jù)必須維持一段時(shí)間保持不變,這段時(shí)間就是建立時(shí)間 Tsetup

- 保持時(shí)間: 在時(shí)鐘有效沿到來(lái)之后,數(shù)據(jù)必須維持一段時(shí)間保持不變,這段時(shí)間就是保持時(shí)間 Thold

當(dāng)時(shí)只知道觸發(fā)器需要建立時(shí)間和保持時(shí)間使得工作穩(wěn)定,但是為什么需要建立時(shí)間和保持時(shí)間呢?秉持著對(duì)知識(shí)點(diǎn)刨根問(wèn)底的態(tài)度,這里就從更底層出發(fā),去深究觸發(fā)器為什么需要建立時(shí)間和保持時(shí)間。

下圖就是 D 觸發(fā)器的內(nèi)部結(jié)構(gòu)展開(kāi)圖,其主要有兩個(gè) RS 鎖存器組成,在前面的為 Master,后面的為 Slave,兩個(gè)鎖存器串聯(lián)共用一個(gè)時(shí)鐘信號(hào),但是兩者極性相反,為了更符合習(xí)慣,這里的觸發(fā)器定為上升沿敏感的。

為什么需要建立時(shí)間?

在前面分析過(guò),在數(shù)據(jù)傳輸時(shí),Master RS 鎖存器負(fù)責(zé)將數(shù)據(jù)鎖存,Slave RS 鎖存器負(fù)責(zé)將 Master 穩(wěn)定鎖存的數(shù)據(jù)輸出。因此輸入在從 Master 輸入到 Slave 輸出是一個(gè)順序執(zhí)行的過(guò)程,也就是說(shuō)要想從 Slave 順利輸出數(shù)據(jù),那么在 Master 就必須順利鎖存好數(shù)據(jù)。

那就先看 Master RS 鎖存器是如何對(duì)輸入數(shù)據(jù)進(jìn)行鎖存的,數(shù)據(jù)的路徑如下圖中的紅線所示,當(dāng)時(shí)鐘 Clk 為 0 時(shí),數(shù)據(jù)從 D 輸入(假設(shè)數(shù)據(jù)輸入為 0)經(jīng)過(guò)反相器歷時(shí) t1,數(shù)據(jù)變成 1,經(jīng)過(guò)與門歷時(shí) t2 數(shù)據(jù)變成 1,再經(jīng)過(guò)或非門歷時(shí) t3,由于此時(shí)數(shù)據(jù)為 1,所以經(jīng)過(guò)或非門 Q 端輸出為 0,Q 端輸出又作為下面的或非門輸出為 1,并且在此歷時(shí) t4,最終在 Q 端輸出 0,此時(shí)數(shù)據(jù)便順利被鎖存起來(lái)。

這里忽略不計(jì)門與門之間的路徑延時(shí)時(shí)間,只對(duì)時(shí)間做個(gè)大概分析,從這里可以計(jì)算得到所歷經(jīng)的總時(shí)長(zhǎng)為:t1+t2+2*t3+t4,這個(gè)時(shí)間就可以大致認(rèn)為是觸發(fā)器的建立時(shí)間 Tsetup。當(dāng)經(jīng)過(guò) Tsetup 后數(shù)據(jù)被穩(wěn)定的鎖存,當(dāng)時(shí)鐘上升沿到來(lái)時(shí)(0->1),Slave RS 鎖存器就可以接受到正確的數(shù)據(jù)并輸出,如果不滿足建立時(shí)間需求的話會(huì)發(fā)生什么情況呢?

假設(shè)此時(shí)不滿足建立時(shí)間需求,當(dāng)需要被鎖存的數(shù)據(jù)在還未進(jìn)入到第一個(gè)或非門時(shí),時(shí)鐘上升沿就已經(jīng)來(lái)到,此時(shí) Q 端輸出的數(shù)據(jù)仍然是上一次被鎖存的不確定數(shù)據(jù),可能為 1 也可能為 0,這樣 Slave 輸出的數(shù)據(jù)就可能會(huì)出錯(cuò)。

為什么需要保持時(shí)間?

再來(lái)分析一下保持時(shí)間,如下圖中綠線為時(shí)鐘到達(dá)與門的路徑延時(shí)假設(shè)為 t5,藍(lán)線為數(shù)據(jù)到達(dá)與門的路徑延時(shí)假設(shè)為 t6,因?yàn)闀r(shí)鐘路徑存在反相器延時(shí),所以延時(shí)會(huì)大一些,即 t5>t6,假設(shè)在 Slave 輸出數(shù)據(jù)的過(guò)程中,輸入數(shù)據(jù) D 由原來(lái)的 0 跳變到 1,此時(shí)由于 t5>t6,就有可能使得與門的兩個(gè)輸入同時(shí)為 1(時(shí)鐘上升沿來(lái)臨之前 Clk 為 0,經(jīng)反相器輸出為 1),此時(shí)與門輸出為 1,推出 Q' 輸出為 0,進(jìn)而 Q 輸出為 1,于是新到來(lái)的輸出 Q = 1 就會(huì)將影響原來(lái)的 0,最后導(dǎo)致鎖存的數(shù)據(jù)為 1,最終 Slave 的輸出為 1,導(dǎo)致數(shù)據(jù)出錯(cuò),這就是為什么輸入數(shù)據(jù)需要在時(shí)鐘上升沿來(lái)臨之后仍然保持一段時(shí)間(t5-t6)不變。

從上面的分析可以得出,D 觸發(fā)器的建立時(shí)間要求比保持時(shí)間要求要更嚴(yán)苛,這也是在 RTL 設(shè)計(jì)綜合后,建立時(shí)間違例比保持時(shí)間違例更頻繁的原因,要求高了自然就更難達(dá)到,同時(shí)建立時(shí)間和保持時(shí)間也是相悖的,建立時(shí)間要求數(shù)據(jù)路徑延時(shí)更小,數(shù)據(jù)路徑延時(shí)越小,Master 鎖存器更容易將數(shù)據(jù)鎖存;保持時(shí)間希望數(shù)據(jù)路徑延時(shí)更大,一旦使得數(shù)據(jù)路徑延時(shí) t6>t5,Slave 鎖存器輸出的數(shù)據(jù)就不會(huì)出錯(cuò)。

-

MOSFET

+關(guān)注

關(guān)注

147文章

7242瀏覽量

214282 -

場(chǎng)效應(yīng)晶體管

+關(guān)注

關(guān)注

6文章

365瀏覽量

19593 -

D觸發(fā)器

+關(guān)注

關(guān)注

3文章

164瀏覽量

48021 -

GND

+關(guān)注

關(guān)注

2文章

540瀏覽量

38904 -

閾值電壓

+關(guān)注

關(guān)注

0文章

73瀏覽量

51517

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

靜態(tài)時(shí)序之建立時(shí)間和保持時(shí)間分析

芯片設(shè)計(jì)進(jìn)階之路—從CMOS到建立時(shí)間和保持時(shí)間

淺析D觸發(fā)器的建立時(shí)間和保持時(shí)間物理含義

數(shù)字電路中,建立時(shí)間和保持時(shí)間對(duì)于觸發(fā)器的時(shí)鐘信號(hào)有

建立時(shí)間和保持時(shí)間討論

保持時(shí)間與建立時(shí)間

請(qǐng)問(wèn)怎么求這個(gè)D2觸發(fā)器的建立時(shí)間和保持時(shí)間的關(guān)系呀

數(shù)字 IC 筆試面試必考點(diǎn)(9)建立時(shí)間以及保持時(shí)間 精選資料分享

為什么觸發(fā)器要滿足建立時(shí)間和保持時(shí)間

為什么觸發(fā)器要滿足建立時(shí)間和保持時(shí)間

到底什么是建立時(shí)間/保持時(shí)間?

SOC設(shè)計(jì)中的建立時(shí)間和保持時(shí)間

PCB傳輸線建立時(shí)間、保持時(shí)間、建立時(shí)間裕量和保持時(shí)間裕量

從底層重新認(rèn)識(shí)D觸發(fā)器、建立時(shí)間和保持時(shí)間

從底層重新認(rèn)識(shí)D觸發(fā)器、建立時(shí)間和保持時(shí)間

評(píng)論