本文記錄SDC約束文件中比較復(fù)雜的一些命令,包括時(shí)鐘分頻、時(shí)序例外、多周期約束、半周期約束、多時(shí)鐘約束等。感覺(jué)項(xiàng)目中能用到的基礎(chǔ)命令差不多就總結(jié)完了。

時(shí)鐘分頻

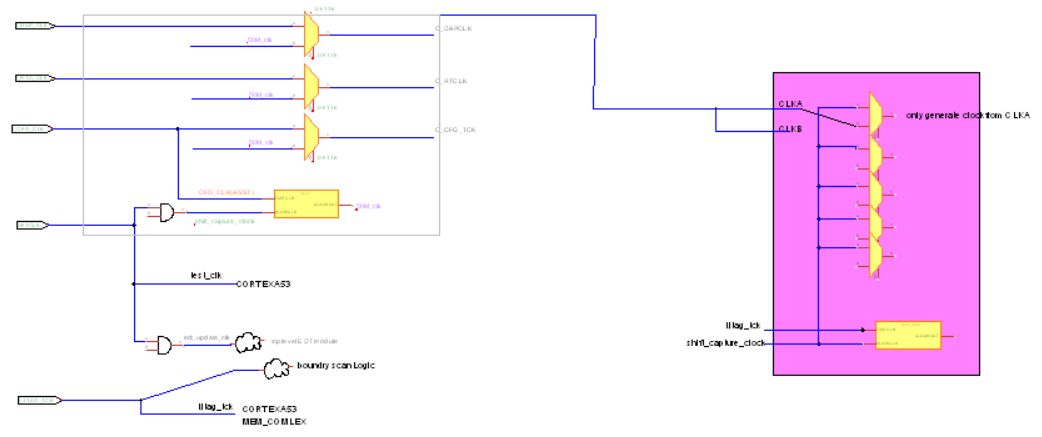

時(shí)鐘信號(hào)穿過(guò)時(shí)序單元分頻之后,需要人為設(shè)置generatedclock,工具才能夠正確推導(dǎo)分頻之后的時(shí)鐘。因?yàn)?a target="_blank">EDA工具在STA時(shí),時(shí)鐘信號(hào)不能穿透時(shí)序單元傳播。

命令:

create_generated_clock-divide_by 2 -nameCLKG-source[get_portsCLK] [get_pinsFF1/Q]

set_clock_latencyvalue[get_clocksCLKG]#設(shè)置延時(shí)

set_clock_uncertaintyvalue[get_clocksCLKG]#設(shè)置不確定性

set_clock_transitionvalue[get_clocksCLKG]#設(shè)置轉(zhuǎn)換時(shí)間

除-divide_by之外,還可以采用-edges更精確的表明相對(duì)于masterclock,generatedclock的時(shí)鐘跳變邊沿。

FalsePath

某些情況下,設(shè)計(jì)中的確存在某些路徑,但是這些路徑之間的時(shí)序是不可能的,或者不是真實(shí)的,就要設(shè)置falsepath,讓工具不再對(duì)該路徑進(jìn)行STA(注意只是不進(jìn)行時(shí)序分析,路徑還是存在的)。比如跨時(shí)鐘域之間的路徑,不會(huì)跳變的路徑等,或者不可能的路徑等。命令為:

set_false_path

互斥時(shí)鐘

多個(gè)時(shí)鐘是同步的,但是邏輯是相互排斥的,比如通過(guò)MUX二選一的時(shí)鐘,他們之間的時(shí)序路徑也不需要分析,為了讓工具不再優(yōu)化兩時(shí)鐘之間的時(shí)序,可以用兩種命令約束:

方法1:

set_false_path-from[get_clocks CLK1] -to [get_clocks CLK2]

方法2:

set_clock_group-logically_exclusive-groupCLK1 -groupCLK2

-logical_exclusive表示兩個(gè)時(shí)鐘在邏輯上是不能同時(shí)存在的。如果物理上不能同時(shí)存在,比如同一個(gè)時(shí)鐘源定義了兩個(gè)時(shí)鐘,就要采用-physically_exclusive。

異步時(shí)鐘

兩個(gè)設(shè)計(jì)的時(shí)鐘來(lái)自于兩個(gè)不同的晶振,時(shí)鐘源沒(méi)有任何關(guān)系,頻率不確定,相位不確定,這兩個(gè)時(shí)鐘就叫異步時(shí)鐘,工具無(wú)法對(duì)異步時(shí)鐘進(jìn)行時(shí)序分析,也沒(méi)必要進(jìn)行時(shí)序分析。但是設(shè)計(jì)人員要確保信號(hào)在異步時(shí)鐘域之間的傳輸時(shí)不出現(xiàn)亞穩(wěn)態(tài)。一般采用打兩拍、握手、fifo等跨時(shí)鐘域處理方式。

命令為:

set_clock-asynchronous-groupCLKA-groupCLKB

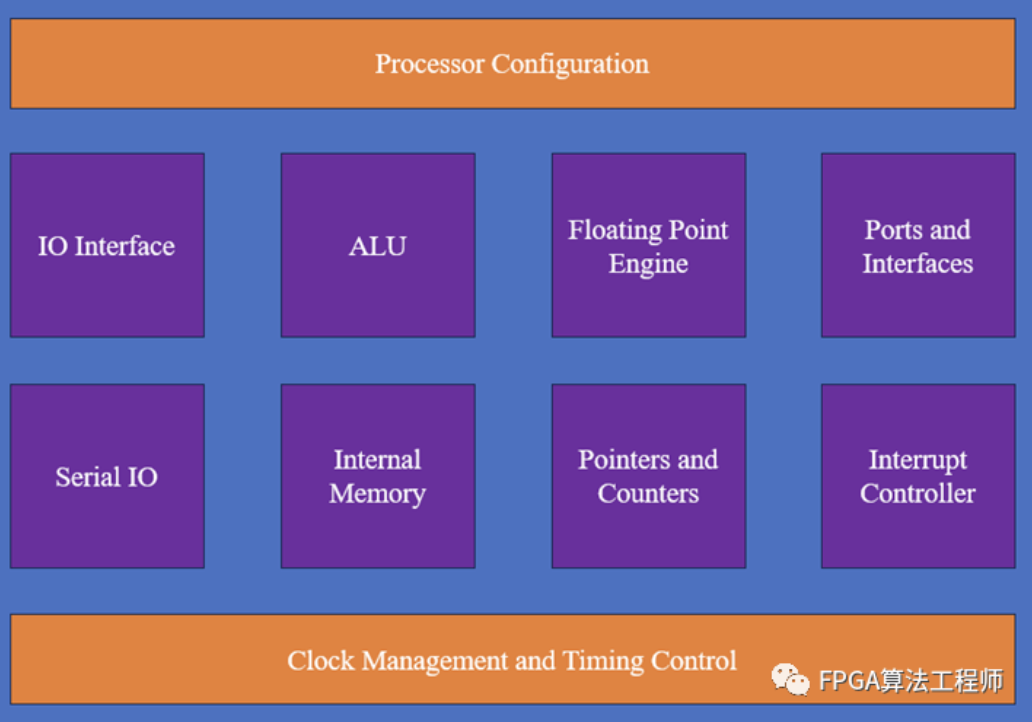

set_case_analysis

用于約束固定0/1,或者只有上升沿/下降沿的端口,在這個(gè)端口散出的路徑中,就只有0/1,或者只分析上升沿/下降沿。在MMMC設(shè)置中,經(jīng)常用這個(gè)設(shè)置芯片的不同工作模式。

多周期設(shè)計(jì)

在設(shè)計(jì)中,當(dāng)兩個(gè)寄存器之間的組合邏輯路徑里,數(shù)據(jù)傳輸花費(fèi)的時(shí)間多于一個(gè)時(shí)鐘周期,就需要為這個(gè)組合邏輯路徑聲明為多時(shí)鐘周期路徑。

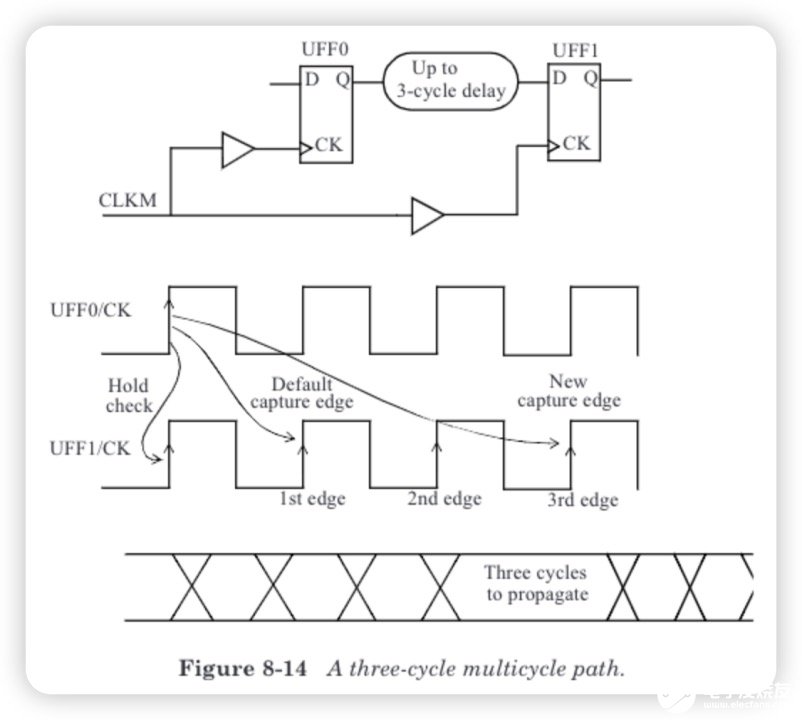

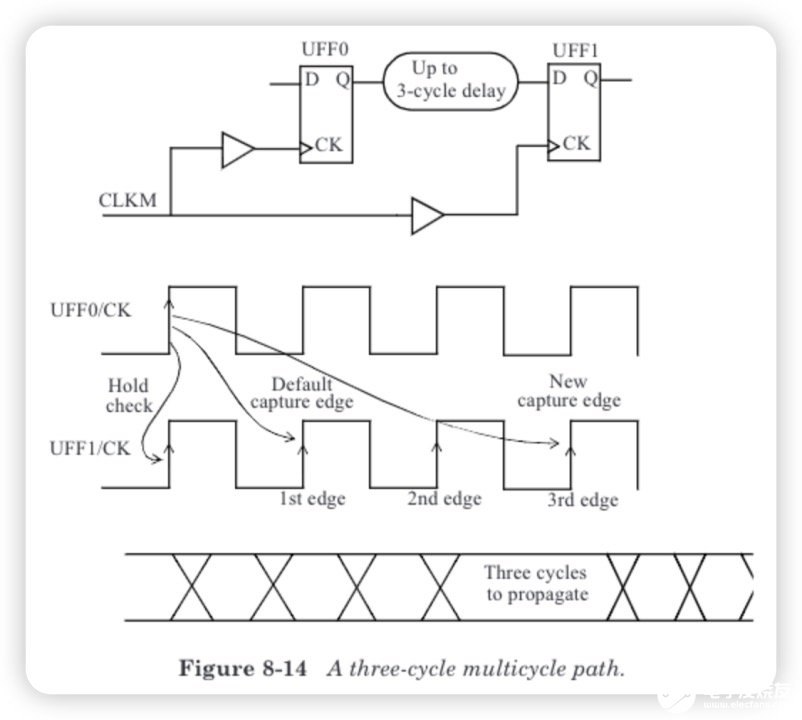

上圖中,兩個(gè)寄存器之間的組合路徑需要3個(gè)時(shí)鐘周期。對(duì)建立時(shí)間的約束命令為:

create_clock-nameCLKM -period 10 [get_portsCLKM]

set_multicycle_path 3 -setup -from[get_pins UFF0/Q] -to [get_pinsUFF1/D]

接下來(lái)考慮hold時(shí)間檢查,默認(rèn)的hold檢查是setup之前的有效沿(2ndedge),但是實(shí)際上數(shù)據(jù)不需要經(jīng)過(guò)這么久的延時(shí),實(shí)際上hold檢查的合理有效沿需要提前2個(gè)周期(setup-1),因此hold約束命令為:

set_multicycle_path 2 -hold -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

此外,如果該多時(shí)鐘周期路徑分為兩個(gè)部分A和B,其中A的延時(shí)為3clockcycles,B的延時(shí)是一個(gè)標(biāo)準(zhǔn)的時(shí)鐘周期,那么可以只用-through選項(xiàng)約束慢速的部分。命令:

set_multicycle_path 3 -setup-througSLOW

set_multicycle_path2-hold-throughSLOW

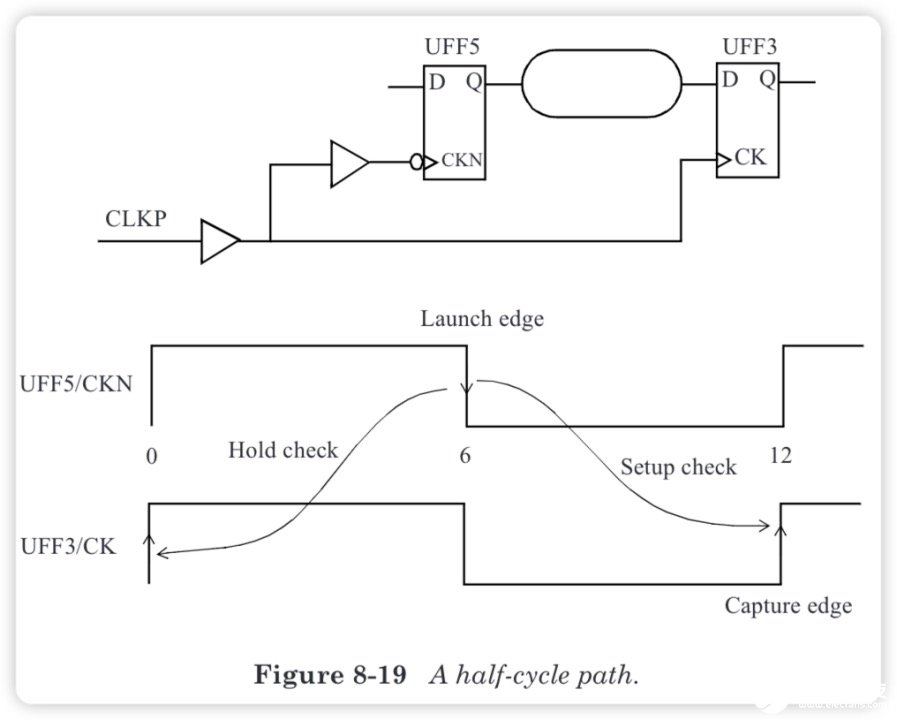

Half-Cycle Paths

當(dāng)設(shè)計(jì)中同時(shí)存在上升沿和下降沿出發(fā)的場(chǎng)景,就很可能存在half-cyclepath。比如上升沿出發(fā)的寄存器到下降沿觸發(fā)的寄存器或者下降沿出發(fā)的寄存器到上升沿觸發(fā)的寄存器,如下所示。

建立時(shí)間中,數(shù)據(jù)的ArriveTime等于下降沿的6ns延時(shí)加上數(shù)據(jù)的延時(shí),RequireTime為12ns的時(shí)鐘周期。即數(shù)據(jù)只有半個(gè)時(shí)鐘周期的時(shí)間,因此對(duì)建立時(shí)間的約束更苛刻了。

保持時(shí)間的含義是在時(shí)鐘沿跳變時(shí),上一個(gè)狀態(tài)不能變化太快。如上圖所示,保持時(shí)間的檢查的有效沿為caputreedge的上一個(gè)上升沿,由于launchedge已經(jīng)有半個(gè)周期6ns的延時(shí)了,因此數(shù)據(jù)總是在6ns之后才來(lái)的,因此保持時(shí)間的裕量特別大。

多時(shí)鐘約束

設(shè)計(jì)內(nèi)部包含多個(gè)時(shí)鐘,但是所有時(shí)鐘都通過(guò)一個(gè)時(shí)鐘源分頻得到,這種是同步時(shí)鐘,相位都是固定的。工具在分析時(shí)序時(shí),會(huì)自動(dòng)計(jì)算兩時(shí)鐘信號(hào)相鄰最近的相位的時(shí)間差,作為STA檢查中的RequireTime。

在輸入/出端口,一個(gè)輸入/出對(duì)應(yīng)著多個(gè)時(shí)鐘的輸入,這種需要對(duì)該端口進(jìn)行多約束。

多時(shí)鐘輸入延時(shí)

create_clockCLKA#內(nèi)部時(shí)鐘

create_clockCLKB#外部時(shí)鐘

set_input_delay1 -clockCLKB-max【get_portsA】

其中CLKA為待優(yōu)化模塊內(nèi)部的采集端口A數(shù)據(jù)的時(shí)鐘,CLKB為待優(yōu)化模塊外部驅(qū)動(dòng)數(shù)據(jù)進(jìn)入端口A的虛擬時(shí)鐘。

多時(shí)鐘輸出延時(shí)

create_clockCLKA#內(nèi)部時(shí)鐘

create_clockCLKB#外部采集時(shí)鐘B

create_clockCLKC#外部采集時(shí)鐘C

set_output_delay1 -clockCLKB-max【get_portsA】

set_output_delay1 -clockCLKC-add_delay-max【get_portsA】

Removal/RecoveryTiming

可以理解為復(fù)位信號(hào)的“Setup/HoldTime”。

審核編輯:黃飛

-

時(shí)鐘源

+關(guān)注

關(guān)注

0文章

93瀏覽量

16038 -

時(shí)鐘信號(hào)

+關(guān)注

關(guān)注

4文章

453瀏覽量

28666 -

異步時(shí)鐘

+關(guān)注

關(guān)注

0文章

17瀏覽量

9427 -

時(shí)鐘分頻

+關(guān)注

關(guān)注

0文章

4瀏覽量

5732

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

時(shí)序約束實(shí)操

時(shí)序分析的設(shè)計(jì)約束(SDC)

聊聊ASIC設(shè)計(jì)約束與SDC命令

ASIC設(shè)計(jì)約束與SDC命令介紹

Linux中常用的壓縮和解壓縮命令介紹

時(shí)序約束 專版

Linux系統(tǒng)中常見(jiàn)的壓縮命令工具概述

總結(jié)嵌入式系統(tǒng)開(kāi)發(fā)中常見(jiàn)的存儲(chǔ)器及其特點(diǎn)

如何將Altera的SDC約束轉(zhuǎn)換為Xilinx XDC約束

時(shí)序分析的設(shè)計(jì)約束SDC怎么寫呢?

時(shí)序分析基本概念—SDC概述

ASIC設(shè)計(jì)約束與SDC命令

SDC約束文件中常見(jiàn)的基礎(chǔ)命令總結(jié)

SDC約束文件中常見(jiàn)的基礎(chǔ)命令總結(jié)

評(píng)論