對(duì)于信號(hào)而言,phase shift是一個(gè)相對(duì)值,而time delay是絕對(duì)值。有時(shí)候我們關(guān)心time delay,那么如何由phase得到延遲時(shí)間呢?

假設(shè)信號(hào)經(jīng)過一階低通濾波器(-3dB帶寬為f0),那在所有頻率點(diǎn),信號(hào)的delay是怎樣的?

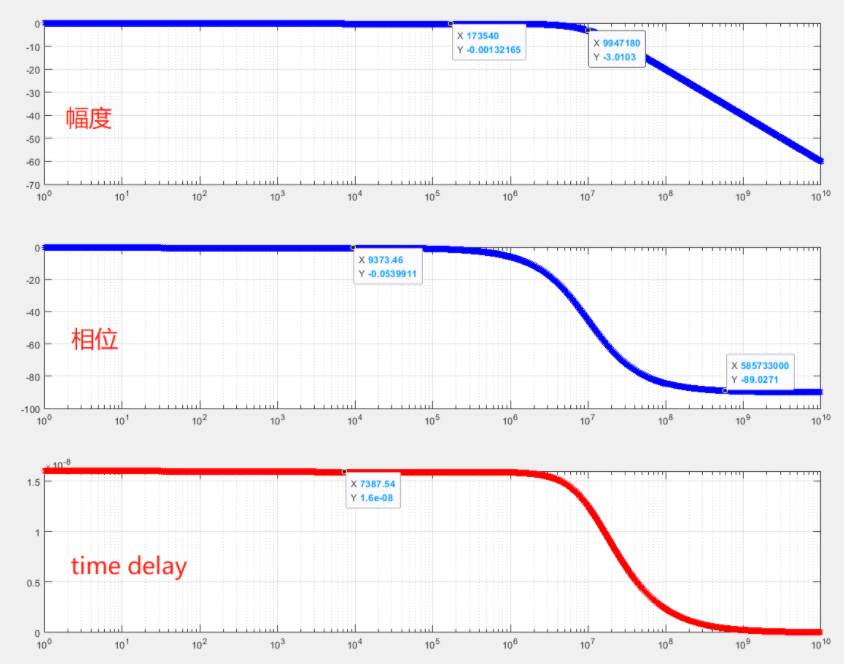

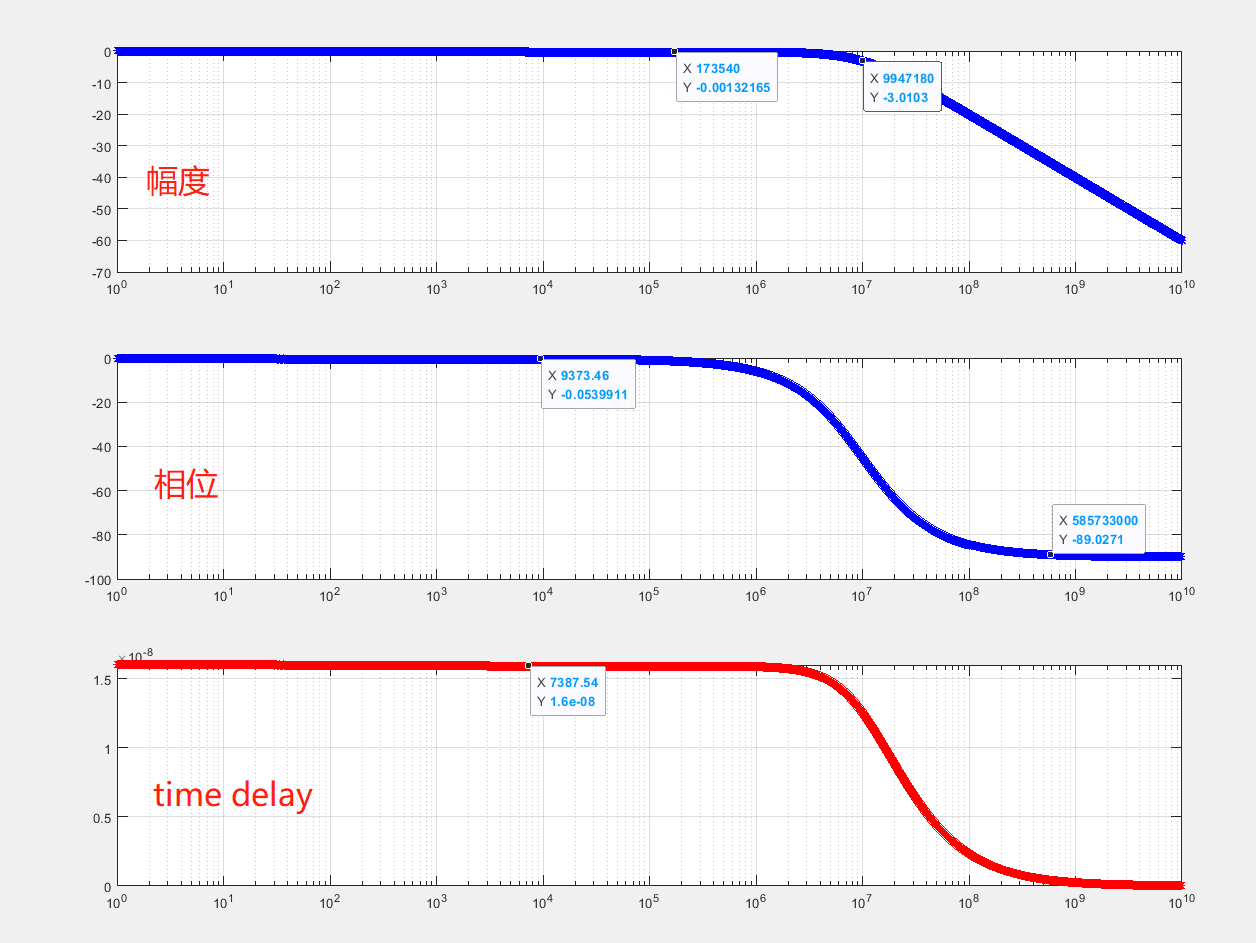

tao=16ns時(shí),我用matlab plot了一下幅度、相位和time delay,其中time delay=phase/w (其中w為角頻率,phase量綱為rad/s)

可以看出低頻的time delay=tao,高頻信號(hào)沒有delay。

在數(shù)學(xué)上time delay=arctan(f/f0)/(2*pi*f)

當(dāng)f/f0為無窮小時(shí),上式近似為1/(2*pi*f0)=tao ==》原來tao的物理意義在這里,意味著小于f0的頻率基本都delay tao。

當(dāng)f遠(yuǎn)大于f0時(shí),time delay=0,可以理解為相位偏差90度但由于周期無窮小,所以delay為0;

中間階段就按照arctan(f/f0)/(2*pi*f)的公式來,time delay和頻率是一個(gè)非線性的關(guān)系。

**************************************************************

我因此繼續(xù)延伸一個(gè)話題:一個(gè)閉環(huán)運(yùn)放,當(dāng)gbw不變,而phase margion變化時(shí),在gbw處的環(huán)內(nèi)信號(hào)(也可以理解為干擾) delay time一樣嗎?如果環(huán)內(nèi)信號(hào)的delay time特別關(guān)鍵,那么可以認(rèn)為即使gbw相同,當(dāng)phase margion不同時(shí),在gbw處的干擾信號(hào)的抵消速度不一樣。

再進(jìn)一步,如果是一個(gè)dc-dc或pll,帶內(nèi)雙極點(diǎn),一個(gè)零點(diǎn),那么即使gbw不同,在零極點(diǎn)位置相同(dc增益不同)時(shí),環(huán)路的響應(yīng)速度(高頻處的相位)是一樣的(但抵消的幅度不一樣,這么分析好像實(shí)際意義不大,但把環(huán)路反饋拆分為速度(時(shí)間)和幅度,有利于更細(xì)致的分析環(huán)路響應(yīng)問題和做改進(jìn))。

再往前,環(huán)路問題拆分為幅度和速度(時(shí)間,也可以認(rèn)為是頻率)后,在sdm adc中,如果要優(yōu)化int1對(duì)idac的瞬態(tài)響應(yīng),由于idac方波中包含了各種頻率分量,為了使方波中各次諧波都能有響應(yīng),此時(shí)opamp的gbw要足夠大。

而當(dāng)設(shè)計(jì)一個(gè)濾波器,想要在某個(gè)頻段有很好的線性度時(shí),可以不用做很高的gbw,而利用一些復(fù)極點(diǎn)把關(guān)心的頻段做一個(gè)peak即可。

以上的分析說明,明確對(duì)速度(頻率)和幅度的要求后,改進(jìn)方法會(huì)很有針對(duì)性。

審核編輯:黃飛

-

濾波器

+關(guān)注

關(guān)注

161文章

7860瀏覽量

178934 -

低通濾波器

+關(guān)注

關(guān)注

14文章

485瀏覽量

47535 -

諧波

+關(guān)注

關(guān)注

7文章

830瀏覽量

41892 -

信號(hào)

+關(guān)注

關(guān)注

11文章

2804瀏覽量

77106

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

信號(hào)如何由phase得到延遲時(shí)間呢?信號(hào)的delay是怎樣的?

調(diào)用Time_Auto_Decrement()函數(shù)來是LED_Delay_Time變量的值遞減,為什么值卻不變?

pcm1796數(shù)據(jù)中的delay time和pcm1748數(shù)據(jù)手冊(cè)中的group delay是同一個(gè)意思嗎?

在FPGA內(nèi)手動(dòng)做Delay

testbench時(shí)鐘信號(hào)

Design considerations for three-phase power factor correction

Phase Noise Analysis in CMOS L

UCC28950,pdf(Green Phase-Shift

數(shù)字控制移相-Digitally Control Phase

數(shù)字控制移相-Digitally Control Phase

Propagation Delay Measurements

Accounting for delay from multiple sources in delta-sigma ADCs

淺談信號(hào)delay time和phase shift

淺談信號(hào)delay time和phase shift

評(píng)論