計算機領域總是在持續不斷地進步,始終有發展變化和更新迭代等待著我們去體驗和探索。從頭開始打造一臺新的 PC 是一種令人愉悅的體驗,有新一代標準時更是如此。說到這里,我們不得不提到有關隨機存取存儲器 (RAM) 的話題。具體來說是 DDR4 RAM,這恰好是市場上目前的標準。RAM 的重要性眾所周知,如果我們問到任何計算機或網絡工程師,他們都會表示擁有再多的 RAM 也不為過。

基于 DDR4 實現的 PCB 架構改進

如上所述,計算機技術領域的格局不斷發展變化。隨著新標準的出現,設備架構需要作出相應調整。這一表述同樣適用于從 DDR3 到 DDR4 的代際標準變化。

隨機存取存儲器的這些進步也顯著提升了整體性能。因此,想要利用最新的 RAM,就需要改變 PCB 設計;正如 USB 標準從 USB 2.0 發展到 USB 3.0 時一樣。隨著市場對更強處理能力、更佳性能和更高級功能的需求不斷推動行業的發展,這些類型的改變是持續且必要的。

盡管大多數人不會注意到或看到 PCB 設計所需的架構變化,但這并沒有降低這些關鍵變化的重要性。

1. 實現 DDR4,PCB Layout 需要作出什么改變?

雙倍數據速率 4 (Double Data Rate 4)簡稱 DDR4,有兩種不同的模塊類型。其中一種模塊類型是小型雙列直插式內存模塊(260 個引腳),簡稱 So-DIMM,用于筆記本電腦等便攜式計算設備。另一種模塊類型是雙列直插式內存模塊(288 個引腳),簡稱 DIMM,用于臺式機和服務器等設備。

因此,架構的第一個變化當然是引腳數所致。上一迭代 (DDR3) 的 DIMM 使用 240 個引腳,So-DIMM 為 204 個引腳。而前文提到的 DDR4 的 DIMM 使用 288 個引腳。隨著引腳或觸點的增加,DDR4 提供更大的 DIMM 容量、更好的數據完整性、更快的下載速度和更高的能效。

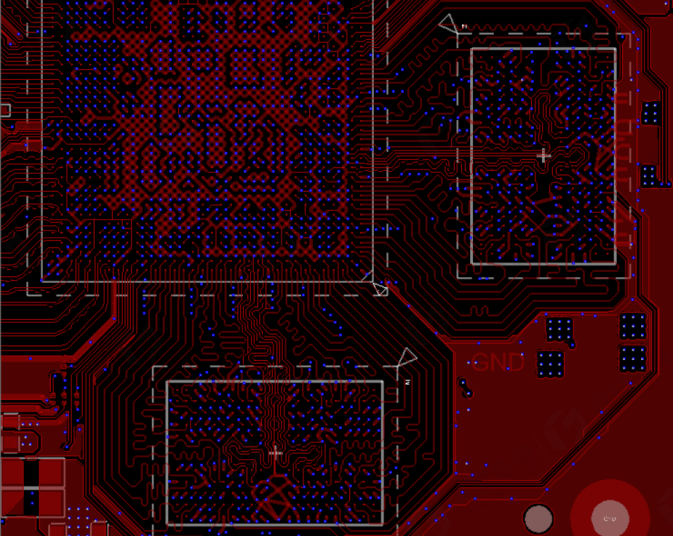

各種類型的 DDR RAM 芯片

與這種整體性能改進一同出現的還有一種彎曲設計(底部),可以實現更好、更安全的連接,并提高安裝過程中的穩定性和強度。此外,臺架測試證明,DDR4 使性能提升了 50%,最高可達 3,200 MTs(每秒兆傳輸率)。

而且,這些性能提升是在降低功耗的情況下實現的:每個 DIMM僅耗費1.2 伏,而不是上一代標準要求的 1.5 至 1.35 伏。所有這些變化意味著 PCB 設計人員必須重新評估設計方法來實現 DDR4。

2. PCB DDR4 設計指南

如果我們希望電子設備或元件以最佳水平運行,則需要精準的 PCB 設計,其中包括 DDR4 的實現。這一點很好理解。除了需要設計精度之外,還必須符合當今的內存。

PCB 設計人員也必須考慮各種其他因素,例如空間分配和關鍵連接。還需要管理初始設計階段,因為想要成功實施,設計必須滿足布線拓撲和設計規范。

為了有效管理數據,PCB 應遵循布線和最佳實踐 (PCB),否則會導致若干問題,包括易感性和輻射發射。PCB 設計人員還應該利用適當的技術來實現大規模扇出和高邊緣速率,以保持低誤碼率和 1.6 至 3.2 Gbps 的數據范圍。同樣,如果沒有適當的設計技術,我們的 PCB 將遇到信號完整性問題并導致串擾和由此產生的(過度)抖動。

3. DDR4 布線指南以及長度和間距規則

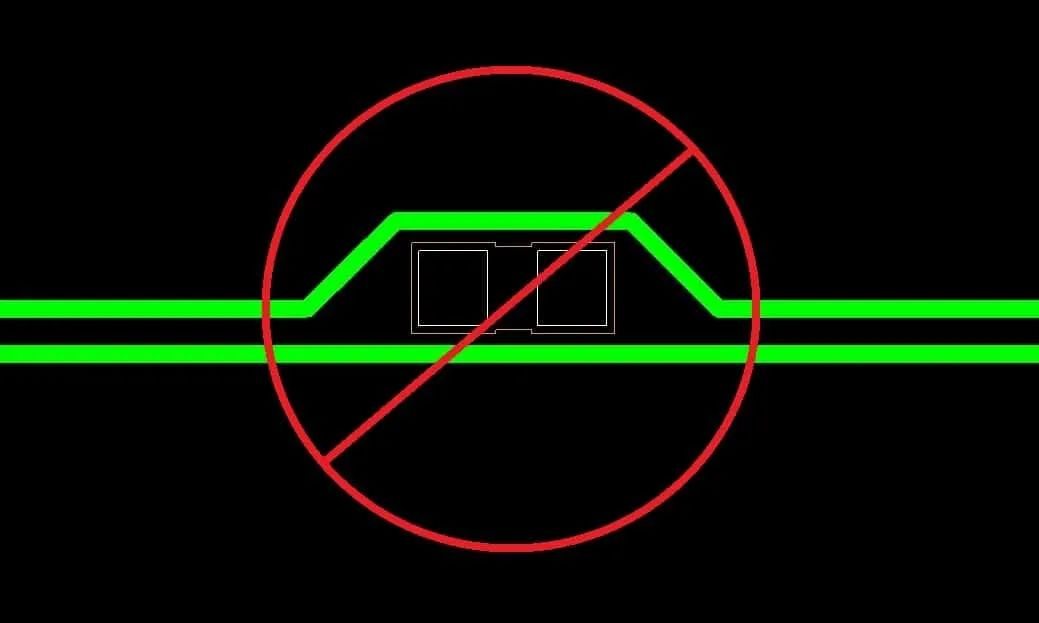

在 PCB 設計中,想要實現最佳布線路徑,需要正確放置 DIMM 連接器和正確使用內存芯片。一般來說,DDR4 SDRAM 需要更短的布線和適當的間距,以實現峰值時序和最佳信號完整性。PCB 設計人員還應在相關信號組中進行引腳交換。此外,在實現過程中,應避免信號布線位于空隙處、信號層布線彼此相鄰以及參考平面分割。

同時,如果可以的話,我們還應該在電源層或適當的接地 (GND) 之間進行存儲器接口信號布線。此外,可以通過在同一層的同一字節通道組中進行 DQ(輸入/輸出數據)、DQS(數據選通)和 DM(數據掩碼)信號布線來幫助減少或消除傳輸速度差異。與 DQS 信號相比,時鐘信號的傳播延遲更長,因此時鐘信號的走線長度通常需要比雙列直插式內存模塊中最長的 DQS 走線更長。

最后,我們必須牢記,每個電路板堆疊都是不同的,間距要求也是如此。因此,必須利用場求解器 (如Cadence Clarity? 3D Solver) 在臨界信號之間建立低于 -50dB 的串擾。請注意:從時鐘到 DQS 沒有長度要求,但是從時鐘到命令/控制/地址有長度要求。長度要求取決于材料的 Dk(介電常數)和每個 SDRAM 的負載。

4. DDR4 層分配和數據通道參考

可以將 DQS、DQ 和 DM 網絡分配給堆疊中任何可用的內部帶狀線層。而地址/命令/控制和時鐘應在更靠近 SDRAM 的層上進行布線,以最大限度地減少過孔耦合。

地址/命令/控制 SDRAM 過孔應該在每個 SDRAM 處添加連接到接地的過孔(陰影過孔),以減少過孔耦合。

此外,地址和控制參考電源層或接地取決于控制器。需要注意的是,DIMM 有地址和控制參考電源層,而板載 BGA(球柵陣列)很少有地址和控制參考電源層。

DDR4 會給設計增添大量的復雜性,但遵守指南可以緩解這種情況

DDR4 與上一代標準 (DDR3) 一樣,在實現時需要新的設計方法。顯然,為了適應升級后的性能,設計要求有所變動,這是創新的副作用。然而,遵循正確的設計和拓撲技術可以最大程度地利用這一當代的新標準來提升性能。

無論是要實現任何形式的 DDR 內存,還是從事于對信號要求特別高的設計,Cadence 的設計和分析工具套件都能助您一臂之力。Allegro? PCB Designer 不僅可以為您提供對元件進行恰當放置和布線的布局解決方案,而且還能提供一整套工具來加強分析和生產,確保設計比您預期的“雙倍數據速率”更快。

文章來源: Cadence楷登PCB及封裝資源中心

審核編輯 黃宇

-

pcb

+關注

關注

4326文章

23160瀏覽量

399929 -

布線

+關注

關注

9文章

777瀏覽量

84428 -

DDR4

+關注

關注

12文章

322瀏覽量

40955

發布評論請先 登錄

相關推薦

DDR電路PCB布局布線技巧

DDR電路的PCB布局布線要求

【PCB設計干貨】DDR電路的PCB布局布線要求

DDR4復位偏差要求是什么?

AM64x\\AM243x DDR 電路板設計及布局指南

DDR4,什么是DDR4

DDR4設計規則及DDR4的PCB布線指南

DDR4 PCB布線指南和PCB架構的建造

DDR4原理及硬件設計

DDR電路的PCB布局布線要求

PCB的DDR4布線指南和PCB的架構改進

PCB的DDR4布線指南和PCB的架構改進

評論