CPU的外部時(shí)鐘電路和其外接晶振,作用是一樣的嗎?

CPU的外部時(shí)鐘電路和外接晶振在一定程度上起到了相似的作用,但細(xì)節(jié)上存在一些差異。在本文中,我將詳細(xì)討論這兩者的作用、原理以及它們之間的關(guān)系。

首先,讓我們了解CPU的外部時(shí)鐘電路。外部時(shí)鐘電路,又稱為系統(tǒng)時(shí)鐘或總線時(shí)鐘,是一種用來(lái)驅(qū)動(dòng)CPU和其他硬件設(shè)備的電路。它通過(guò)產(chǎn)生穩(wěn)定的方波脈沖信號(hào)來(lái)同步各個(gè)組件的工作,有效地協(xié)調(diào)CPU和系統(tǒng)內(nèi)的其他硬件設(shè)備之間的數(shù)據(jù)傳輸和運(yùn)算。

外部時(shí)鐘電路通常由集成電路(IC)或晶振驅(qū)動(dòng)。它負(fù)責(zé)產(chǎn)生一個(gè)基準(zhǔn)頻率的時(shí)鐘信號(hào),該信號(hào)將告訴CPU和其他硬件設(shè)備何時(shí)執(zhí)行操作。這個(gè)基準(zhǔn)頻率通常以赫茲(Hz)為單位表示,例如3.2 GHz或4.0 GHz。

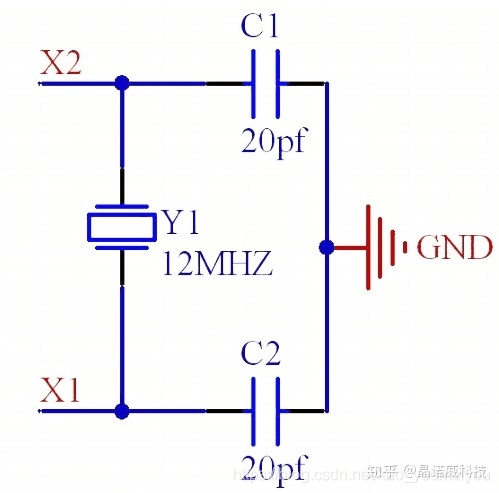

那么外接晶振是什么呢?外接晶振是一種獨(dú)立于CPU的設(shè)備,用于產(chǎn)生穩(wěn)定的時(shí)鐘信號(hào)。它由一個(gè)壓片石英晶體和相關(guān)電路組成。晶振的頻率通常以赫茲為單位,例如10 MHz或20 MHz。

外接晶振與外部時(shí)鐘電路之間的關(guān)系是這樣的:外接晶振產(chǎn)生的時(shí)鐘信號(hào)被外部時(shí)鐘電路接收,并進(jìn)一步分配給CPU和其他硬件設(shè)備。簡(jiǎn)而言之,外接晶振是外部時(shí)鐘電路的一個(gè)重要組成部分,用于提供穩(wěn)定的時(shí)鐘信號(hào)。

在這里,我們需要注意的是,雖然外接晶振和外部時(shí)鐘電路都起到了為CPU提供時(shí)鐘信號(hào)的作用,但它們的功能和工作原理有一些不同之處。

首先,外接晶振是一個(gè)獨(dú)立的設(shè)備,其頻率通常固定不變。它的輸出信號(hào)是一個(gè)穩(wěn)定的方波脈沖信號(hào),其頻率由晶振的參數(shù)決定。

相反,外部時(shí)鐘電路是一個(gè)集成在主板或芯片上的電路,它通過(guò)將外接晶振的時(shí)鐘信號(hào)進(jìn)行分頻、倍頻和緩沖等操作,來(lái)產(chǎn)生更高或更低的頻率信號(hào),以滿足特定的系統(tǒng)需求。這意味著外部時(shí)鐘電路可以根據(jù)需要調(diào)整時(shí)鐘頻率,以適應(yīng)不同的CPU和系統(tǒng)配置。

此外,外部時(shí)鐘電路還負(fù)責(zé)將時(shí)鐘信號(hào)提供給其他硬件設(shè)備,例如主板上的其他芯片、內(nèi)存、顯卡等。它必須確保這些設(shè)備都以正確的時(shí)序和同步方式進(jìn)行工作,以實(shí)現(xiàn)高效的數(shù)據(jù)傳輸和協(xié)調(diào)。

最后,外部時(shí)鐘電路還可以通過(guò)增加或減少CPU時(shí)鐘頻率的倍數(shù)來(lái)實(shí)現(xiàn)超頻或降頻。超頻是指將CPU的時(shí)鐘頻率提高到高于其標(biāo)稱頻率的操作,以提高計(jì)算性能;降頻則是將CPU的時(shí)鐘頻率降低以節(jié)省能源或減少熱量產(chǎn)生。

綜上所述,盡管外部時(shí)鐘電路和外接晶振都是為CPU提供時(shí)鐘信號(hào)的重要組成部分,但它們的具體功能和工作原理略有不同。外接晶振負(fù)責(zé)產(chǎn)生穩(wěn)定的基準(zhǔn)頻率,而外部時(shí)鐘電路將這個(gè)基準(zhǔn)頻率進(jìn)行分頻、倍頻和緩沖等操作,以提供給CPU和其他硬件設(shè)備所需的時(shí)鐘信號(hào)。這兩者的協(xié)同工作確保了計(jì)算機(jī)系統(tǒng)的正常運(yùn)行和高效性能。

-

集成電路

+關(guān)注

關(guān)注

5392文章

11624瀏覽量

363192 -

晶振

+關(guān)注

關(guān)注

34文章

2899瀏覽量

68316 -

時(shí)鐘電路

+關(guān)注

關(guān)注

10文章

239瀏覽量

50800

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

晶振的作用:電子設(shè)備的頻率基石

請(qǐng)問(wèn)AFE4400的外接晶振時(shí)鐘能否用外部時(shí)鐘源代替?

LMK00105 HCMOS與LVCMOS晶振的輸出內(nèi)阻是一樣的嗎?

有源晶振與無(wú)源晶振穩(wěn)定性比較:為何有源晶振更勝一籌?

物聯(lián)網(wǎng)系統(tǒng)硬件方案的“心臟”_晶振詳解

晶振的抗干擾設(shè)計(jì):確保系統(tǒng)時(shí)鐘的穩(wěn)定性

如何正確計(jì)算并使用晶振的外接負(fù)載電容

晶振在電路中有什么作用

晶振在物聯(lián)網(wǎng)應(yīng)用中的作用有哪些

CPU的外部時(shí)鐘電路和其外接晶振,作用是一樣的嗎?

CPU的外部時(shí)鐘電路和其外接晶振,作用是一樣的嗎?

評(píng)論