1、I2C 總線介紹

I2C bus是Inter-IC bus的縮寫,意思是IC器件之間的通訊總線;I2C 總線的特點如下:

- 只需要兩個線路,serial data line(SDA)和serial clock line(SCL)

- I2C總線可以支持一主多從或者多主多從的架構;

- I2C總線上的從器件是通過地址來唯一確定的;

- I2C總線是串行,8-bit,雙向傳輸的,支持standard-mode(100Kbits/s)、fast-mode(400kbit/s)、fast-mode plus(1Mbit/s)、high-speed mode(3.4Mbit/s)

- I2C總線上可以掛載的器件數量只受最大總線電容影響;

2、I2C總線的電氣設計

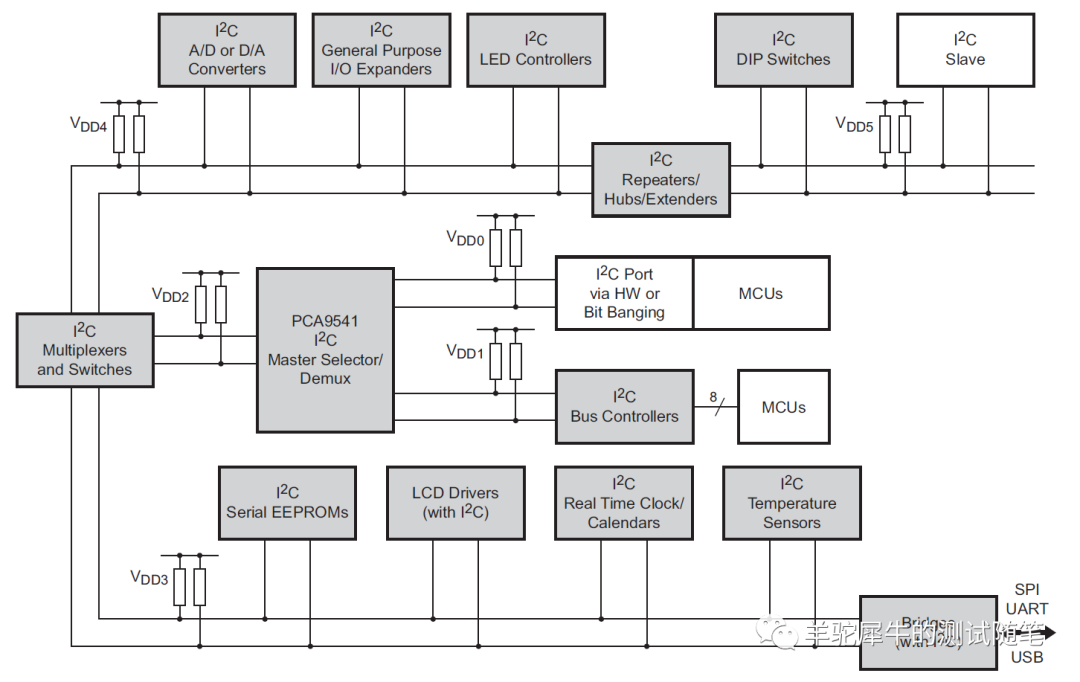

上圖展示了I2C的電氣連接架構

- 所有I2C器件通過SDA和SCL連接到總線上

- I2C總線不同電平總線要分別接電阻上拉至當前電平值

- 不同總線電平的I2C器件通過雙向電平轉換器(Switches)作為電平轉換

2.1 電平轉換的基本邏輯和原理

如上圖所示,主要有3種狀態:

- 雙邊器件均不下拉總線(輸入輸出為高)。3V3部分線路上拉,這樣的話MOS的G和S極都是3V3,Vgs小于導通電壓,MOS不導通;如此一來,雙邊器件均保持其對應電平值的高電平。

- 3V3器件下拉總線到低電平。MOSFET的S極變低,而MOS的G極電平是3V3,Vgs大于閾值MOS導通;5V器件總線電平通過MOS被拉至低電平,最終實現低電平的輸出輸入。

- 5V器件下拉總線至低電平。MOS的D極電壓降低直至比S極電壓低的時候,MOS內置的漏極-基底二極管導通,MOS管的S極也就是3V3總線電平開始下降,當S極電平下降到Vgs大于閾值電平時,MOS管導通,S極電平和D極電平一致被拉到低電平;從而實現了高電平器件輸出到低電平器件輸入。

2.2 上拉電阻

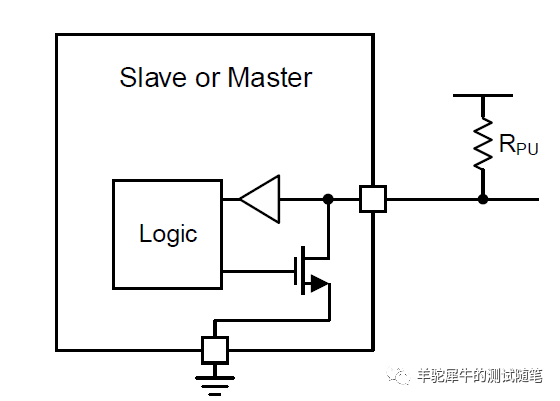

- I2C端口為開漏輸出(區別于常見IO的推挽輸出),即其IO口輸出是通過控制MOS管打開與關斷來將漏極上的電平進行輸出,所以沒有高電平輸出能力,必須將總線上拉至總線電平來實現高電平輸出。

- 開漏輸出低電平的實現如下圖所示:

- 開漏輸出高電平的實現如下圖所示:

2.2.1 上拉電阻的阻值如何選擇

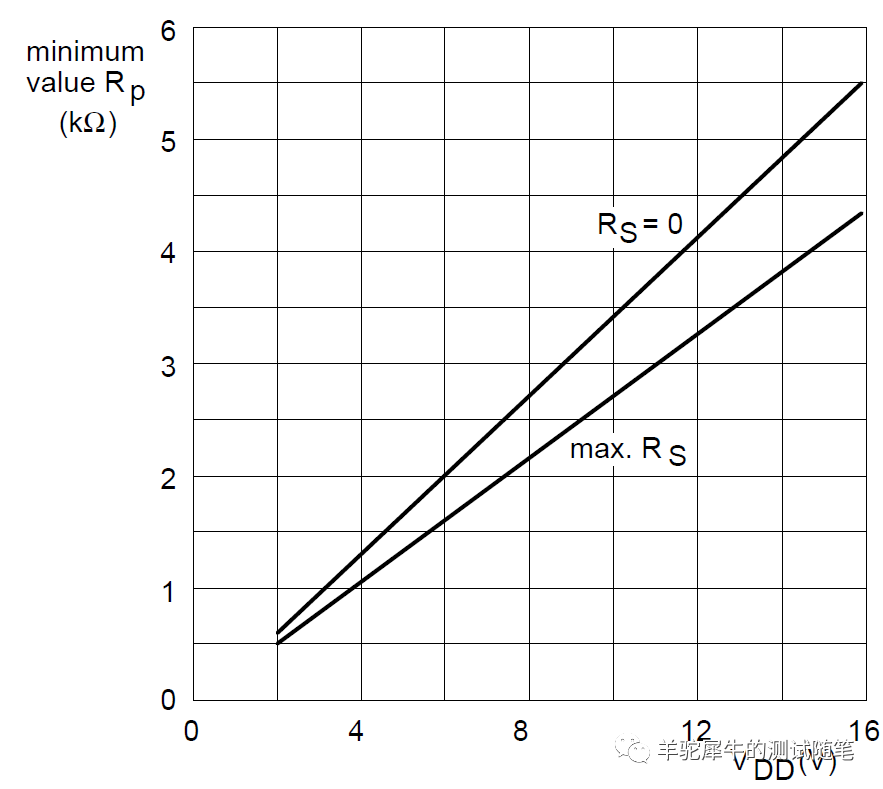

- 眾所周知,電阻是能耗器件,所以肯定是盡可能使得電阻上的功率損耗越小越好,即電阻在此條件下是個最小值

Rp(min)=(Vcc-Vol(max))/Iol

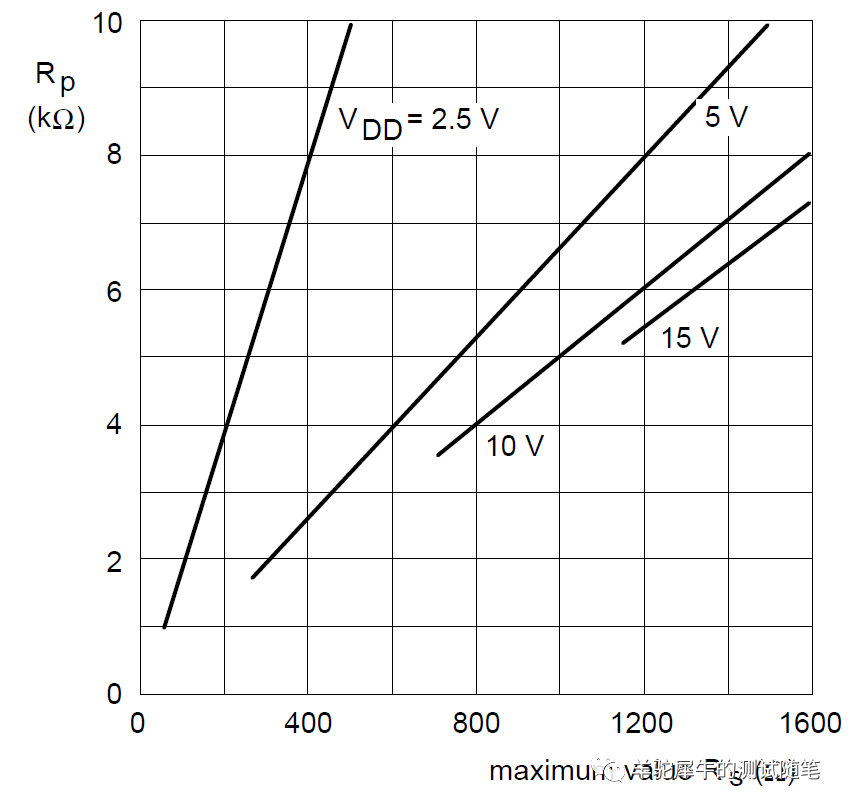

Vcc:上拉電平 ,Volmax):總線輸出為低電平的最大電壓值 ,Iol:總線的驅動電流(Vol狀態下) - 上拉電阻Rp還會受信號上升時間約束,一般datasheet上有明確的最大上升時間要求,若超過這個值,有可能信號還沒上升至高電平就開始下降,導致信號采樣出錯;

Rp(max)=tr/(0.8473 Cb)

tr:上升時間,Cb:總線電容(線路、連接和管腳的總電容)

推導公式如下:

參考一階電路的電壓隨時間的變化公式 V(t)=Vcc (1-e^(-t/RC))

上升下降時間一般波形的30% - 70%,這是因為輸入低電平最大值門限一般0.3Vcc,輸入高電平門限一般0.7Vcc(不是絕對,參考芯片Datasheet)

當Vih=0.7*Vcc時,Vih=0.7*Vcc=Vcc*(1-e^(-t1/Rp*Cb))

當Vih=0.3*Vcc時,Vih=0.3*Vcc=Vcc*(1-e^(-t2/Rp*Cb))

上升時間即為:tr=t2-t1=0.8473Rp8Cb - 最終根據計算出來的Rp范圍內選擇一個合適阻值

注意:

實際電路設計中,總線上會掛載不止一個器件,這就要綜合多個器件的參數進行計算,進而選擇一個適合所有器件的值 - 除了上拉電阻Rp,有時在器件連接到總線上時會串入一個電阻Rs,這個電阻主要作用是消除高壓毛刺;Rs跟Rp的關系如下圖所示,Rs的值可以參考,若實測總線上沒有高壓毛刺,那Rs可以去掉;

3、I2C的數據幀結構

起始位:開始狀態位,1bit,SCL為高時SDA由高至低的過程稱作起始位;還有一種重復起始條件,指的是主機對于同一個從器件進行同一操作的時候,不需要先發送停止條件結束總線,再開始;

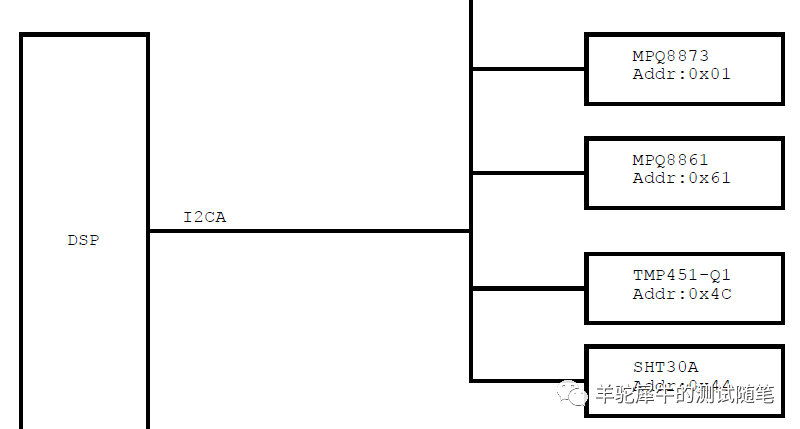

地址位:7bit,是當前總線需要訪問的器件地址;特殊的情況是10bit,一般不用。7bit地址里一般前四位是由器件類型定死,我們自己可以配置的是低三位,也就意味著,同類型的器件在同一根總線上最多可以掛載8個;

讀寫操作位:1bit,0代表寫,1代表讀;

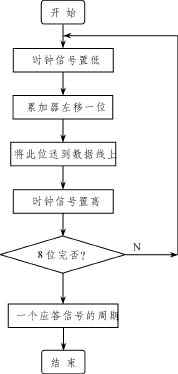

應答位:1bit,低電平,每8bit之后跟一位應答位,表示接收端接收成功;還有一種非應答位(NCK)高電平,表示終止傳輸。

數據位:8bit,一個字節后面必須跟著一個應答位;一般數據的第一個字節傳輸的是要操作的寄存器地址,后面字節是要寫入或者讀出的數據。

停止位:當SCL為高電平時,SDA總線由低電平向高電平切換表示停止條件

- 起始和停止條件一般由主機產生。總線在起始條件之后被認為是忙碌的狀態;在停止條件的某段時間之后,總線被認為再次處于空閑狀態。重復起始條件跟起始條件一樣,后續總線會處于忙碌狀態;

- SDA線上數據必須在SCL高電平周期保持穩定,也就是說SDA數據高低狀態變化只能發生在SCL低電平的時候;

4、I2C的時鐘同步與仲裁

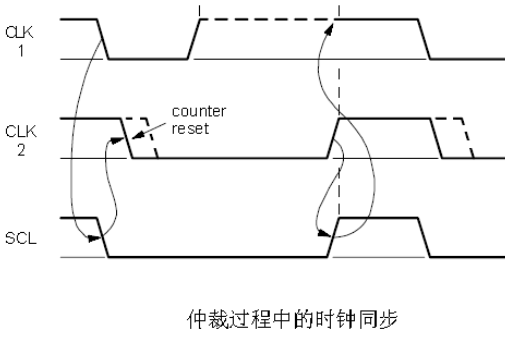

- 同步:所有主機在SCL上產生他們自己的時鐘來傳輸I2C總線上的報文。數據只有在SCL高電平周期有效,因此需要一個確定的時鐘進行逐位仲裁。

- 如下圖所示,多個主機在同一個總線上產生自己的時鐘信號;SCL線被有最長低電平周期的器件保持低電平,此時低電平周期短的器件會進入高電平的等待狀態;所以,低電平周期由低電平時鐘周期最長的器件決定,高電平周期由高電平周期最短的器件決定。

- 仲裁:

主機只能在總線空閑的時候啟動傳輸。兩個或多個主機在起始條件的最小持續時間內產生一個起始條件;

當SCL為高電平時,仲裁在SDA線上發生;在其他主機發送低電平時,發送高電平的主機將斷開他的輸出,因為總線上電平與自己電平不一致。

5、I2C與CBUS的兼容

C-BUS接收器可以連接到標準的I2C總線。但是必須連接第三條叫DLEN的線,而且要省略響應位。通常I2C的傳輸是8位的字節傳輸,兼容C-BUS的器件有不同的格式。在混合總線中,想要訪問操作C-BUS器件,需要發送特定的C-BUS地址(0x0000001x);發送C-BUS地址后,DLEN線被激活,發送C-BUS格式的報文,如下圖所示:

-

二極管

+關注

關注

147文章

9706瀏覽量

167583 -

MOSFET

+關注

關注

147文章

7242瀏覽量

214278 -

上拉電阻

+關注

關注

5文章

363瀏覽量

30734 -

電平轉換器

+關注

關注

1文章

179瀏覽量

19621 -

I2C總線

+關注

關注

8文章

406瀏覽量

61173

發布評論請先 登錄

相關推薦

I2C總線原理詳解

基于CPLD的I2C總線接口設計

I2C總線信號與測試案例(一)

I2C總線信號與測試案例(一)

評論