一、SerDes簡要介紹

1、概述

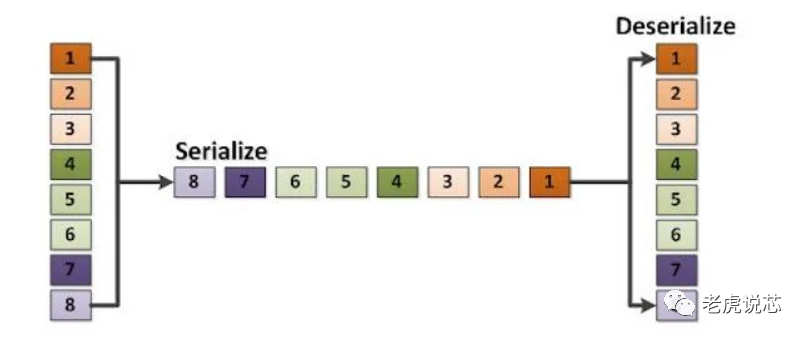

SerDes是SERializer(串行器)/DESerializer(解串器)的簡稱,是一種主流的時分多路復用(TDM)、點對點(P2P)的串行通信技術。發送端將多路低速并行信號轉換成高速串行信號,經過傳輸媒體(光纜或銅線),在接收端高速串行信號重新轉換成低速并行信號。這種點對點的串行通信技術充分利用傳輸媒體的信道容量,減少所需的傳輸信道和器件引腳數目,提升信號速度,從而大大降低通信成本。

隨著電子行業技術的發展,特別是在傳輸接口的發展上,傳統并行接口的速度已經達到一個瓶頸,取而代之的是速度更快的串行接口,于是原本用于光纖通信的SerDes技術成為了高速串行接口的主流。串行接口主要應用了差分信號傳輸技術,具有功耗低、 抗干擾強,速度快的特點,最高傳輸速率可達10Gbps以上。

在SerDes流行之前,芯片之間是通過系統同步或源同步并行接口來傳輸數據的。SerDes的優點:更少IO數量,更小封裝,更少走線,更低成本;有效降低電磁干擾,有效降低噪聲和串擾。SerDes的劣勢:系統的設計復雜程度高,需要更高性能材質的通道。

幫助SerDes實現更高速高帶寬的技術主要有:多路復用/差分/時鐘數據恢復/鏈路均衡。

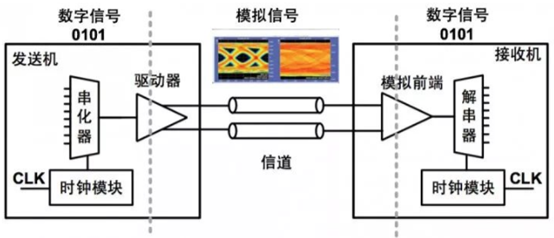

圖1 Serdes電路的示意圖

圖1可以看出,SerDes是一種數模混合芯片,成對使用。

2、serdes的技術原理

提升數據傳遞效率,總體上有兩種方法:提高頻率/帶寬,提高帶寬/頻譜利用率。

信息技術的早期,數據傳輸主要用低速串口,為提高帶寬,出現了低速并口(因為早期技術和硬件無法支持更高的頻率和帶寬)。隨著并口技術的發展,干擾和噪音問題逐漸凸顯,并口傳輸速度的瓶頸也逐漸到來。為此,又出現了“高速串行HSS“技術,逐漸用于通信、顯示、消費電子等領域;SerDes就是一種可以集合串口和并口的技術。狹義的SerDes是一種物理概念,是一種在發送端將并行數據轉換為串行數據,在接收端將串行數據恢復為并行數據的電路。

串-并轉換的實現是基于信號復用技術的成熟。

信號復用是指在傳輸路徑上綜合多路信道,然后恢復原機制或解除終端各信道復用技術的過程。當前最常見的是時分復用、頻分復用、波分復用、碼分復用四種。

時分復用是將一條物理信道按時間劃分為不同的時間片段,分配給多個信號使用。即,每一個信號在不同的時間上占用同一個信道;

頻分復用是指將物理信道按頻率劃分為不同的虛擬信道,使多信號共同傳輸;

波分復用是按波長劃分,是頻分的一個分支;碼分時按碼型/地址劃分;時分復用和頻分復用在SerDes領域更常見;

復用技術使得多個并行信號在串口中傳輸成為可能,進一步提高了效率。

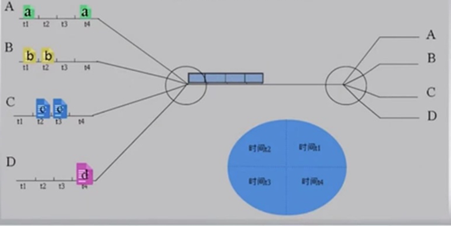

圖2-1 時分復用示意圖

圖2-2 波分復用示意圖

上圖為光通信領域,信號“復用”的示意圖。

為進一步發揮SerDes的優勢,還會用到名為“低電壓差分信號“的技術,以更進一步提升帶寬。差分信號由一對相反信號組成,接收端以兩者的大小關系來識別“0“和”1“,信號在傳輸過程中即使受到干擾,大小關系也不會發生變化,保持了傳輸信號的完整性。差分信號有三種:低電壓差分信號(LVDS)、低電壓偽射級耦合邏輯(LVPECL)和電流模式邏輯(CML),目前在SerDes領域較常見的是LVDS。

3、信號的數模轉換

所有信號,在傳輸時都是以模擬信號的形式傳遞。我們日常所說的“數字信號”“模擬信號”是指信號的處理形式。因為二極管的工作原理,顯而易見地,數字信號更容易被計算機處理。

數字信號轉換為模擬信號,是通過調幅或者調頻加到一個正弦波(一般稱為“基帶信號”)上面,這樣調制后的攜帶信息的波就已經不是一個固定頻率的正弦波了,這個調制后的波稱為“載波信號”,就是我們想要的信息。數字轉換為模擬的電路稱為DAC。

模擬信號轉換為數字信號,可以簡單記憶為:采量編,采樣、量化、編碼。模擬轉換為數字的電路稱為ADC,ADC的過程可看作是DAC的逆過程。

ADC的指標主要有分辨率(又名精度)和采樣率(又名轉換速率)兩項。分辨率用“位”來形容(可以理解為小數點的位數)。目前最初級的是8位的,常見于單片機。分辨率的位數越高,采樣越準確,單點的采樣值越接近真實值。采樣率越高,還原數據的能力就越強。

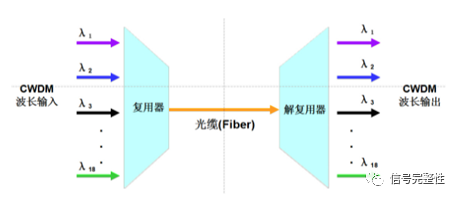

圖3 模擬信號-數字信號轉換

圖片截取自B站up主“郭天祥老師”《AD/DA數模轉換介紹》

以三位ADC為例介紹ADC的大致工作過程:

三位,就是2的三次方,即均分8等份。假設模擬信號的峰值電壓為1V,則每0.125V作為采樣間隔。0.125V就被稱為LSB(least significant bit最低有效位)。小于0.125V的,轉換為數字時統一記為“001”(對應十進制為1),0.125-0.25V,轉換為數字時統一記為“010”(對應十進制為2),以此類推。最終完成模擬信號向數字信號的轉換。

二、SerDes的重要概念和技術

1、碼元

理解SerDes的傳輸過程,需要引出“碼元”的概念。

一個碼元就是一個脈沖信號,即一個最小信號周期內的信號。我們都能夠理解,最簡單的電路,以高電平代表“1”,低電平代表“0”。一個代表“1“或“0“的信號,就是一個碼元。

信號可以傳遞信息主要是因為信號有頻率,振幅,相位,波長,周期,其中頻率/波長/周期三者有相關性,因此可以認為,頻率、相位、振幅使信號可以傳遞信息,其中最常見的是振幅(電平)。所以,有沒有可能讓一個碼元/脈沖信號攜帶的信息量是2或是4bit呢?

答案是肯定的。一個碼元可以包含多個bit數據,包含的bit數稱為碼元的寬度。比特率是指一秒鐘可以發送多少bit的數據,波特率是指一秒鐘可以發送多少碼元。當一碼元攜帶2bit數據,那么比特率=波特率的2倍。

一個二進制信號,比如0或1,就是1bit。現在有8bit數據,如果用二進制碼元(一次只運送一個比特),需要在信道上傳輸八次脈沖信號,如果用四進制碼元(一次能運送2個比特),需要在信道上傳四次脈沖信號……因此碼元攜帶比特越多,傳輸的脈沖信號次數越少,傳輸速度就越快。

2、NRZ和PAM

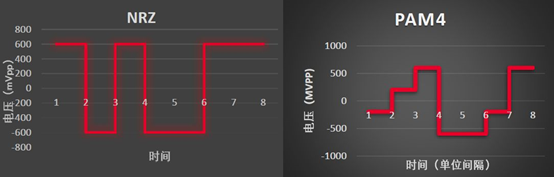

理解了碼元的概念和意義后,就能夠較好理解NRZ和PAM。NRZ和PAM是信號傳輸方式。

NRZ:Non-Return-to-Zero,不歸零編碼;可以把NRZ看作PAM2,一個碼元只有1bit信息,即,只代表0或1。

PAM:Pulse AmplitudeModulation,脈沖幅度調制。常見的有PAM4,PAM8,PAM12等。PAM4即第四代脈沖幅度調制,目前最成熟,是指一個碼元包含2bit信息。PAM4的波形一共有4種,見下圖,可分別定義為:00,01,10,11。

圖4 NRZ與PAM

以十進制下的邏輯數字“9“為例,”9“對應的二進制為”1001“,當使用NRZ時,需要的碼元數量為4,“1”“0”“0”“1”依次傳輸;當使用PAM4時,需要的碼元數量為2,“10”“01”兩個碼元依次傳輸。這樣,在信號頻率不變的情況下,信道帶寬/傳輸能力提高了一倍。

可以通俗理解為,PAM4之于NRZ相當于在車速不變的情況下(頻率不變),車道數量增加一倍。原理上也有些類似于前述提到的“信號復用”。

從以上原理可知,PAM的本質是將信號的幅度做更大密度的利用,這就對信號發射和接收,以及編碼和解碼過程,提出了更高的要求。

NRZ需要信號頻率高,但是電路結構相對簡單,而且數模轉換過程簡單。相同帶寬下,PAM4需要的信號頻率是NRZ的一半,如果是PAM6、PAM8等,信號頻率可以更低。所以,PAM需要的信號頻率低,但是電路結構相復雜,而且數模轉換過程復雜,需要消耗更多功率,而且成本也更高。同樣因為電路復雜,PAM的延遲也大于NRZ。

因此,NRZ還是PAM,各企業都會選擇最適合自身的路線。所以,也會有企業選擇多通道/低信號頻率的方式實現高帶寬。比如,光通信領域的100G產品,業內既有PAM4的單通道光模塊,也有4通道,每通道為25G的NRZ光模塊產品。

3、時鐘

簡單的來講,時鐘信號就是由電路產生的具有周期性的脈沖信號,被用來為系統中多個同步執行的電路之間、為不同系統之間的數據傳輸提供參考基準。微處理器的指令執行也都是在時鐘的節拍下進行操作的。時鐘信號的作用就像交響樂團的指揮;或是龍舟上的鼓手。

生活中能見到的最原始的時鐘信號:石英表,用到的原理是晶振效應。晶振效應是指,晶體以一定角度切割為兩部分,兩側加電壓,晶體就會以固定的頻率震動,而頻率不受外界環境影響。晶振有一個頻率,用這個頻率來計時,夠一秒鐘的時候發一個驅動信號給電機,電機帶動秒針跳動一下,這就是最原始的石英表。

目前晶振/時鐘信號已經廣泛應用于電信領域。很多電路/信道中都會同步傳遞時鐘信號。

而時鐘信號在SerDes領域使用時,存在一個非常嚴重的問題:時鐘與數據并行傳輸時,無法達到1Gb/s以上的帶寬。超過這個帶寬,會出現非常嚴重的時鐘信號偏移。而目前常見的SerDes,車端已經基本在2Gb/s以上,通信用serdes已經達到100-200Gb/s。

于是,人們研發出了在serdes信道內只傳輸串行數據,而不傳輸時鐘信號;在接收端進行時鐘數據恢復的技術,即CDR,Clock and Data Recovery,時鐘數據恢復。CDR技術目前已經廣泛應用于SerDes、以太網、PCI-Express、Aurora等領域。

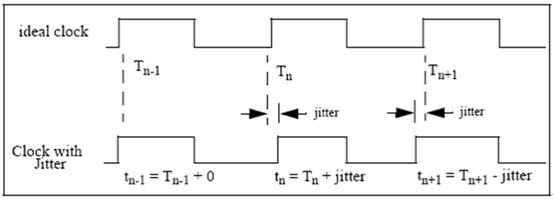

再詳細介紹下為何需要做時鐘恢復:

假設輸入信號是規整的,每個碼元的時間間隔都是完全一樣的,類似下圖:

圖5-1 規整碼元(每個冰墩墩看作一個碼元)

經過傳輸后,可能因為線路中各種噪音的影響,或是其它各種原因,導致接收端的碼元不再是規整的,類似下圖:

圖5-2 不規整碼元(t2>t1)

因為SerDes的所有電路都使用統一的參考時鐘,所以圖5-2所示的碼元是沒辦法被接收端處理的,或是會存在誤判,因此需要對其進行恢復,使之重新成為圖5-1的狀態。這就是CDR的意義。具體的恢復過程稍微復雜,在此不做詳細介紹。

CDR技術還使得不需要單獨布設時鐘信號線,減少布線沖突,節省成本,降低電路/網絡設計難度。

4、CDR和DSP

CDR已經在上一部分做了簡要介紹。CDR主要是用模擬電路的處理方式,對時鐘做恢復,即在圖1中,接收端先對傳輸過來的模擬信號進行時鐘恢復,再轉為數字信號。

那么,可否先轉為數字信號,再恢復時鐘呢?答案也是可以的。用到的處理電路,就是DSP。

DSP用于SerDes,初衷并不是為了做時鐘恢復,而是因為PAM4及以上的傳輸方式下,碼元的處理較為復雜,需要由DSP完成。然后因為DSP有更好的數字處理能力,所以除了提供CDR能提供的時鐘恢復功能之外,還可以進行色散補償操作,去除噪聲、非線性等干擾因素,對于整個電路的提升是優于CDR的。

DSP的短板在于,因為處理更復雜,所以功耗更高,成本也更高,而且DSP的延時也要長于CDR。

目前業內的主流觀點認為,DSP更適合長距或中長距,CDR可能更適合短距或中短距。用于SerDes的DSP主要是16nm及以下的方案,研發費用較高,需要有較大的出貨量來平攤。產業界內,單通道最高數據率大于30 Gbit/s以上,通常考慮采用PAM4+DSP的方案,以下使用NRZ+CDR。筆者了解到,已經有業內企業在研發新的CDR技術用于替代現有的DSP方案,用于PAM,最終實現低成本和更好的可操作性。

CDR的方案包括:基于數字PLL的CDR,基于相位插值的CDR,基于電荷泵和模擬濾波器的CDR等。其中后兩者被更多認為屬于模擬電路。而DSP被認為是完全數字電路。

關于CDR、DSP在SerDes領域的應用,以及與NRZ、PAM的搭配關系,與國外相比目前國內的相關研究還不夠深入,國內能夠獲取的資料也還較少。

5、包頭和包尾

通信領域,數據包頭一般用于識別一幀(包)的開始。包尾的作用較多,如果是固定長度的包,可以是做校驗位等。或者是用于標識一幀的結束。

筆者認為,警匪片里“洞幺,我是洞拐”,這個就可以認為是包頭,“XXXX,over”這個“over”可以看作“包尾”。

理論上來說,SerDes不分拆壓縮成包,輸入端接收到什么就傳輸什么,這是SerDes可以實現實時、無損傳輸的重要原因。相比之下,以太網受到帶寬限制,需要分拆、壓縮成包,然后對壓縮包進行傳輸。

SerDes理論上不存在包頭包尾。但是芯片內部根據不同的設計需要會加入包頭或者包尾進行校驗或者分包,比如4合一的SerDes芯片,在芯片內部就需要進行區分哪個通道的數據,這個時候,芯片內部就需要做類似包頭的操作;另外為了校驗數據,會增加額外的類似于包尾的開銷。

因此,SerDes的包頭包尾和以太網等的包頭包尾有一定區別。尤其當使用CDR時,SerDes的包頭包尾中還必須包含特殊的比特序列,這進一步增加了serdes電路的復雜度。

除此之外,SerDes用到的重要技術還包括前向糾錯(FEC)、循環冗余校驗(CRC)、誤差校正碼(ECC)、鏈路均衡、預加重、多重相位技術、線路編解碼等,多通道SerDes還會用到通道綁定。而SerDes信道內傳輸電信號和傳輸光信號,也有很多差別。受篇幅所限,此處不做過多展開。

三、serdes的抖動與噪聲

1、抖動概述

ITU-T G.701標準對抖動的定義為:“抖動是指數字信號在短期內重要的瞬時變化相對于理想位置發生的偏移”。噪聲、非理想電路、非理想信道,都是抖動產生的原因。

圖6 抖動示意圖

抖動可以分為隨機性抖動(RJ-Random Jitter)和確定性抖動(DJ- Deterministic Jitter)。RJ的噪聲源、串擾源很多,產生的原因很復雜。隨機抖動滿足正態分布,一般很難消除;DJ是由可識別的干擾信號造成的,這種抖動通常幅度有限,具備特定的(而非隨機的)產生原因,它是可重復可預測的。信號的反射、串擾、開關噪聲、電源干擾、EMI等都會產生DJ。

DJ又可以主要分為周期性抖動(PJ)、數據相關抖動(也有叫數據依賴型抖動,DDJ)和占空比抖動(DCD)三種。

PJ由電路上周期性干擾源導致。比如開關電源的開關頻率,時鐘信號的串擾等。PJ不能被均衡器校正。

DDJ是由于不理想的信道導致。是可以被均衡器校正的抖動。

DCD因差分信號的正端負端的偏置電壓不一致,或者上升沿和下降沿時間不一致會導致占空比失真。DCD和數據pattern相關,是可以被校正的抖動。

除抖動外,SerDes面臨的挑戰還包括:電磁干擾、衰減、插入損耗等。其中,抖動、電磁干擾、衰減的大小基本與信號頻率成正相關性。

抖動的分析和校正,主要用到概率統計與分析等各種數學手段。因為現實中的抖動很多是多個抖動的疊加,而每個單項抖動又可能有多項干擾源,所以SerDes領域抖動的難點在于如何準確找到抖動的干擾源并制定有效的干預/補償手段。

2、抖動與噪聲的區別

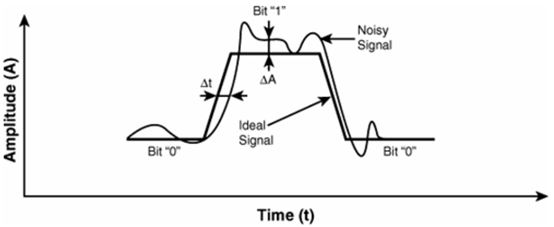

筆者在了解SerDes,了解通信原理的過程中,很長一段時間都無法搞清楚抖動和噪聲的區別。乍一聽起來,二者都是用來描述信號偏離的現象。實際上,抖動和噪聲是對同一類物理現象的兩種不同表述方式,或者叫不同的數學表達式。二者甚至可以進行變換。

真實信號和理想值的偏離,分兩個方面:信號幅度的偏離,稱之為幅度噪聲,簡稱噪聲;時間的偏離,稱之為時序抖動,簡稱抖動。幅度噪聲是一個持續的過程,時刻影響整個系統,時序抖動只是在邊沿跳變時影響系統。

或者這樣理解:抖動是一個時間域的概念,而噪音是一個頻率域的概念。抖動是對信號時域變化的測量結果,它從本質上描述了信號周期距離其理想值偏離了多少。

圖7 抖動與噪聲

上圖可以比較清晰的理解抖動與噪聲的區別。“Δt”是抖動,“noisy signal”是噪聲。

通過以上內容我們可以理解,抖動/噪聲是無法完全消除的,干擾源也非常多,包括電路設計,PCB的布局布線,半導體器件自身,甚至電子和空穴特性都可能產生抖動/噪聲。而且隨著信號頻率/帶寬/分辨率越高,抖動/噪音帶來的影響可能就越大,盡力減小抖動/噪音的必要性就越大。

另一個比較讓人難受的問題是,由于SerDes采用了差分信號,即在一個信道內錯頻收發傳輸,兩個反向信號可能會互為干擾。這極大增加了減少抖動/噪聲的難度。

抖動與噪聲的數學變換稍顯繁瑣,在此不做介紹。

審核編輯:劉清

-

電磁干擾

+關注

關注

36文章

2330瀏覽量

105644 -

串行通信

+關注

關注

4文章

579瀏覽量

35581 -

TDM

+關注

關注

0文章

57瀏覽量

15677 -

串行器

+關注

關注

0文章

116瀏覽量

14470 -

SerDes

+關注

關注

6文章

201瀏覽量

35042

原文標題:SerDes簡介

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

了解SERDES基礎概念,快速進入高速系統設計

GMII、SGMII和SerDes的差異總結

車載SerDes技術概述、特點和應用詳解

請問6678中的srio的serdes和以太網的serdes是共用還是各自有自己的serdes?

SerDes是怎么工作的

SERDES的優勢 SERDES演變的看法

SerDes是什么?SerDes功能和特性概述

SerDes是怎么設計的?(一)

SerDes的技術原理 SerDes的重要概念和技術概述

SerDes的技術原理 SerDes的重要概念和技術概述

評論