**1 **電源系統

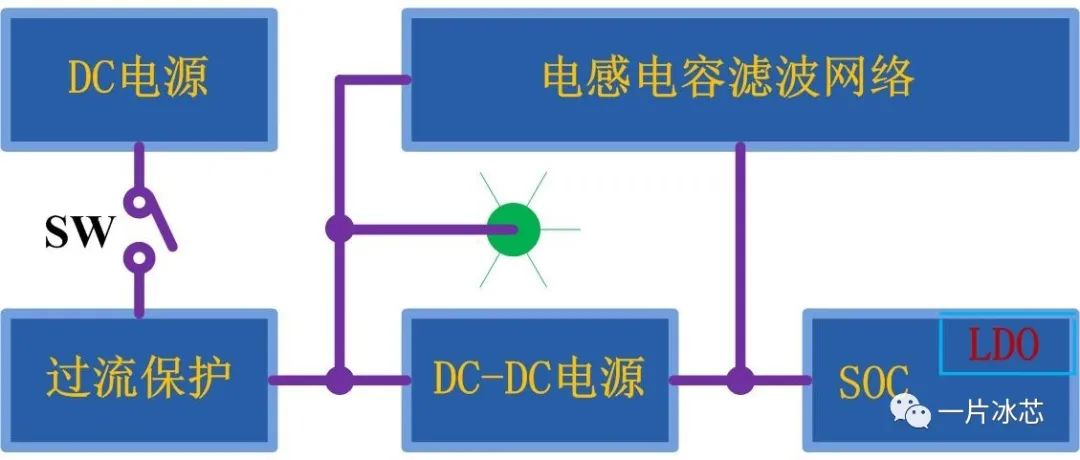

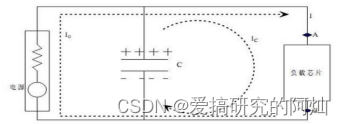

圖1是我畫的一個完整的電源系統,其中DC電源可以是你筆記本電腦的電源適配器、手機電池或者紐扣電池等,DC電源經開關SW到PCB板上的過流保護,然后送到DC-DC電源(升壓/降壓),DC-DC電源的輸入和輸出都需要電感電容濾波,濾波后的電壓再送到芯片(SOC)內部。圖中綠色小太陽圖案代表電源指標燈,LDO表示芯片內部電源。

- 例如一個手機板級系統包括內存、Flash、CPU、GPU、基帶處理器等,每種芯片對電源的需求不同,有的要低壓,有的要高壓,有的要高性能(模擬電路),有的要高速度(數字電路),有的既要高性能又要高速(模數混合電路),我們的電源系統就是來完成這個任務的。

Fig1. 完整的電源系統

現代集成電路芯片電源電壓一般為3.3V/2.5V/1.8V/1.5V/1.2V/1.1V/1.0V/0.9V /0.8V/0.6V/0.5V,換句話說圖1中DC-DC電源輸出或者SOC輸入電壓為以上幾種。實際應用中無論是wireless還是wireline產品電源都不低于3.3V,因此往往需要降壓型的DC-DC電源,我們可以選用TI公司的LMZ12002和PTD08D210W,兩種芯片的Spec如圖2所示。

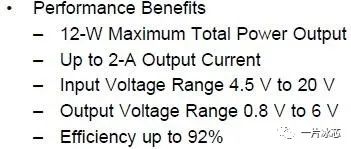

(a)LMZ12002的Spec

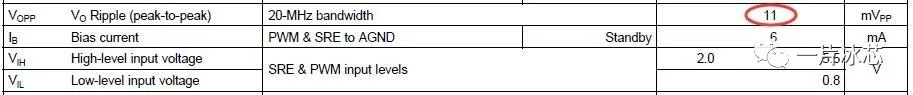

(b)PTD08D210W的Spec

Fig2. LMZ12002和PTD08D210W的Spec

其中圖2(a)給出了LMZ12002輸入電壓范圍為4.5-20V,輸出電壓范圍為0.8-6V,最大輸出電流為2A,效率最高可達92%,最大8mV輸出電壓紋波。

其中圖2(b)給出了PTD08D210W輸入電壓范圍為4.75-14V,輸出電壓范圍為0.7-3.6V,最大輸出電流為10A,效率最高可達96%,最大11mV輸出電壓紋波。

TI公司DC-DC芯片寬輸入范圍降低了圖1 DC電源的要求,DC電源可選用6V、8V、12V等典型電壓,實際應根據你的應用場景來合理配置DC-DC的輸出電壓使其能達到最好的性能和最高的效率。

DC-DC電源內部一般都包含一個振蕩器,振蕩頻率在幾百kHz到幾十MHz,并且輸出電壓會產生幾mV(如LMZ12002輸出電壓紋波為8mV)到幾十mV(如PTD08D210W輸出電壓紋波為11mV)的電壓紋波。4G基帶信號帶寬為20MHz,mm-Wave5G最大Channel帶寬可達400MHz,高速SerDes數據率已經做到了112Gbps,有些應用場景GHz的電源噪聲干擾也不得不考慮。這些因素就對芯片內部LDO的電源電壓抑制比提出了要求。

**2 **片上電源

2.1 背景

片上電源英文應該叫fully-integrated low-dropout regulator(LDO),當然前邊介紹的DC-DC也是一種電源,本期不做重點介紹。

前邊介紹的DC-DC是板級系統的第一級電源,翻看LMZ12002和PTD08D210W用戶手冊我們可以得到DC-DC電源的效率基本可以保證在80%以上,最高可達96%,高的電壓轉換效率是板級電源系統第一級采用DC-DC的最主要原因。LDO效率一般為輸出電壓除以輸入電壓(略小于),如輸入電壓為3.3V,輸出電壓為0.8V,效率小于24.2%,為了提高效率應盡量減小輸出與輸入的電壓差。

LDO可以產生低噪聲、快速響應、高電源電壓抑制比(PSRR)的內部電源,因此在高性能模擬電路、快速響應的高速數字電路中LDO不可或缺。

文獻[1-5]給出了幾種LDO的應用場景,如圖3所示。

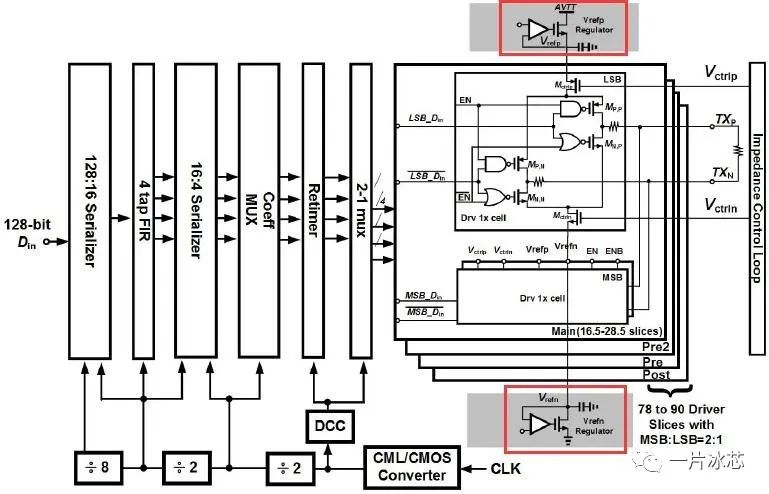

(a)文獻[1]LDO的應用

(b)文獻[2]LDO的應用

(c)文獻[3]LDO的應用

(d)文獻[4-5]LDO的應用

Fig3. 文獻[1-5]LDO的應用

圖3(a)-(b)應用在了電壓模PAM4 Transmitter,速度分別為56Gbps和112Gbps,用于提供穩定及快速響應的電源。圖3(c)用于LCVCO,用于產生低噪聲和高電源電壓抑制比的電源。圖3(d)用于高速光通信前端系統中的transimpedance amplifier,用于產生高電源電壓抑制比和快速響應的電源。其中文獻[4-5]為同一結構,于2014年發表在了ISSCC會議上,次年發表在了TCAS-I期刊上。下面章節我們以圖3(d)為例詳細分析一下LDO設計時應注意的問題。

2.2 注意事項

一個典型的LDO一般包括兩個低頻極點,一個位于功率管柵端一個位于輸出端,這是因為功率管柵端往往接在誤差放大器(EA)的輸出,具有較高的輸出阻抗和大的寄生電容,Capacitor-less LDO輸出一般會掛有pF級的電容,導致輸出極點也處于較低的頻率,當然片外電容LDO輸出端極點頻率會更低。

LDO是一個負反饋環路,因此在動手設計一個LDO時應考慮把主極點位置放在什么位置,因為極點的位置會影響環路穩定性。如果把主極點位置放在輸出端,重載時單位增益帶寬和主極點頻率都會增大,當單位增益帶寬接近第一非主極點位置時相位裕度會減小,穩定性降低。如果把主極點位置放在內部,需要密勒補償將內部極點頻率推到很低以免在輕載時次極點接近主極點,進而限制環路穩定性,過程如圖4所示。

Fig4. 典型LDO輕載重載模式下極點分布

2.3 實例

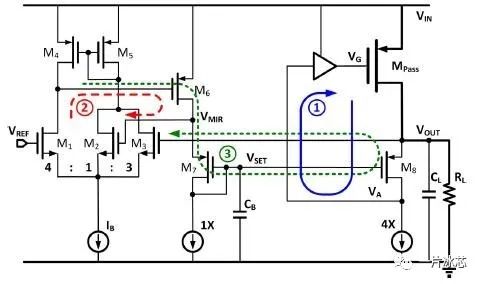

文獻[4-5]是一個1.2V轉1.0V的LDO,提出了一種采用Flipped Voltage Follower(FVF)及Buffer Impedance Attenuation(BIA)技術的三環Capacitor-less的LDO,其特點是整個頻帶范圍內PSRR小于-12dB且具有快速響應,原理圖如圖5所示。

Fig5. 片上三環LDO原理圖

這個結構跟我之前介紹的FVF結構的LDO類似,區別是該結構采用BIA技術將輸出級的快速響應環路的內部極點推到了高頻(GHz)處,使得輸出級的快速響應環路帶寬達到600MHz。合理設置三輸入EA(圖5中M1-M3)M2和M3的比例可實現輸出端(圖5 V OUT )DC電壓精度及環路穩定性之間最優值。M11在輕載和重載時設置在亞閾值或臨近亞閾值區以得到最大的gm,從而將圖5 Buffered FVF環路極點推到高頻。

三個環路標注在了圖6所示的結構圖,環路1提供快速響應和較低的環路增益,環路2 DC增益大,帶寬小可將VREF精確復制到VMIR或V SET ,環路3由VOUT反饋到三輸入誤差放大器M3的柵端提高了VOUT的DC精度。三個環路各司其職產生一個具有快速響應和全頻帶范圍內高PSRR的高精度電壓。

Fig6. 片上三環LDO結構圖

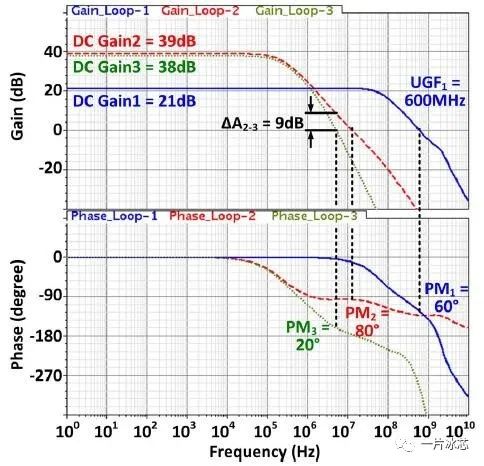

圖7給出了重載模式下三環路的幅頻和相頻特性曲線。環路3相位裕度只有20度,這似乎影響了環路穩定性,但考慮到環路2和環路3共用一個誤差放大器,環路穩定性要看整體的,只要環路2和環路3整體相位裕度夠大就行,不用在意整體環路中的某一環路相位裕度不夠大(就像有些帶隙基準或constant-gm偏置中允許存在正反饋一樣,只要正反饋小于1且整體是一個負反饋環路就沒有問題)。

Fig7. 重載模式下的幅頻和相頻特性曲線

**3 **思考與討論

該結構輸出端接有140pF電容,在該光通信接收端的應用中是否有必要在片上集成如此大的電容?該應用中是否要考慮放大器的噪聲?

-

振蕩器

+關注

關注

28文章

3847瀏覽量

139364 -

輸出電壓

+關注

關注

2文章

1122瀏覽量

38299 -

SoC芯片

+關注

關注

1文章

617瀏覽量

35041 -

電源系統

+關注

關注

3文章

628瀏覽量

37900 -

DC-DC電源

+關注

關注

2文章

64瀏覽量

17762

發布評論請先 登錄

相關推薦

PCB電源供電系統的分析與設計

Android Framework電源子系統的分析

嵌入式系統電源芯片選型與應用

MCU學習筆記_PWR電源管理系統

TPS62130電源芯片的學習

芯片及系統電源學習分析

芯片及系統電源學習分析

評論