優化 FPGA HLS 設計

用工具用 C 生成 RTL 的代碼基本不可讀。以下是如何在不更改任何 RTL 的情況下提高設計性能。

介紹

高級設計能夠以簡潔的方式捕獲設計,從而減少錯誤并更容易調試。然而,經常出現的問題是性能權衡。在高度復雜的 FPGA 設計中實現高性能需要手動優化 RTL 代碼,而這對于HLS開發環境生成的 RTL 代碼來說是不可能的。

然而,存在一些解決方案,可以通過使用 FPGA 工具設置優化設計本身來最大限度地減少性能損失。

高效找到正確的 FPGA 工具設置

盡管設計人員知道 FPGA 工具設置的存在,但這些設置往往沒有得到充分利用。通常,只有在出現設計問題時才使用工具設置。然而,對于已達到性能目標的設計,還有額外10% 至 50% 性能改進的巨大潛力。

上面的核心問題在于選擇正確的工具設置,因為不同的 FPGA 工具提供 30 到 70 種用于綜合和布局布線的設置。可能的組合太多了。可以編寫腳本來創建不同的運行并嘗試推薦的標準指令/策略。

最后一個挑戰問題是計算能力不足。典型的嵌入式應用程序是在單臺計算機上設計的。運行多個編譯需要更多的計算能力。這是與時間的權衡。如果可以同時運行更多(使用云)綜合策略,周轉時間將會更短。

如何優化高級設計 - Sobel 濾波器

Sobel 濾波器是視頻處理中常用的參考設計。該參考設計針對具有 Dual ARM? Cortex?-A9 MPCore? 的 FPGA。

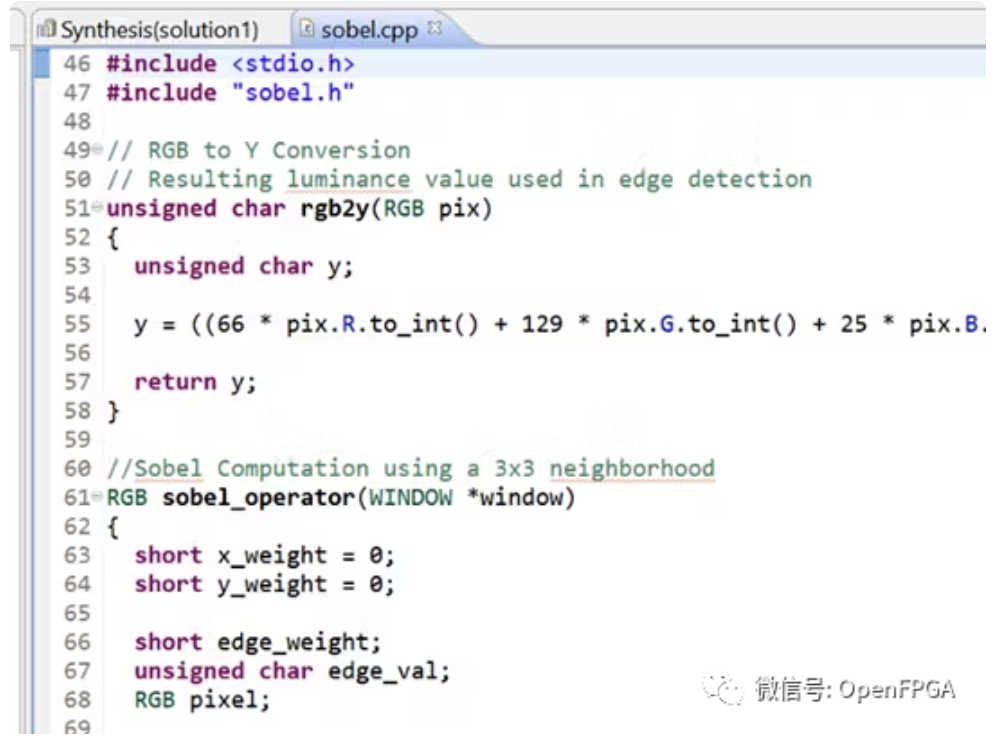

我們使用 Xilinx HLS 工具來打開此設計。

它的時鐘周期為 5.00 ns,即 200 MHz。從時序估計(見下文)來看,它仍然缺少 506 ps 的時序,這相當于 181 MHz,比目標速度低 10%。

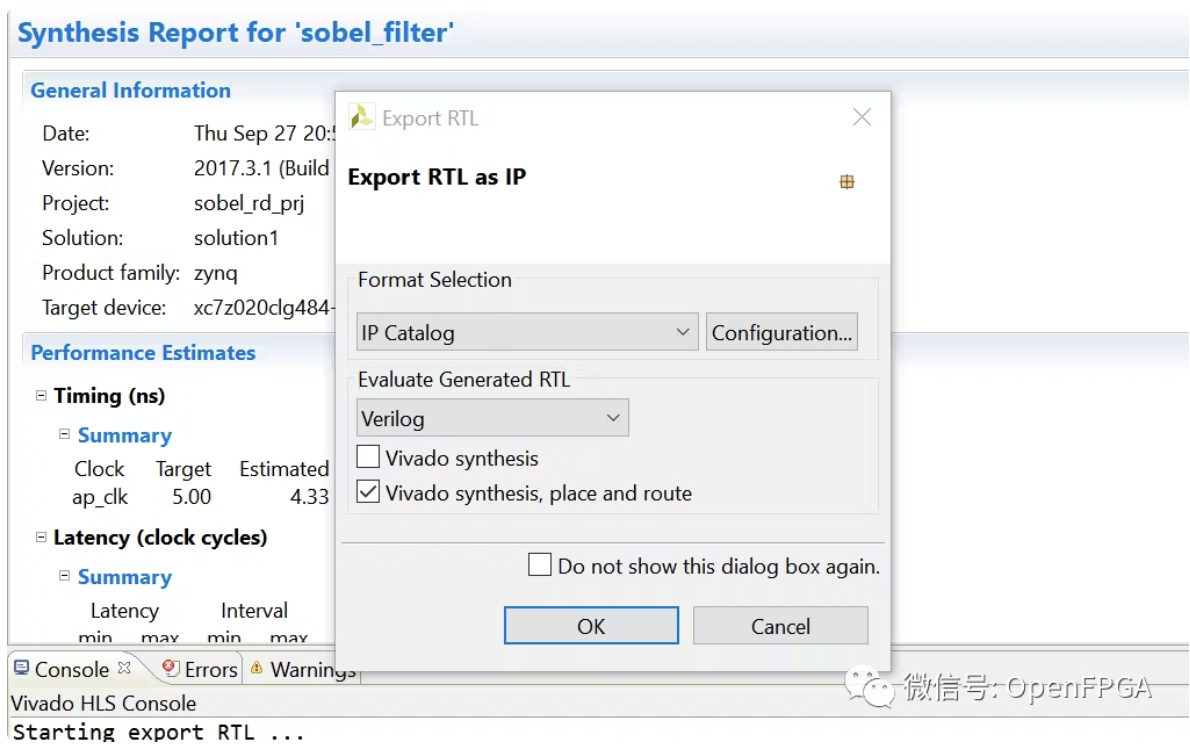

導出到 RTL 項目

在不更改 C++ 代碼的情況下,將設計導出到 RTL 中的 Vivado 項目中。在“解決方案”下,選擇“導出 RTL”。

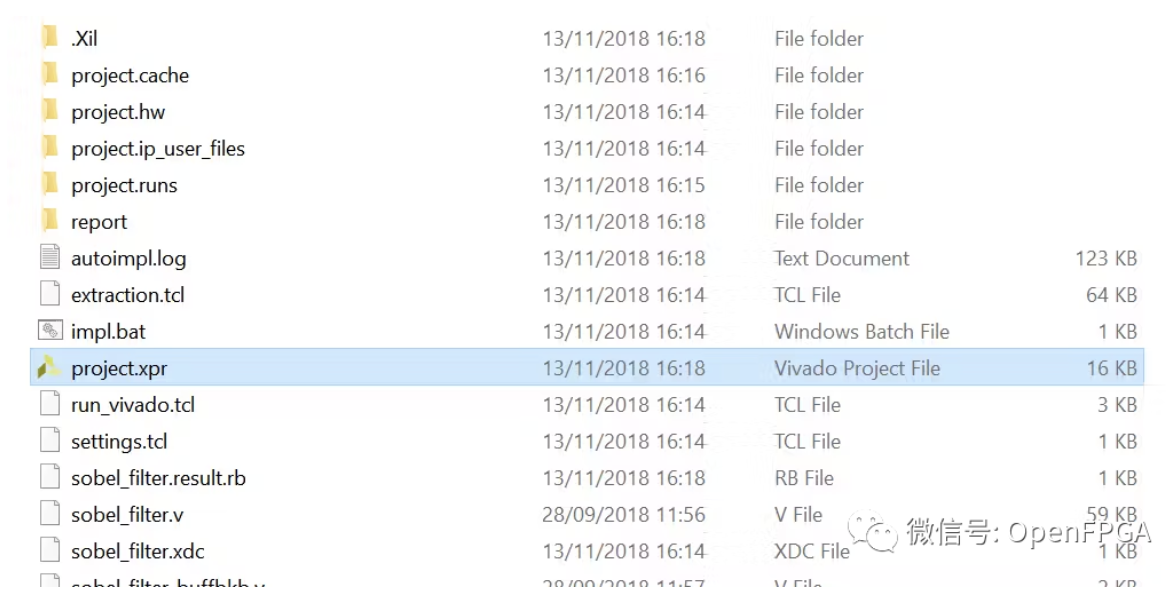

它將在后臺執行 Vivado 并生成項目文件 (XPR)。它還應該編譯設計,并且應該在控制臺中看到實際的時序詳細信息。完成后,在/solution/impl/verilog/文件夾中找到項目文件。

找到一個 XPR 文件。可以通過Vivado打開它來驗證它,可以看到生成的RTL源碼。

優化時序

下一步是使用名為InTime 的設計探索工具。(同樣,可以自己編寫腳本來嘗試 Vivado 工具中提供的標準指令或策略)可以使用免費評估許可證在本地運行 InTime 。或者,使用一些免費積分和預裝 FPGA 工具注冊 Plunify云帳戶。

啟動InTime后,打開項目文件。當提示要使用的 Vivado 版本時,請使用“相同”的 Vivado 版本。例如,如果使用2017.3 HLS,請使用2017.3 Vivado。

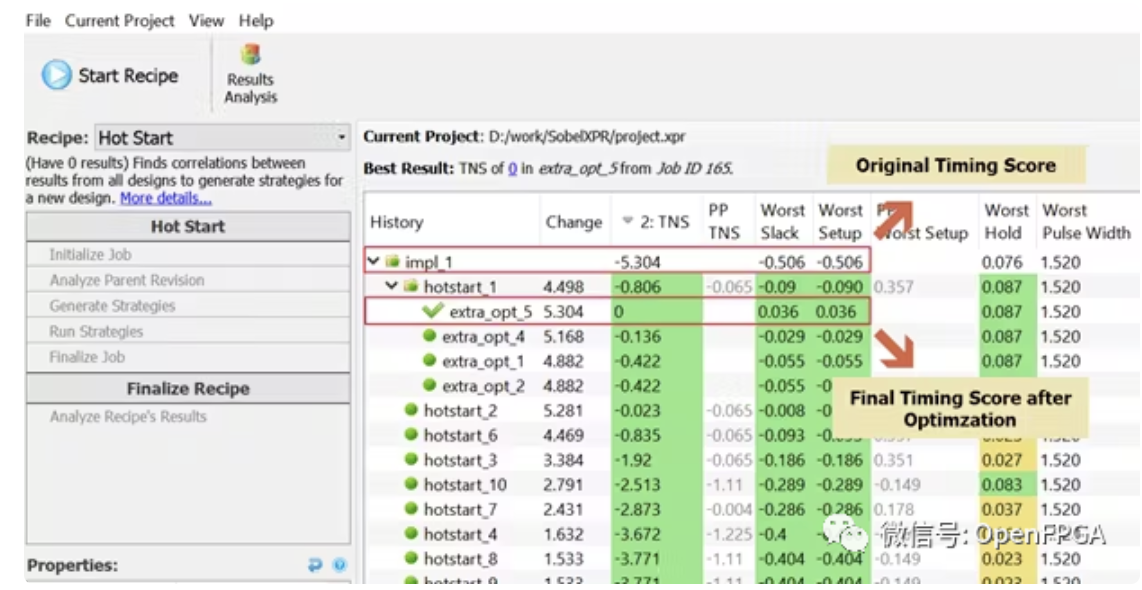

選擇“熱啟動”。“熱啟動”是基于之前其他設計經驗的推薦策略列表。

單擊“Start Recipe”開始優化。如果在云上運行,則應同時運行多個編譯以減少時間。

優化過程和結果

在第一輪(“熱啟動”)之后,最好的結果是“hotstart_1”策略。然而,它仍然缺少-90ps 的時序。

我們對“HotStart_1”的結果應用了名為“Extra Opt Exploration”的第二個秘訣。這側重于優化關鍵路徑。這是一種迭代優化,只要每次迭代都顯示出改進,就會不斷重復。如果達到時間目標或未能顯示出改進,它最終將自動停止。

經過兩輪優化,共15次編譯,該設計能夠滿足200Mhz的性能目標。這是無需對 RTL 源代碼進行任何更改即可實現的。

更高水平的性能

要達到更高的性能水平,需要在所有方面進行優化——架構設計、代碼和工具。工具設置探索可以克服更高級別設計的性能權衡,而不會失去它首先帶來的生產力優勢。這對于高級設計師來說是雙贏。

-

ARM

+關注

關注

134文章

9165瀏覽量

369189 -

濾波器

+關注

關注

161文章

7860瀏覽量

178928 -

FPGA設計

+關注

關注

9文章

428瀏覽量

26628 -

RTL

+關注

關注

1文章

385瀏覽量

59950 -

HLS

+關注

關注

1文章

130瀏覽量

24208

發布評論請先 登錄

相關推薦

如何在不改變RTL代碼的情況下,優化FPGA HLS設計

優化 FPGA HLS 設計

怎么利用Synphony HLS為ASIC和FPGA架構生成最優化RTL代碼?

【正點原子FPGA連載】第一章HLS簡介-領航者ZYNQ之HLS 開發指南

FPGA高層次綜合HLS之Vitis HLS知識庫簡析

使用Vivado高層次綜合 (HLS)進行FPGA設計的簡介

Achronix與Mentor攜手帶來高等級邏輯綜合(HLS)與FPGA技術之間的連接

FPGA并行編程:基于HLS技術優化硬件設計

利用FPGA工具設置優化FPGA HLS設計

使用網絡實例比較FPGA RTL與HLS C/C++的區別

FPGA基礎之HLS

FPGA——HLS簡介

使用Vivado高層次綜合(HLS)進行FPGA設計的簡介

如何優化FPGA HLS設計呢?

如何優化FPGA HLS設計呢?

評論