DFT PLL向量,ATE怎么用?

自動測試設備(ATE)對PLL(鎖相環)進行測試時,我們首先要明白PLL在系統級芯片(SoC)中的重要性。它是SoC中關鍵的時鐘或信號同步部件,其性能直接影響到芯片邏輯的正確運行。在測試PLL

IP時,通常會有多個測試項目,如頻率測試、相位噪聲、鎖定時間、穩定性、誤差和漂移等。

但在SoC的ATE測試中,CP階段通常只進行PLL頻率和鎖定測試。

那么DFT如何產生PLL 測試pattern,以及ATE如何根據這些pattern進行PLL測試?

DFT(Design For Test)是用于生成測試pattern以檢測芯片功能和性能的技術。在生成PLL(Phase-Locked Loop)測試pattern的過程中,DFT通過使用特定的算法和測試向量來生成測試pattern。這些測試pattern旨在模擬PLL在不同條件下的行為,以確保芯片的PLL功能正常。

ATE(Automated Test Equipment)是一種用于自動測試芯片性能和功能的設備。在測試PLL時,ATE會使用由DFT生成的測試pattern來模擬芯片的輸入,并監控芯片的輸出以檢查其功能是否正常。

這里的pattern指的是用于測試PLL的特定數據序列。這些數據序列在測試過程中被發送到芯片的輸入管腳,并在芯片的輸出管腳比較相應的輸出數據序列。通過比較預期輸出和模擬輸出,ATE可以判斷PLL是否正常工作。

總之,DFT通過生成測試pattern來模擬PLL的行為,ATE使用這些測試pattern來測試芯片的功能,并比較預期輸出和模擬輸出以判斷芯片是否正常工作。

DFT 產生 PLL 向量

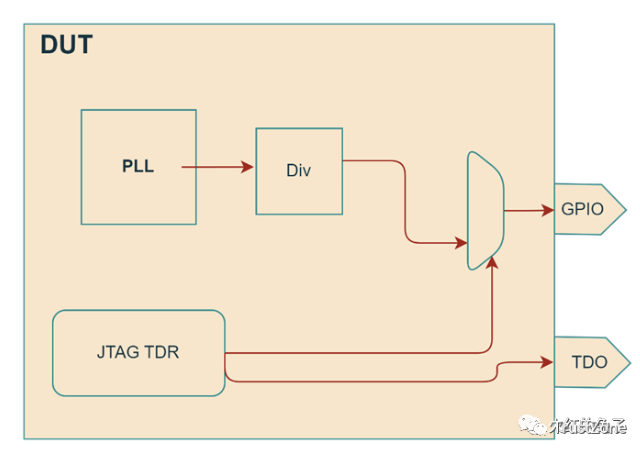

DFTer 每條PLL向量配置要求:(參考下圖)

?a) JTAG配置多個PLL為對應的待測頻點。

?b) 配置Div系數為最大,盡可能降低輸出時鐘的頻率。

?c) LOCK信號在TDO串行移出觀測或者復用到IO上。

?d) 切換IO復用后,PLL div 信號將會輸出到對應GPIO上。

PLL輸出頻率的要求:10M~50M之間。 WHY?

1.上限受限于GPIO,在高于50M時,GPIO的輸出特性隨頻率升高而減弱,最好低于50M。(機臺PS1600最高1.6G采樣頻率,不需要考慮奈奎斯特頻率的限制。)

1.下限需要考慮到不同測試方法的測試時間的影響,比如給一個32K的鐘,機臺需要構造更長的采樣向量。

-

芯片

+關注

關注

456文章

51170瀏覽量

427244 -

測試

+關注

關注

8文章

5375瀏覽量

127061 -

IC

+關注

關注

36文章

5979瀏覽量

176216 -

pll

+關注

關注

6文章

781瀏覽量

135332 -

DFT

+關注

關注

2文章

231瀏覽量

22834

發布評論請先 登錄

相關推薦

Nvidia is hiring-Senior DFT Engineer

什么是DFT,DFT是什么意思

DFT分步法原理分析

DFT如何產生PLL 測試pattern

DFT如何產生PLL 測試pattern

評論