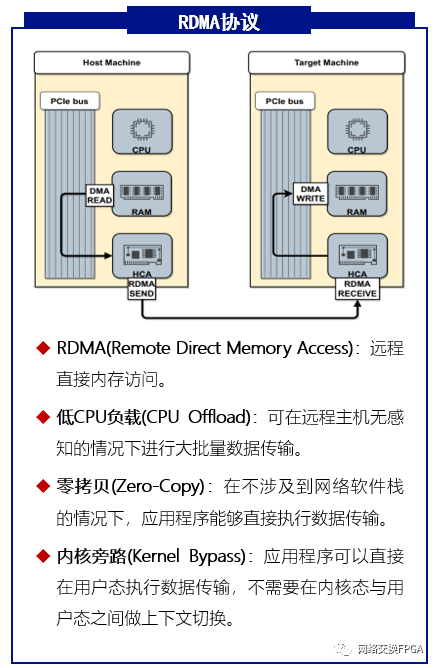

傳統TCP/IP技術處理數據包需通過操作系統和其他軟件層,導致數據在系統內存、處理器緩存和網絡控制器緩存間頻繁復制,增加了服務器CPU和內存的負擔,特別是在網絡帶寬、處理器速度與內存帶寬不匹配時,網絡延遲會進一步加劇。RDMA技術通過將數據處理從CPU旁路并卸載到硬件上來實現低時延和高帶寬特性。

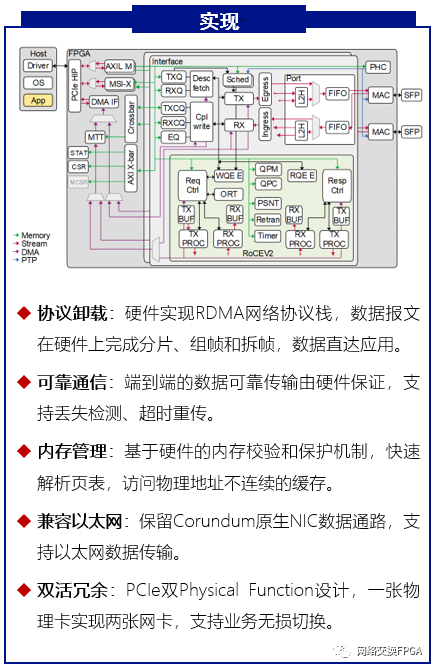

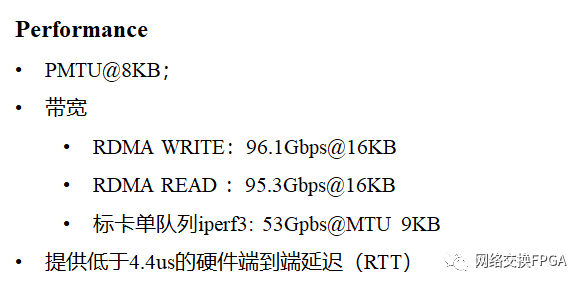

基于這一研究背景,介紹一種具備RDMA功能的FPGA網卡實現方案—RNIC 。本方案以Corundum開源高性能原型平臺為基礎, 實現了100Gbps的RoCE v2網絡協議棧卸載加速;在保留Corundum原生PCIe DMA引擎等組件的基礎上,通過精準的拆分設計、邏輯耦合和路徑復用,將RoCE v2網絡協議棧嵌入以太網網卡設計。方案支持單邊RDMA READ和RDMA WRITE操作、雙邊SEND/RECV操作以及立即數操作,提供Back-to-N的重傳機制保障數據傳輸完整性的同時提供了可達256的Outstanding能力, 并支持基于DCQCN算法的擁塞控制機制為本方案在數據中心等場景的大規模部署提供保障。實測RNIC能夠實現低至4us左右的硬件端到端延遲以及高達96Gbps的吞吐量。

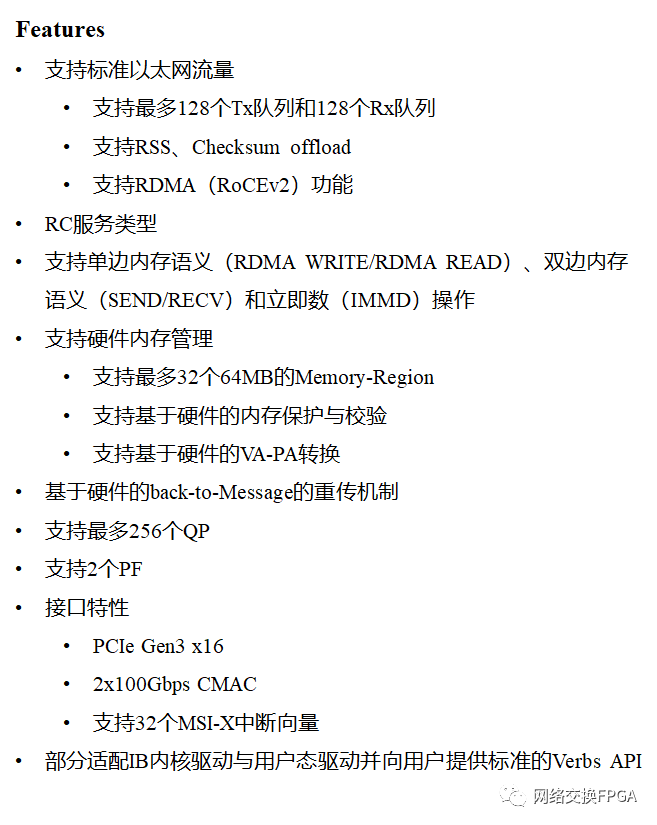

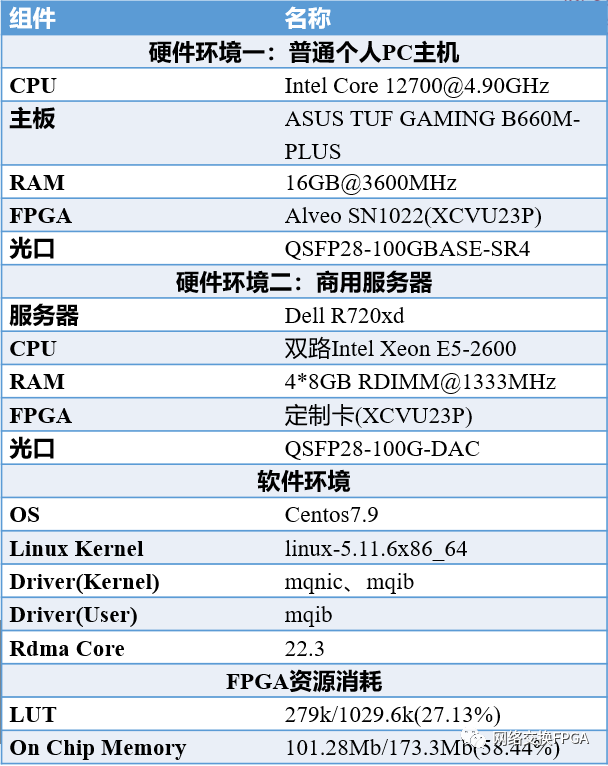

我們實現的100G RDMA網卡具體指標和性能如下:

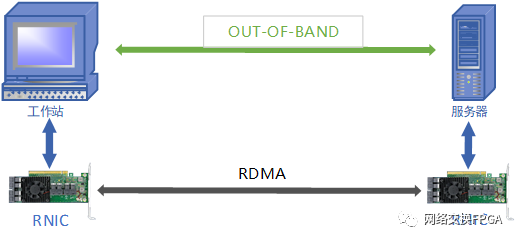

測試場景及拓撲連接圖如下。

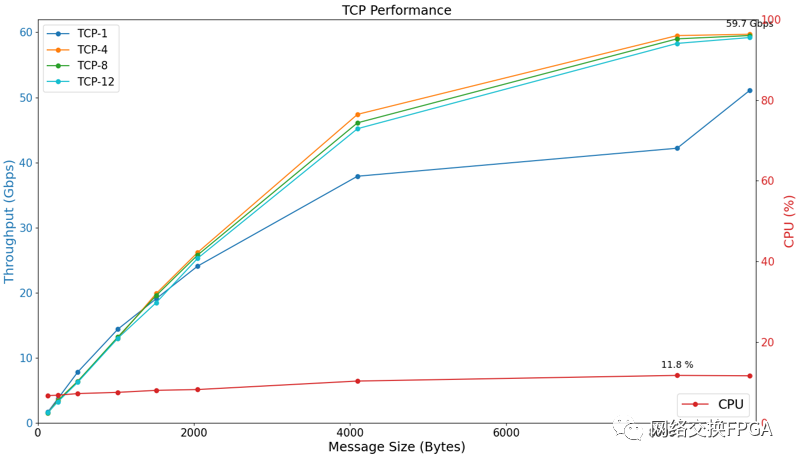

TCP測試結果如下。

TCP性能表現:實測在Linux系統環境下,端到端連接拓撲,當MTU=9214B,不進行多核優化時,本方案的iperf TCP帶寬可達59.7G bps;CPU占用率為12%左右 ; TCP/IP協議普遍延遲在100–200微秒之間。

TCP測試分析:性能開銷集中在內核協議棧的系統調用、內存拷貝、協議處理與中斷處理等方面。這些開銷占用了大量的CPU 資源,增加了數據延遲。

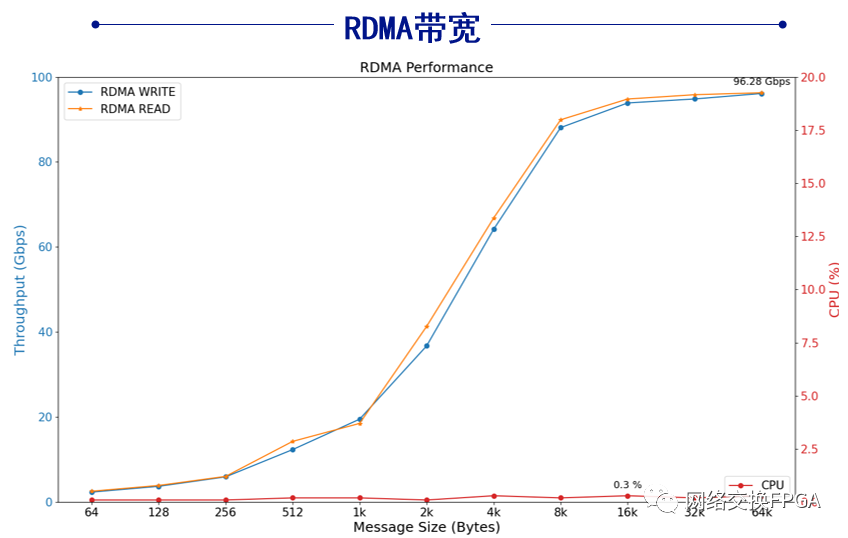

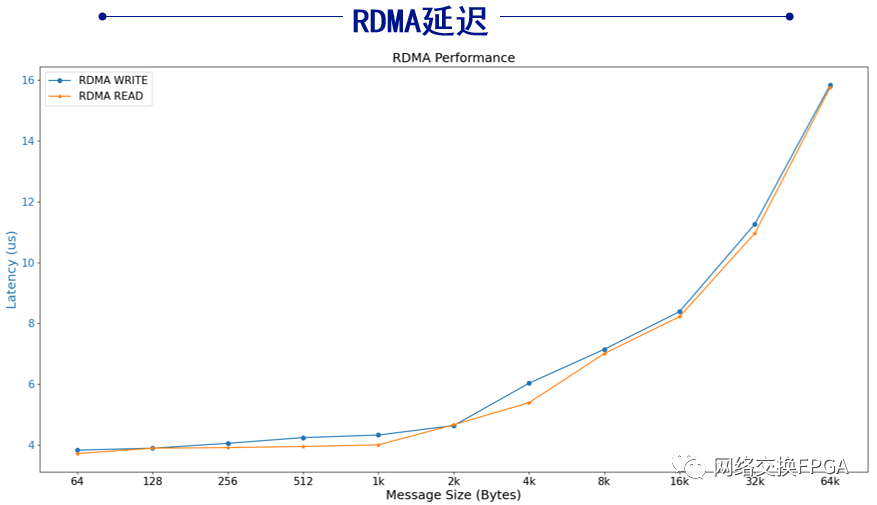

RDMA測試結果如下。

RDMA性能表現:在Linux系統環境下,相同測試拓撲,使用配套驅動程序和應用程序發送RDMA命令進行測試。本方案的RDMA網卡實測單邊RDMA語義讀寫帶寬可達96.28G bps;CPU占用率不超過0.3%;硬件端到端讀寫延遲低至4us左右。

RDMA測試分析:當消息大小大于8KB時,系統吞吐量可以逼近滿帶寬,當消息較小時,吞吐量會顯著降低。原因一方面是數據幀幀頭開銷占比上升導致有效帶寬下降,另一方面在于硬件設計無法支撐更高的消息速率。時延會隨消息大小出現近似線性的增長,最大的延遲花費在PCIe鏈路和網絡鏈路上,硬件的處理開銷占比很小。

對比以太網和RDMA的測試結果可知,在相同的硬件條件下,使用RDMA技術的網卡可以擁有更高的網絡帶寬和更低的傳輸時延,對于云服務、數據中心等具有高吞吐量的網絡業務需求場景,RDMA技術更能滿足實際需要,能充分解放處理器資源,提高帶寬,降低成本。

下面視頻詳細介紹實際測試情況:

我們未來有很多工作要做,如添加我們之前做的P4可編程的工作(【Verilog開源】一種用于智能網卡或可編程交換機的,支持P4語言的高性能開源解析器的設計),突破Corundum架構限制支持百萬QP對和提升小包性能,進一步優化流量控制、擁塞管理和負載均衡等問題,進一步的提高數據中心網絡的數據傳輸速率和穩定性。

?

?

審核編輯:劉清

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605988 -

以太網

+關注

關注

40文章

5460瀏覽量

172721 -

RDMA

+關注

關注

0文章

78瀏覽量

8981 -

PCIe接口

+關注

關注

0文章

121瀏覽量

9788 -

TCP通信

+關注

關注

0文章

146瀏覽量

4292

原文標題:【實測】基于Corundum架構的100G RDMA網卡

文章出處:【微信號:gh_cb8502189068,微信公眾號:網絡交換FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RDMA RNIC虛擬化方案

一種基于FPGA的多通道頻率測量系統的實現方法介紹

RT-thread實現U盤升級的一種OTA方案

分享一種智能網卡對熱遷移支持的新思路

一種基于FPGA的誤碼性能測試方案

一種通用SPI接口的FPGA設計與實現

介紹一種具備RDMA功能的FPGA網卡實現方案—RNIC

介紹一種具備RDMA功能的FPGA網卡實現方案—RNIC

評論