一:Boundary Scan的基本概念及應用

-> 什么是Boundary SCAN?

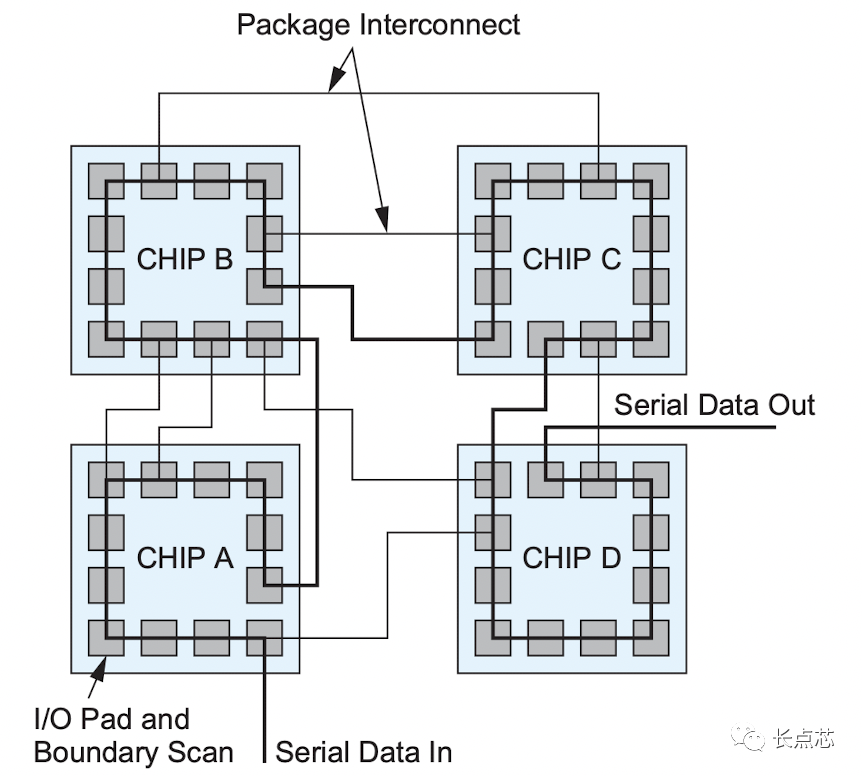

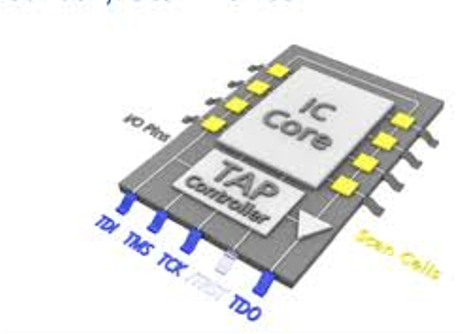

首先我們都知道BSCAN是一種用于測試和驗證集成電路的技術。在集成電路中,有許多引腳***(pins)*** 用于與其他器件進行通信和連接。BSCAN 通過在芯片引腳之間添加可控的掃描鏈***(Scan Chain)*** ,使得我們能夠在測試和調試時以串行方式訪問每個芯片引腳。如下圖

-> BSCAN誕生的契機是什么呢?

電路板的日益復雜和 surface mount technologies (表面貼裝技術)等技術的轉變導致系統設計師們達成一致,采用了一種統一的基于掃描的方法,稱為邊界掃描***(boundary scan)*** ,用于在電路板(任何系統)級別上測試芯片。

-> BSCAN為芯片驗證帶來了什么?

1. 連通性測試:

假設你在設計一個SoC,其中涉及許多引腳用于連接不同的子系統。使用邊界掃描,你可以測試這些引腳之間的連通性。例如,你可以加載一個測試模式,通過觀察TDO信號,檢查引腳是否按預期連接,是否存在開路或短路問題。

2.故障定位:

在芯片制造過程中,可能會出現一些未預料的故障,例如焊接問題或晶體管故障。通過加載適當的測試模式,你可以觀察故障信號在掃描鏈上的傳播路徑,從而精確定位故障的位置,加速故障排除過程。

3.邏輯驗證:

在芯片設計的早期階段,你可以使用邊界掃描來驗證芯片的基本邏輯功能。通過加載測試模式,觀察輸出是否與預期相符,以驗證芯片的功能性。

4.硬件調試:

假設你遇到了一些奇怪的硬件問題,如時序問題或邏輯錯誤。通過在掃描鏈上加載特定的測試模式,你可以觀察信號在芯片內部的傳播路徑,有助于理解信號的行為,從而更有效地進行硬件調試。

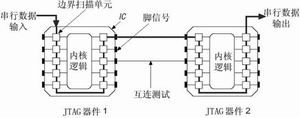

5.芯片級聯測試:

在多芯片系統中,邊界掃描可以用于測試不同芯片之間的連接性。通過將多個芯片的邊界掃描鏈連接在一起,你可以檢測引腳和信號在整個系統中的傳輸情況。

總之,邊界掃描在SoC設計驗證中是一項強大的工具,可以幫助芯片驗證工程師在不同階段進行測試、調試和驗證,從而提高芯片的質量和可靠性。

二:Boundary Scan的硬件實現

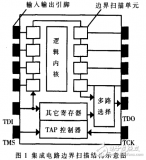

邊界掃描的核心思想是在SoC芯片的引腳周圍添加一個可控的掃描鏈,將芯片內部的邏輯電路與掃描鏈相連。這個掃描鏈由一系列的Scan Cells (掃描單元)組成,每個掃描單元可以存儲一個比特的數據。通過操控TAP(Test Access Port) 控制器,我們可以在掃描鏈上加載測試模式,然后觀察測試模式在芯片內部的傳播路徑,從而實現測試、調試和驗證。

沒錯,下面就要詳細介紹一下我們的主角TAP了!

TAP控制器是邊界掃描的核心,它負責管理掃描鏈的操作。TAP控制器通過四個或個基本信號進行操作測試訪問端口。

- TCK(Test Clock):用于控制掃描鏈的時鐘信號。

- TMS(Test Mode Select):用于控制TAP控制器狀態機的狀態切換。

- TDI(Test Data Input):用于將數據加載到掃描鏈中。

- TDO(Test Data Output):用于從掃描鏈讀取數據。

- TRST(Test Reset):用于異步復位TAP控制器,如果芯片沒有自動生成上電復位信號的話。

不過一般我們用到前面四個就夠了,下面是一個基本的TAP架構圖。

下面我們就按照這張圖剖析一下TAP的組成部分。

1. TAP控制器(TAP Controller):

TAP控制器是TAP的核心,負責控制掃描操作的狀態轉換和時序。它通過TCK(Test Clock)、TMS(Test Mode Select)、TDI(Test Data Input)和TDO(Test Data Output) 等信號,實現從一個狀態到另一個狀態的轉換,以便執行不同的操作,如掃描測試數據或讀取測試結果。TAP控制器按照JTAG(Joint Test Action Group) 標準定義了一組狀態,如Test-Logic-Reset狀態、Run-Test/Idle狀態等。

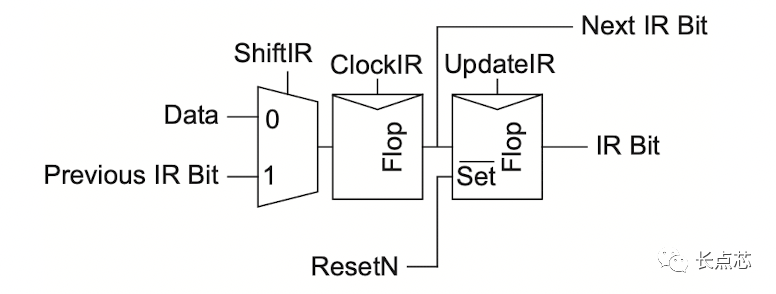

2.指令寄存器(Instruction Register):

指令寄存器用于存儲和加載TAP控制器的指令。在測試和調試過程中,可以通過加載不同的指令來控制芯片的操作。指令寄存器的位數決定了可以定義的不同指令數量,從而支持多種測試模式和操作。

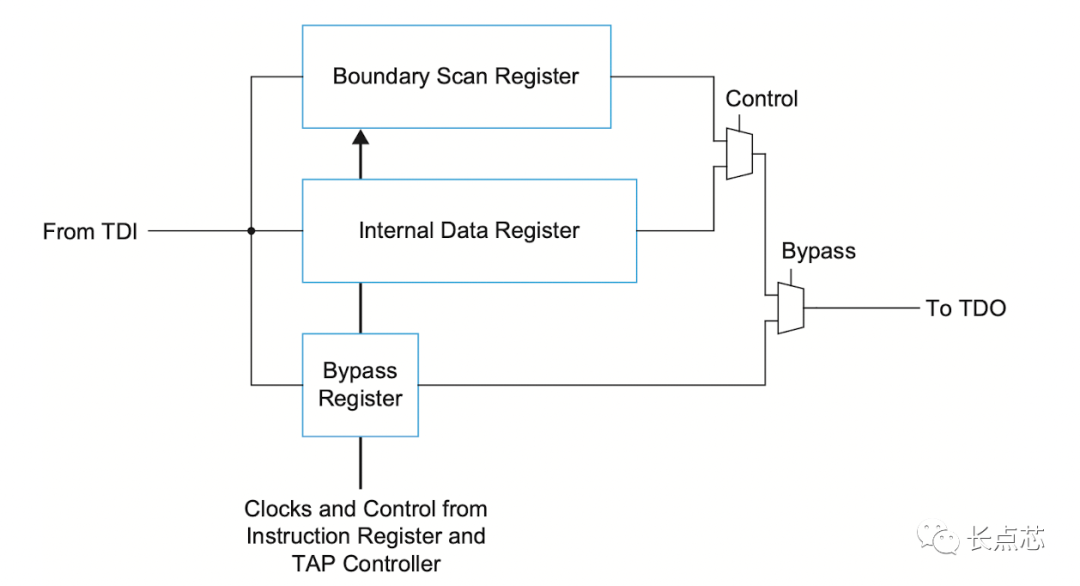

3. 測試數據寄存器(Test Data Register):

測試數據寄存器用于存儲測試模式數據,它是掃描鏈(Scan Chain)的一部分。測試數據可以被輸入到芯片進行測試,也可以從芯片中讀取出來作為測試結果。測試數據寄存器又分為不同的子寄存器,包括邊界掃描寄存器、旁路寄存器和TDO驅動器。

3.1. 邊界掃描寄存器(Boundary Scan Register):

邊界掃描寄存器是邊界掃描技術的關鍵,用于在芯片的引腳之間插入可控的測試邏輯。它允許在芯片的輸入和輸出之間插入額外的邏輯電路,以便執行連通性測試、故障定位等操作。邊界掃描寄存器存儲了掃描鏈上的測試模式數據,可以通過TAP控制器進行加載和讀取。

3.2. 旁路寄存器(Bypass Register):

旁路寄存器用于繞過邊界掃描邏輯,將芯片的輸入直接連接到輸出。當不需要執行邊界掃描時,可以通過加載指令將旁路寄存器中的數據傳遞給TDO輸出,從而繞過邊界掃描邏輯。

3.3. TDO驅動器(TDO Driver):

TDO驅動器用于控制TDO輸出信號的驅動。在掃描鏈操作期間,TDO驅動器負責將測試模式數據從邊界掃描寄存器或旁路寄存器傳遞到TDO輸出。TDO驅動器還可以根據TAP控制器的狀態控制TDO輸出信號的開關。

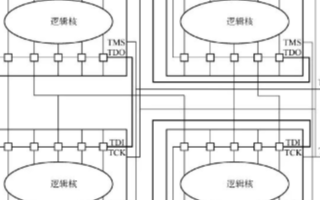

這些組成部分共同構成了TAP結構,使得邊界掃描技術成為一種強大的芯片測試和驗證工具,為集成電路設計和制造過程提供了可靠的測試手段。下圖展示一個完整的Boundary SCAN。

結語

Boundary SCAN作為現代芯片設計驗證領域的重要工具,為芯片工程師提供了強大的測試和調試手段。它通過TAP控制器、掃描鏈和測試模式生成器的協同工作,實現了對芯片內部功能和連通性的全面測試。

-

集成電路

+關注

關注

5392文章

11622瀏覽量

363185 -

晶體管

+關注

關注

77文章

9746瀏覽量

138900 -

芯片制造

+關注

關注

10文章

629瀏覽量

28913 -

邊界掃描

+關注

關注

1文章

32瀏覽量

15036 -

Scan

+關注

關注

0文章

12瀏覽量

3579

發布評論請先 登錄

相關推薦

FX3支持IEEE1149的邊界掃描測試嗎?

如何為第三方設置Zynq 7000系列進行邊界掃描?

邊界掃描技術及其在VLSI芯片互連電路測試中的應用

基于邊界掃描技術的板級測試分析

邊界掃描測試技術在帶DSP芯片數字電路板測試中的應用解析

TMS320VC5510 GGW BSDL Model邊界掃描DSP模型的詳細資料概述

JTAG(四) 邊界掃描測試技術

邊界掃描-Boundary Scan技術及其在芯片測試中的應用

邊界掃描-Boundary Scan技術及其在芯片測試中的應用

評論