近年來,5G、自動駕駛、超大規模計算,以及工業物聯網等領域呈現出強勁的發展勢頭。推動這些高速發展的產業是AI(人工智能)和ML(機器學習)的大規模應用。這種全新的技術布局不僅加速了更復雜的計算需求、更強的功能性和更快的數據傳輸速度,同時也為芯片研發人員帶來了前所未有的挑戰:即下一代芯片必須更快且更智能。

在當前的背景下,由于算力和存儲需求正面臨爆發式增長,這直接導致推動先進SoC(系統級芯片)設計和驗證的壓力也呈指數級增加。特別是在集成電路規模越來越龐大的現實情況下,從設計到流片(Tape-out)的全流程中,驗證變得尤為重要。這是因為有效的驗證不僅確保了電路在設計層面的完善,還保證了其在實際應用中的穩定運行,從而降低了修正和調整的成本和時間。

為了應對這一挑戰并縮短驗證周期,硬件仿真成為了超大規模集成電路驗證的首選工具。它能在最短的時間內完成對電路功能的全面驗證,這樣就大大減少了整個設計到生產的周期。同時,AI/ML算力的飛速增長不僅促進了EDA(電子設計自動化)工具的快速演進,還與EDA工具結合,催生了一種“雙向加速”的良性循環。

去年年底,思爾芯推出了首款國產企業級硬件仿真系統——芯神鼎OmniArk。值得一提的是,芯神鼎已將AI應用于編譯流程中,這無疑推動了芯片設計領域的發展。

芯神鼎硬件仿真系統采用了由AI驅動的智能編譯引擎,該引擎能夠在編譯流程中極大地減少編譯時間和內存占用,實現增量編譯,并能智能匹配P&R(布局與布線)策略,從而顯著提高布線的成功率。本文將從多個獨立模塊的角度,深入探討芯神鼎硬件仿真系統的智能編譯流程。

并行綜合:打破傳統編譯瓶頸

傳統綜合方法充滿了局限性。在集成電路設計領域,傳統綜合方法主要有兩種:Top-down綜合和Bottom-up綜合。1.Top-down綜合

該方法對整個設計進行處理,以實現徹底的優化。盡管優化程度高,但這一方案的綜合時間通常非常長,不適用于迅速變化的項目周期。2.Bottom-up綜合

此方法首先對底層模型進行獨立綜合,然后逐步并入上層模塊進行綜合。雖然這適用于一些包含獨立IP的復雜設計,但其在超大規模集成電路(VLSI)應用中表現出速度和靈活性的明顯不足。對于超大規模集成電路,這兩種傳統綜合方法通常成為編譯過程的瓶頸。除了時間效率低下,其對計算資源,特別是內存的占用也相當巨大。

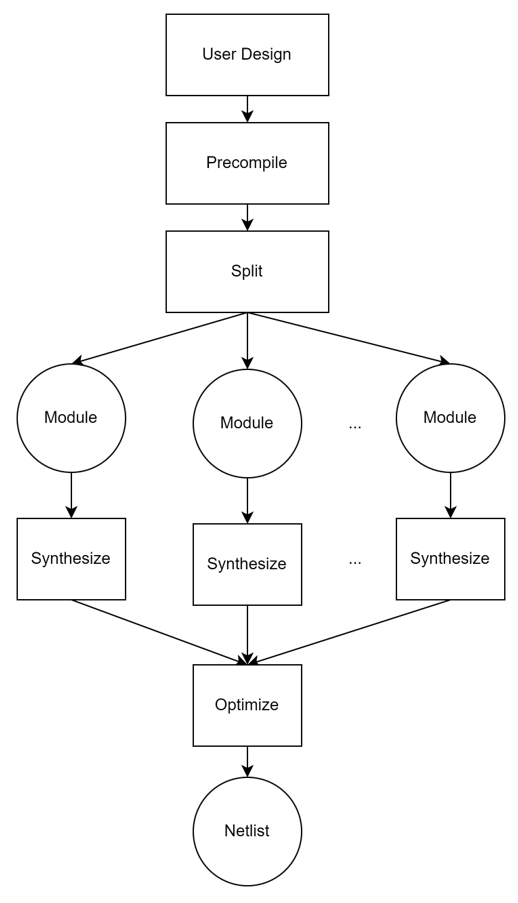

芯神鼎硬件仿真系統對并行綜合進行了創新,采用Module-by-Module的綜合方式,徹底改變了這一現狀。首先,芯神鼎針對整個設計進行必要的全局處理和優化,例如XMR(Cross-Module Reference)處理。接著,以Module為最小粒度,啟動多核并行綜合過程。這一步是本系統最大的創新之一,它允許系統充分利用服務器/集群的并行計算性能。在所有模塊綜合完成之后,系統進一步進行跨模塊邊界(Cross Module Boundary)邏輯優化。此外,芯神鼎能根據服務器配置和實際負載動態調節并行任務數量,以實現負載均衡。

這種并行綜合方法大大加速了超大規模集成電路設計的整體綜合效率。實際應用中,對于多核NVDLA(NVIDIA Deep Learning Accelerator)這樣的復雜設計。經測試,其加速率可以達到驚人的10~100倍,尤其在多核設計中表現出色。

通過創新的并行綜合技術,芯神鼎硬件仿真系統成功地突破了傳統綜合方法在時間和資源效率方面的局限,為超大規模集成電路設計帶來了前所未有的效率提升。 圖一:并行綜合流程

圖一:并行綜合流程

高效率與高質量的智能P&R

在基于硬件仿真的超大規模設計流程中,P&R(布局與布線)通常是編譯的最后一步,負責生成最終的bitstream文件。雖然現有的編譯工具提供了多種P&R選項,目的是適應不同設計需求和優化目標,但實際情況卻遠沒有那么簡單。由于各種SoC需求和應用場景的多樣性,幾乎沒有一種“通用”的P&R選項組合能適用于所有場景。因此,開發人員需要根據特定的設計需求,手動選擇或調整P&R選項,以求達到最佳的設計輸出。

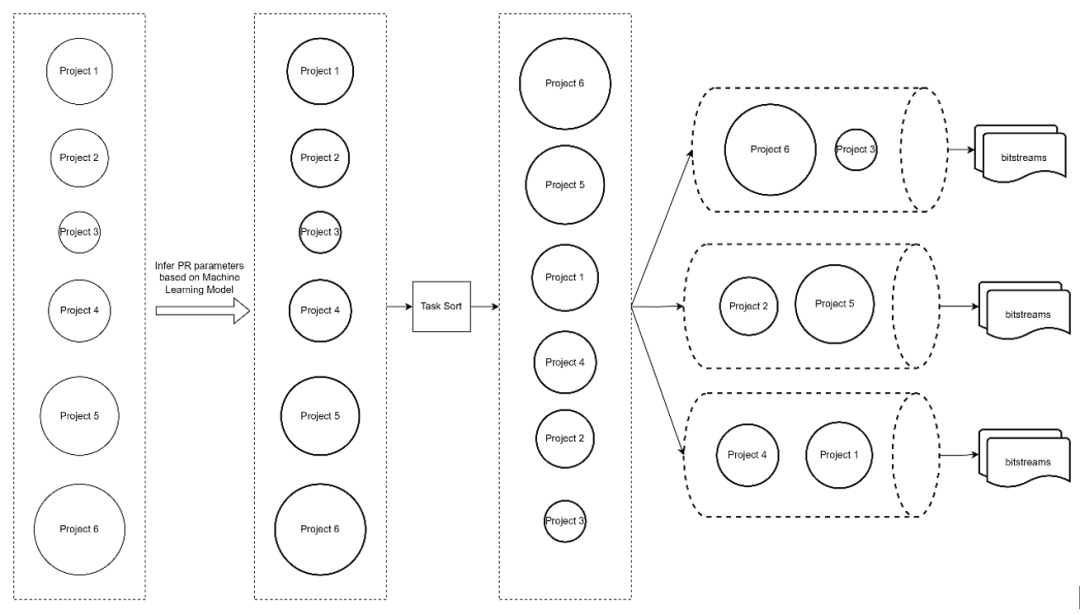

1. 基于機器學習的智能P&R

芯神鼎硬件仿真系統突破了這一局限,采用基于機器學習(ML)的智能P&R方法。通過使用大量的實際P&R數據進行深度訓練,系統生成的ML模型能在推理階段輸出最優的P&R參數組合。更值得一提的是,這種基于數據驅動的方法在多個關鍵性能指標上都超過了人工專家的判斷。例如,在布線成功率方面,經測試,可以顯著提高布線通過率;同時,P&R所需的總時間也可大幅度減少。

2.優化任務調度和并行計算

除了使用機器學習進行智能選項推薦外,芯神鼎硬件仿真系統還進一步優化了任務調度算法。通過智能任務調度,系統能確保在進行P&R操作時充分利用編譯服務器的多核計算能力。具體的并行能力和效率提升取決于編譯服務器的性能和配置。

通過集成基于機器學習的智能P&R以及高效的任務調度和并行計算功能,芯神鼎硬件仿真系統為FPGA設計提供了一種更高效、更質量可控的解決方案。這不僅大幅減少了編譯時間,同時也顯著提升了輸出結果的質量。 圖二:任務調度和并行計算流程

圖二:任務調度和并行計算流程

增量編譯

在超大規模集成電路(VLSI)的設計過程中,即使進行了多方面的編譯流程優化,編譯時間依然可能成為項目進度的瓶頸。更進一步地說,對于那些已經編譯過但需做細微修改的工程,每次都進行全量編譯會大大延長開發周期,耗費人力和計算資源。

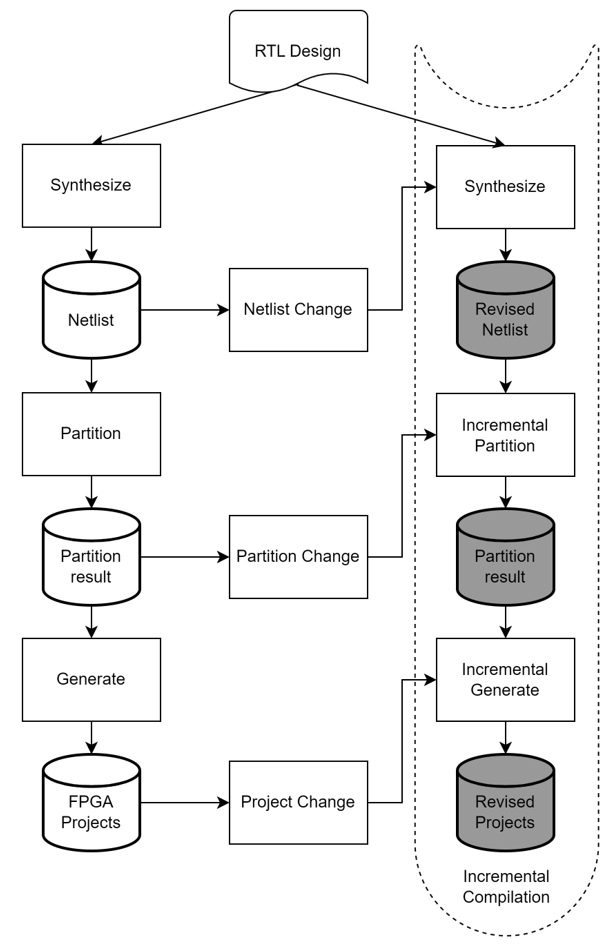

增量編譯(Incremental Compilation)是一種編程優化策略,用于加快編譯過程。在一個大型或復雜的代碼基礎上,每次進行全量編譯(即重新編譯整個代碼基礎)通常會消耗大量時間和計算資源。增量編譯的目標是只重新編譯自上次編譯后發生變化或被影響的代碼部分,而不是整個代碼庫。

增量編譯系統首先會跟蹤代碼中各模塊、函數或文件的依賴關系。當某一部分代碼發生改動后,編譯系統會識別這一改動,并查找所有依賴于該部分的其他代碼。只有被改動的代碼和依賴于它的代碼會被重新編譯。其它未改動和不受影響的代碼則不需要重新編譯。重新編譯的代碼會與舊的編譯結果合并,生成一個更新的可執行文件或庫。對于代碼庫非常大的項目,增量編譯幾乎是必需的。

芯神鼎硬件仿真系統便采用了這種增量編譯策略。它采用了一種先進的增量編譯引擎,該引擎涵蓋了綜合模塊、Partition模塊以及工程生成模塊等關鍵部分。這些模塊都集成了增量編譯技術,可以在二次編譯過程中智能感知用戶所做的任何修改。這種自動感知機制極大地減少了重新編譯所需的計算量,因為它只針對修改過的部分進行編譯,而非整個設計。這樣不僅大幅度縮短了編譯時間,還優化了資源使用效率。 圖三:增量編譯流程

圖三:增量編譯流程

總結

AI+EDA的結合代表了一次跨越式的技術進步,它不僅有望延續并拓展摩爾定律的生命周期,還能顯著節約研發時間和資本投入,提升行業整體競爭力。進一步地,這一結合還為全球芯片設計領域開創了全新的可能性,比如通過機器學習算法優化設計流程,從而縮短產品上市時間,或者在更短的時間內完成更為復雜的設計任務。

芯神鼎硬件仿真系統集多種創新技術于一身,如并行綜合、智能P&R和增量編譯等模塊,不僅大幅度縮短了編譯時間,還提高了整體編譯質量。這些模塊都運用了我們自主研發的先進技術,為客戶在超大規模集成電路驗證方面提供了強有力的支持。除了應對現有的編譯挑戰,我們的解決方案還具備極強的可擴展性,能夠適應未來更高復雜度的工程需求。

通過持續的研發和創新,芯神鼎硬件仿真系統有望成為推動整個集成電路設計行業進入新“智”元的重要力量,開啟一個全新的、以數據和算法為驅動的芯片設計時代。

-

芯片設計

+關注

關注

15文章

1028瀏覽量

55009 -

仿真

+關注

關注

50文章

4124瀏覽量

133995 -

硬件

+關注

關注

11文章

3382瀏覽量

66452 -

AI

+關注

關注

87文章

31530瀏覽量

270342

發布評論請先 登錄

相關推薦

VPS600超大規模無透鏡顯微成像芯片獲“中國芯”芯火新銳產品獎

Zettabyte與緯創攜手打造臺灣首個超大規模AI數據中心

谷歌正在考慮在越南建設超大規模數據中心

形式驗證如何加速超大規模芯片設計?

超大規模集成電路(VLSI)中不可或缺的5種二極管

如何利用低功耗設計技術實現超大規模集成電路(VLSI)的電源完整性?

AI驅動的國產硬件仿真芯神鼎如何加速超大規模芯片設計

AI驅動的國產硬件仿真芯神鼎如何加速超大規模芯片設計

評論