相關閱讀:

RA2快速設計指南 [2] MCU工作模式和選項設置存儲器

RA2快速設計指南 [3] 時鐘電路

RA2快速設計指南 [4] 復位要求和復位電路

RA2快速設計指南 [5] 存儲器

8. 寄存器寫保護

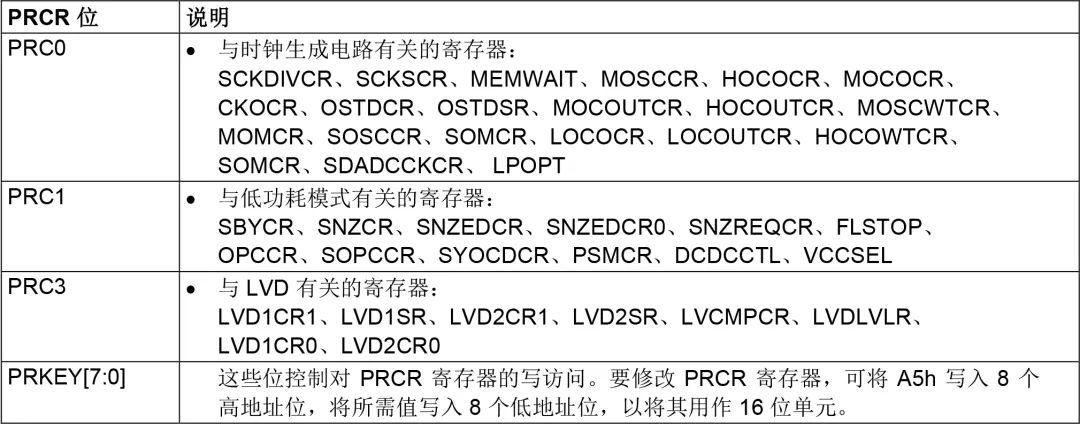

寄存器寫保護功能可防止重要寄存器因軟件錯誤而被覆蓋。使用保護寄存器(PRCR)設置要保護的寄存器。表9列出了PRCR位與要保護的寄存器之間的關聯。

圖18. PRCR寄存器

表9. PRCR保護位

注:以上寄存器并非存在于所有的RA2產品。具體請參照各MCU硬件手冊中“寄存器寫操作”的章節。

Renesas FSP提供兩個API(R_BSP_RegisterProtectEnable 和 R_BSP_RegisterProtectDisable),分別用于使能和禁用寄存器寫保護。

9. I/O 端口配置(1)

《硬件手冊》中的“I/O 端口”部分介紹了基于外設選擇和其他寄存器設置的確切引腳配置。下面列出了一些一般信息。

務必注意的是,復位后,在應用配置之前,每個引腳都將處于其默認狀態。就RA2產品而言,所有I/O引腳在復位后均為輸入引腳。其中某些引腳可能會短暫地處于無法預期的狀態。無論使用哪種配置方法,都會出現這種情況。用戶應考慮這可能對每種應用產生的影響,包括這可能對其他系統功能造成哪些影響。

配置I/O端口時,可以直接寫入寄存器,也可以通過FSP引腳配置功能進行配置。

9.1 多功能引腳選擇設計策略

RA2系列MCU上的大多數端口都具有多種外設功能。Renesas提供了諸如FSP中的引腳配置器之類的工具,以幫助選擇各RA2產品的端口。當需要多個外設功能時,請使用以下設計策略來幫助選擇端口功能。

? 首先,僅通過一個端口選項分配外設功能。例如,調試功能中的每個跟蹤數據信號只有一個端口選項。需要此功能時,先分配這些端口。

? 接下來,為外設功能分配有限的端口選項。例如,支持CLKOUT外設的產品的每個CLKOUT信號通常只有兩個選項。

? 最后,為外設功能分配多個端口選項。一個示例是串行通信接口(SCI),該接口通常具有許多可用的端口選項。

? 從RA2系列MCU硬件手冊“引腳列表”章節中可以看到一些端口的函數名稱中帶有后綴“_A”。為RA2

產品配置端口函數時,可以忽略此種類型的后綴。另請參見本系列文章后續的16.3節。

9.2 設置端口并將其用作GPIO

有兩種方法可以設置端口并將其用作GPIO:一種是使用端口控制寄存器(PCNTR1),另一種是使用PmnPFS寄存器。

方法1:端口控制寄存器(PCNTR1)

? 通過向端口控制寄存器1(PCNTR1)的端口方向位 (PDRn) 寫入“1”,選擇一個引腳作為輸出。

? 端口方向位 (PDRn) 是可讀寫的。將該值設置為“1”將選擇該引腳作為輸出。I/O端口的默認狀態為“0”(輸入)。可以在RA2 MCU上讀取端口方向寄存器。

? 相應端口控制寄存器 (PCNTR1) 中的端口輸出數據位 (PODRn) 是可讀寫的。讀取PODR時,也會讀取輸出數據鎖存器的狀態(不是引腳電平)。

? 端口控制寄存器 2 (PCNTR2) 中的端口輸入位 (PIDRn) 是只讀的。讀取PCNTR2寄存器中的 PIDRn 位以讀取引腳狀態。

方法2:端口mn引腳功能 選擇 (PmnPFS) 寄存器

? 端口模式寄存器 (PMR) 是可讀寫的,用于指定各個引腳是用作GPIO還是用作外設引腳。復位后,所有PMR寄存器均置0,這會將所有引腳都設置為GPIO。如果PMR寄存器置1,則該對應的引腳將用于實現外設功能。外設功能由該引腳的MPC設置定義。

? 將引腳設置為輸出時,建議先將所需的端口輸出值寫入數據鎖存器,然后將方向寄存器設置為輸出。盡管在所有系統中此操作都不太重要,但這可以防止在設置端口時出現意外的輸出毛刺。

通常,使用PCNTR1配置端口有助于提高訪問速度,但可用的配置功能較少。使用PmnPFS寄存器將獲得更多可用的配置功能,但訪問速度較慢。

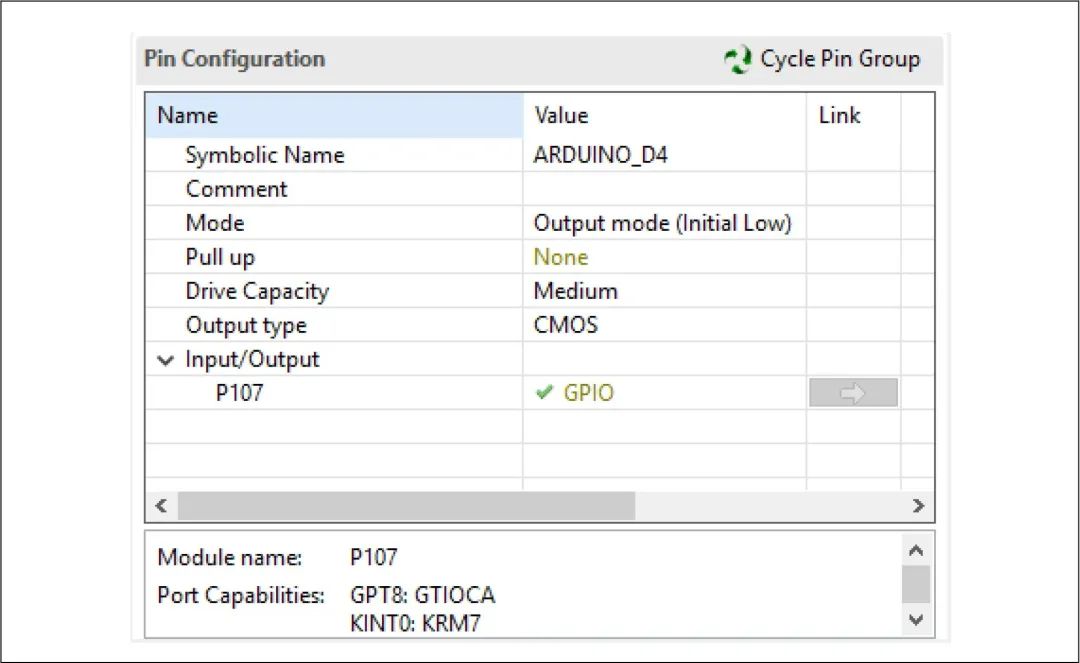

Renesas FSP提供了引腳配置工具,以在復位后配置GPIO引腳,如圖19所示。配置GPIO后,可以在FSP中使用HAL層API對該GPIO進行控制

圖19. 使用FSP配置器將P107配置為輸出和低電平

9.2.1 內部上拉

? 端口0到9上的大多數引腳都可以選擇使能上拉電阻。上拉由每個端口mn引腳功能選擇 (PmnPFS) 寄存器中的上拉 (PCR) 位控制。每個PmnPFS寄存器中的PCR位用于控制端口上的相應引腳。

? 首先,必須通過PmnPFS寄存器中的相關位將該引腳設置為輸入。將PCR位置“1”以使能上拉,將其置“0”以禁用上拉。

? 復位后,會將所有PCR寄存器清零,因此將禁用所有上拉電阻。

? 每當將某個引腳指定為外部總線引腳、GPIO輸出或外設功能輸出引腳時,上拉就會自動關閉。

9.2.2 漏極開路輸出

? 配置為輸出的引腳通常用作CMOS輸出。

? 端口0到上的大多數引腳都可以選擇配置為NMOS漏極開路輸出。

? 每個端口9mn引腳功能選擇 (PmnPFS) 寄存器中的N溝道漏極開路控制 (NCODR) 位控制哪些引腳以漏極開路模式工作。將每個寄存器中的適用位置“1”會使輸出形式變為漏極開路。將每個寄存器中的適用位置“0”會將端口設置為CMOS輸出。

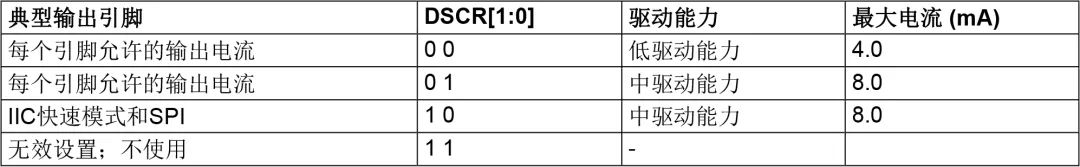

9.2.3 驅動能力

RA2A1產品可以使能驅動能力輸出,其驅動能力可設為低或中驅動能力輸出。其他RA2產品無此功能。

? 驅動能力的切換由每個端口mn引腳功能選擇 (PmnPFS) 寄存器中的驅動能力控制寄存器 (DSCR) 位控制。

? 復位后,會將所有DSCR寄存器清零,因此會將所有引腳設置為低驅動能力輸出。設置“00”以外的值會更改所選引腳的輸出的驅動能力。

? 引腳的最大總輸出因產品及封裝而異。具體請參見MCU硬件手冊“電氣特性”章節的內容。

? 驅動能力的差異如下所示。實際輸出電流會因產品和引腳類型而有所不同。詳細信息請參見MCU硬件手冊。

表10. 引腳驅動能力

輸出驅動能力可能會對電路板設計的整體性能造成重大影響。為每個輸出選擇驅動能力時,應考慮以下幾點:

? 建議首先將所有引腳設置為低驅動能力(默認)并評估性能。

? 根據電路板布局的不同,驅動能力設置為中或高的引腳可能會產生較高的EMI輻射。

? 較長的走線可能需要更高的驅動能力,才能使信號正確傳播到接收器。

9.3 設置和使用端口外設功能

端口mn引腳功能選擇寄存器 (PmnPFS) 用于配置每個端口的特性。PSEL 位用于選擇為每個端口選擇的外設功能。

? 由于大多數引腳具有多種功能,因此RA2 MCU提供了引腳功能控制寄存器 (PmnPFS),可用于更改分配給引腳的功能。

? 每個引腳都有自己的PmnPFS寄存器。

? 每個PmnPFS寄存器都允許將引腳用于外設功能(PSEL位)、用作IRQ輸入引腳(ISEL位)或用作模擬輸入引腳(ASE位)。如果ASEL位置“1”(將引腳用作模擬輸入引腳),則應將該引腳的PMR位置1以用于GPIO,并將該引腳的PDR位置1以用于輸入。

? 請參見《硬件手冊》中“I/O端口”一章的“每種產品的外設選擇設置”部分。

? 為了確保外設引腳上沒有非預期的邊沿輸入或輸出,確保在修改引腳的PmnPFS寄存器之前將目標引腳的端口模式控制 (PMR) 位清零。

? 復位后,所有PmnPFS寄存器均受到寫保護。為了對這些寄存器執行寫入操作,必須首先使用寫保護寄存器 (PWPR) 來使能寫入。

? 設置PmnPFS寄存器時應格外小心,切勿將一個功能分配給多個引腳。用戶不應這樣做,但MCU允許上述操作。如果發生這種情況,則引腳上的功能將處于未定義狀態。

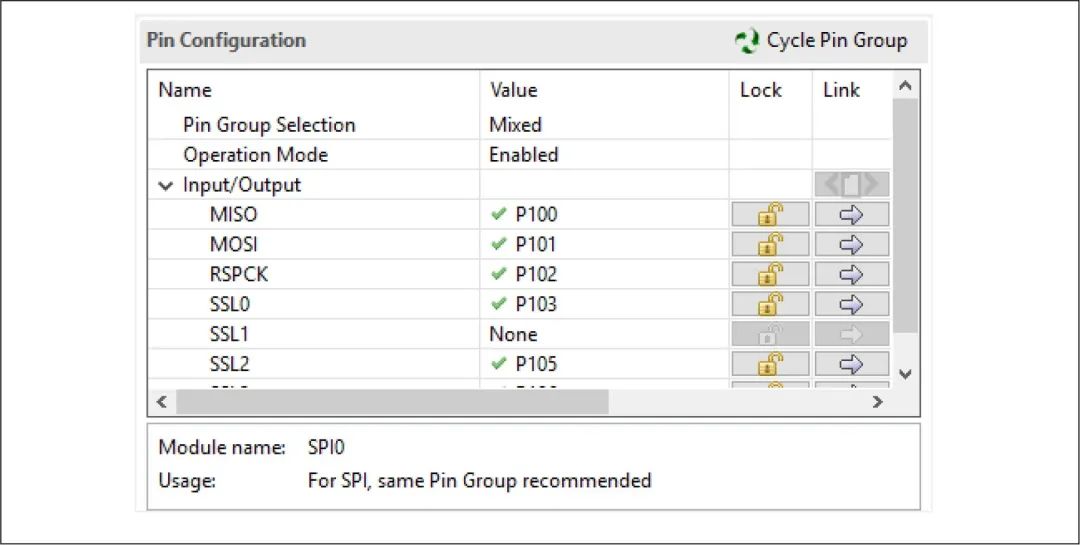

? 圖20為使用Renesas FSP的引腳配置器使能QSPI引腳的示例。

圖20. 使用Renesas FSP中的引腳配置器使能QSPI引腳

9.4 設置和使用IRQ引腳

? 某些端口引腳可以用作硬件中斷線(IRQ)。有關哪些引腳可用于您的MCU的信息,請參見《硬件手冊》中“I/O端口”一章的“每種產品的外設選擇設置”部分。

? 要將端口引腳設置為用作IRQ引腳,必須將其PFS寄存器中的中斷輸入功能選擇位(ISEL)置“1”。

? 引腳可同時用于IRQ和外設功能。要使能此功能,需設置引腳的PFS寄存器的ISEL位和PSE位。

? 具有相同編號的IRQ功能必須在一個引腳上使能。

? IRQ引腳可以在檢測到以下情況時觸發中斷:

? 低電平

? 下降沿

? 上升沿

? 上升沿和下降沿

使用IRQ控制寄存器(IRQCRi)選擇要使用的觸發器。

? 數字濾波可用于IRQ引腳。濾波器基于以四個可選時鐘速率(PCLKB、PCLKB/8、PCLKB/32、PCLKB/64)之一進行的重復信號采樣。它們可以濾除短脈沖:在特定濾波速率下,任何少于3個樣本的高脈沖或低脈沖。濾波器可用于濾除這些線路中的振鈴和噪聲,但是由于速率過快而無法濾除諸如機械開關彈跳之類的長時間事件。使能濾波會給硬件IRQ線增加一小段響應延遲時間(濾波時間)。

? 可以針對每個IRQ引腳單獨使能數字濾波。此過程通過設置每個IRQ的IRQCRi寄存器中的IRQ引腳數字濾波器使能(FLTEN)位來實現。

? 可為每個IRQ引腳單獨配置數字濾波的時鐘速率。此過程通過設置每個IRQ的IRQCRi寄存器中的IRQ引腳數字濾波器設置(FCLKSEL[1:0])位來實現。

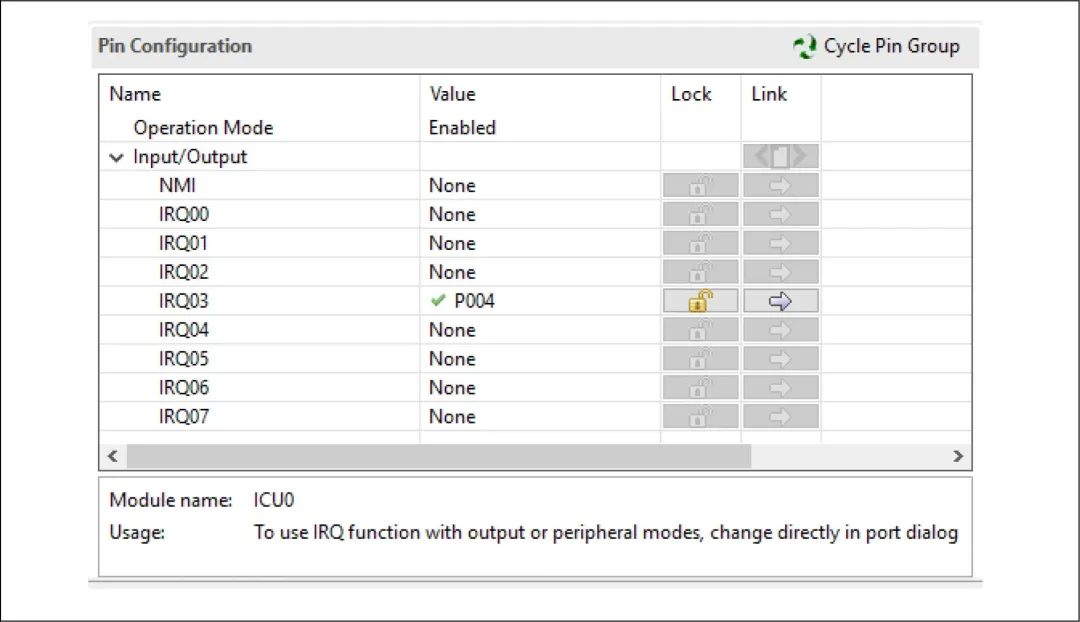

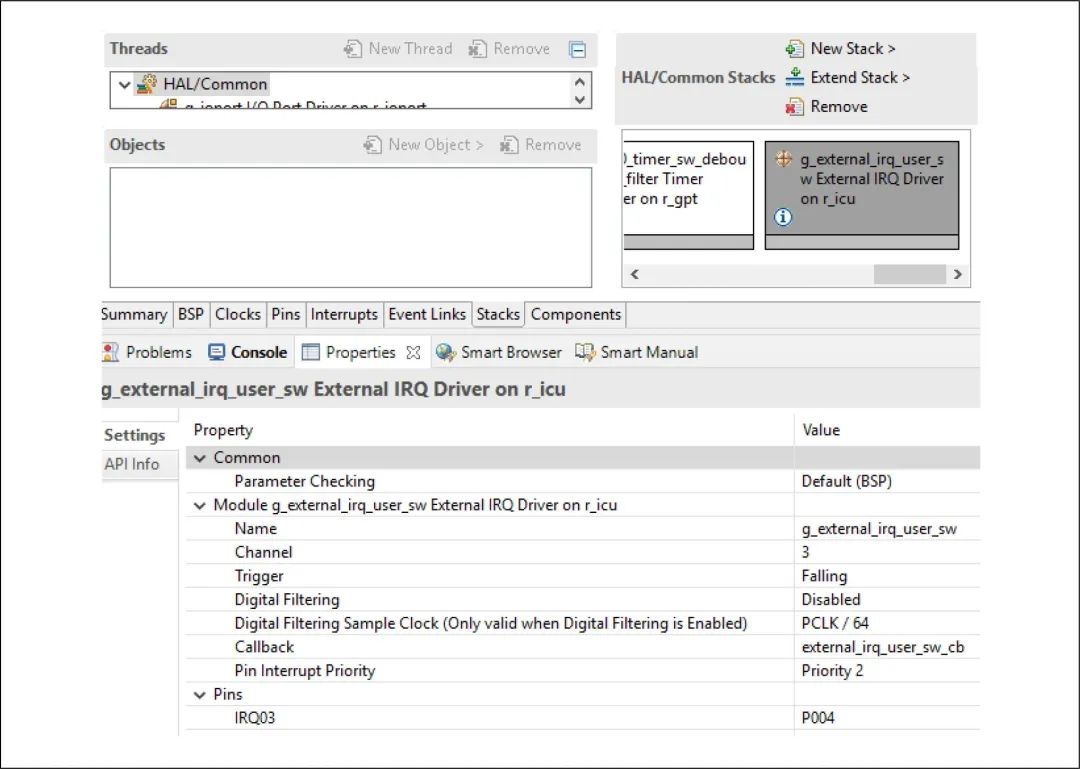

? 圖21和圖22給出了使用Renesas FSP使能和配置IRQ引腳的示例。

圖21. 使用Renesas FSP配置器將P004配置為IRQ03

圖22. 使用Renesas FSP配置器配置IRQ03

9.5 未使用引腳的處理

注:某些引腳需要特定的端接:有關具體建議,請參見《硬件手冊》中的“未使用引腳的處理”部分。

懸空的未使用引腳會消耗額外的功率,并使系統更容易受到噪聲問題的影響。使用下面詳述的方法之一對未使用的引腳進行處理:

1、第一種選擇是將引腳設置為輸入(復位后的默認狀態),然后使用電阻將其連接至Vcc或Vss。不同的連接方法對MCU來說沒有區別;但是,從系統噪聲的角度來看,有的方法可能更具優勢。Vss可能是最典型的選擇。避免將引腳直接連接到Vcc或Vss,因為對端口的方向寄存器(用于將端口設置為輸出)執行意外的寫入操作可能會導致輸出短路。

2、第二種方法是將引腳設置為輸出。無論是將引腳電平設置為高還是低都無關緊要;但是,將引腳設置為輸出并將輸出設置為低電平會在內部將引腳連接至接地層。這可能有助于解決整個系統的噪聲問題。將未使用的引腳設置為輸出有一個缺點,即必須通過軟件控制來完成端口配置。在將方向寄存器設置為輸出前MCU一直保持在復位狀態時,該引腳將為懸空輸入,可能會消耗額外的電流。如果可以接受在此期間消耗額外的電流,則該方法可消除第一種方法所需的外部電阻。

3、將引腳保留為輸入并使用外部電阻將它們處理的一種變化方式是使用MCU多個端口上的內部上拉電阻。這與將引腳設置為輸出有相同的限制(需要程序來設置端口),但是由于產品不會驅動引腳,因此確實可以減少因引腳意外接地、短接到相鄰引腳或Vcc而產生的影響。

9.6 不存在的引腳

每個RA2 MCU系列都有多種封裝尺寸,總引腳數也各有不同。對于小于該MCU系列最大封裝尺寸(通常為100引腳、64引腳、24引腳)的任何封裝,需將PDR寄存器中不存在的端口的對應位置“1”(輸出),并將PODR寄存器中不存在的端口的對應位置“0”。通過查看《硬件手冊》中“I/O端口”部分的“I/O端口規范”表,用戶可以查看每個MCU封裝上可用的端口。例如,端口0上的P007和P008僅在100引腳封裝中可用。請注意,不需要對不存在的引腳進行額外處理。

9.7 電氣特性

常規GPIO端口通常需要CMOS電平輸入(高電平≥ 0.8 * Vcc,低電平≤ 0.2 * Vcc)。某些GPIO端口具有施密特觸發輸入,在輸入要求方面略有不同。有關更多信息,請參見《硬件手冊》中的“電氣特性”部分。

來源:瑞薩MCU小百科

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理

審核編輯 黃宇

-

寄存器

+關注

關注

31文章

5363瀏覽量

121161 -

端口

+關注

關注

4文章

990瀏覽量

32207

發布評論請先 登錄

相關推薦

TCA6424A低電壓24位I2C和SMBus I/O擴展器具有中斷輸出、復位和配置寄存器數據表

TCA9534A具有中斷輸出和配置寄存器的低壓8位I2C和系統管理總線(SMBUS)低功耗輸入輸出(I/O)擴展器數據表

TCA9554A具有中斷輸出和配置寄存器的低壓8位I2C和SMBus低功耗I/O擴展器數據表

具有中斷輸出和配置寄存器的PCA9554遠程8位I2C和SMBus I/O擴展器數據表

PCA9554A具有中斷輸出和配置寄存器的遠程8位I2C和SMBus I/O擴展器數據表

具有中斷輸出和配置寄存器的 PCA9534A遠程8位I2C和SMBus 低功耗 I/O 擴展器數據表

具有中斷輸出、復位和配置寄存器的PCA9539遠程16位I2C 和SMBus 低功耗 I/O 擴展器數據表

具有中斷輸出和配置寄存器的 PCA9535 遠程 16位I2C和SMBus I/O擴展器數據表

具有中斷輸出、復位引腳和配置寄存器的TCA9539-Q1汽車類低壓16位 I2C 和 SMBus低功耗 I/O 擴展器數據表

具有中斷輸出和配置寄存器的PCA9555遠程16位I2C和 SMBus I/O擴展器數據表

TCA9537具有配置寄存器的遠程4位I2C和SMBus I/O擴展器數據表

PCA9536具有配置寄存器的遠程4位I2C和SMBus I/O擴展器數據表

TCA9536具有配置寄存器的遠程4位I2C和SMBus I/O擴展器數據表

TCA9535具有中斷輸出和配置寄存器的低電壓16位I2C和SMBus低功耗I/O擴展器數據表

RA2快速設計指南 [6] 寄存器寫保護和I/O端口配置

RA2快速設計指南 [6] 寄存器寫保護和I/O端口配置

評論