簡介

高速數(shù)字電路電源完整性精確測量一直是個難題,以前大部分研發(fā)單位和公司并不進(jìn)行這些電源完整性參數(shù)的測量。但是,隨著數(shù)字信號速率的不斷提升,特別是提升到 10Gbps 以上數(shù)量級后,電源完整性的測量成為關(guān)鍵測試項目之一,另外芯片和 CPU 的供電電平也越來越小,使得它對電平的變化更加敏感。因而,近來不斷地遇到客戶咨詢電源完整性的測試方案,所以是德科技的技術(shù)工程師們把電源完整性測試系統(tǒng)的技術(shù)背景和方案配置和關(guān)鍵性能指標(biāo)整理如下。

電源完整性測量對象和測量內(nèi)容

PI (Power Integrity),即電源完整性,以前隸屬于信號完整性分析專題,但是因為 PI 足夠復(fù)雜和關(guān)鍵,現(xiàn)在已經(jīng)把其單獨拿出來作為一個專題去研究。快速而準(zhǔn)確的仿真電源完整性至今仍然是一個有待突破的難題 (是德科技的 ADS 高級仿真軟件有專門支持電源完整性的方案)。

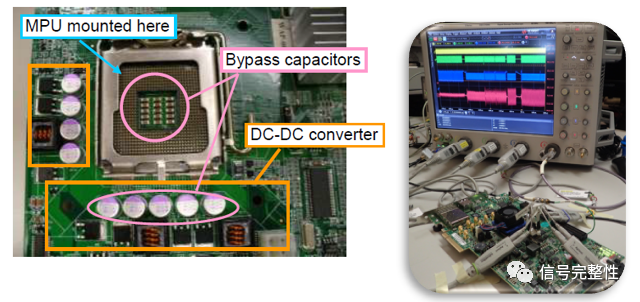

對于高速數(shù)字電路和系統(tǒng),電源完整性(PI)的研究對象是電源分配網(wǎng)絡(luò) PDN(Power Distribution Network)。以筆記本電腦為例,AC 到 DC 電源適配器供給計算機主板的是一個約 16V 的直流電源,主板上的電源分配網(wǎng)絡(luò)要把這個 16V 直流電源變成各種電壓的直流電源(如:±5V, +1.5V, +1.8V, +1.2V 等),給 CPU 供電,給各個芯片供電。CPU 和 IC 用電量很大,而且是動態(tài)耗電的,瞬時電流可能很大,大到幾十甚至 100 多安培,也可能很小,小到低于 1mA,但無論電流如何變 化,電壓必須平穩(wěn)(即紋波和噪聲必須較小),以保持 CPU 和 IC 的正常工作,這都對 PDN 提出了苛刻的要求。我們常見的電腦藍(lán)屏現(xiàn)象,往往和電源完整性密切相關(guān),傳統(tǒng)的方案有很多局限性,我們希望隨著 Keysight 的優(yōu)異方案的普及,電腦藍(lán)屏和其它電源完整性現(xiàn)象逐漸減少。

1. 電源完整性測試系統(tǒng)關(guān)鍵性能指標(biāo):

紋波測試能力:<=3mv(P-P),具體取決于具體的被測對象,也有場合是 20mV 左右。

阻抗測試能力:1 毫歐 ~ 50K 歐姆

頻率范圍:5Hz ~ 3GHz

基本測試精度:±2%

SMD 器件測試能力:頻率 DC ~ 3GHz

引腳器件測試能力:頻率 DC ~ 110MHz

直流偏置范圍:0 ~ ±40V

2. 電源完整性測試系統(tǒng)實現(xiàn)的測試功能:

電源紋波/噪聲/串?dāng)_測量,干擾源定位

直流-直流轉(zhuǎn)換器環(huán)路增益(幅度和相位)測量

PDN(電源分配網(wǎng)絡(luò))毫歐姆級阻抗測量

濾波電容/旁路電容/磁珠等用于電源分配網(wǎng)絡(luò)的器件的阻抗和參數(shù)測量

激勵響應(yīng)測試

電源完整性仿真

第一章 電源完整性時域分析之示波器

電源紋波和噪聲測量

今天的電子電路(比如手機、服務(wù)器等領(lǐng)域)的切換速度、信號擺率比以前更高,同時芯片的封裝和信號擺幅卻越來越小,對噪聲更加敏感。因此,今天的電路設(shè)計者們比以前會更關(guān)心電源噪聲的影響。實時示波器是用來進(jìn)行電源噪聲測量的常用工具,但是如果使用方法和工具不對可能會帶來完全錯誤的測量結(jié)果。

工程師選擇示波器做電源噪聲測量的一個原因是電源噪聲帶寬很寬,但是不能忽略的是,實時寬帶數(shù)字示波器以及其探頭都有其固有的噪聲。如果要測量的噪聲與“示波器和探頭”的噪聲在相同數(shù)量級,那么要進(jìn)行精確測量將是非常困難的一件事情。

示波器的主要噪聲來源于 2 個方面:示波器本身的噪聲和探頭的噪聲。

所有的實時示波器都使用衰減器和放大器來調(diào)整垂直量程,在不同的量程設(shè)置下,其對應(yīng)的放大比或衰減比是不同的,示波器的本底噪聲也是不同的。以 Infiniium S 系列示波器的 2.5GHz 型號DSOS254A 為例,在滿帶寬,2mV/div 設(shè)置下,其本底噪聲是 120uVrms,在 10mV/div 設(shè)置下,其本底噪聲就變?yōu)?172uVrms,表 1 是 S 系列示波器在不同量程設(shè)置下的本底噪聲。從該表 1 我們可以得出一個結(jié)論,測量噪聲時應(yīng)盡可能使用示波器最靈敏,也就是最小,的量程檔。但是示波器在最靈敏檔下通常不具有足夠的偏置范圍可以把被測直流電壓拉到示波器屏幕中心范圍進(jìn)行測試,表 2 是常見示波器支持的偏置范圍,從表 2 我們可以得出第二個結(jié)論,沒有一臺示波器支持的偏置范圍可以覆蓋常見的直流電源被測對象,因此通常需要利用 N7020A 這樣的電源完整性專用探頭將直流偏置范圍提升到+/-24V,否則,你要么使用 AC 耦合把直流電平濾掉只測量 AC 成分,要么使用隔直電容來完成測試, 但所有示波器僅在 1M 歐姆輸入阻抗情況下支持 AC 耦合,在此條件下,示波器帶寬會降到 500MHz,示波器自身的本底噪聲會變大;使用隔直電容的缺點是將直流成分去掉的同時,也會把極低頻信號濾 除,電源信號本身就是低頻的,所以有機會把諸如電壓緩慢跌落等現(xiàn)象掩蓋了。表 1-1:Infiniium S 系列示波器在不同量程設(shè)置下的本底噪聲,適用于電源完整性測試的設(shè)置最多只有 4 個,在圖中以綠色標(biāo)示。大部分情況下,應(yīng)該使用每格 1mV~10mV 的設(shè)置。

| 量程設(shè)置 | DSOS054A | DSOS104A | DSO204A | DSOS254A | DSOS404A | DSOS604A | DSO804A |

| 每格 1mV | 74uVrms | 90uVrms | 120uVrms | 130uVrms | 153uVrms | 195uVrms | 260uVrms |

| 每格 2mV | 74uVrms | 90uVrms | 120uVrms | 130uVrms | 153uVrms | 195uVrms | 260uVrms |

| 每格 5mV | 77uVrms | 94uVrms | 129uVrms | 135uVrms | 173uVrms | 205uVrms | 320uVrms |

| 每格 10mV | 87uVrms | 110uVrms | 163uVrms | 172uVrms | 220uVrms | 256uVrms | 390uVrms |

| 每格 20mV | 125uVrms | 163uVrms | 233uVrms | 254uVrms | 650uVrms | 446uVrms | 620uVrms |

| 每格 50mV | 372uVrms | 456uVrms | 610mVrms | 650uVrms | 1.3mVrms | 1.3mVrms | 1.4mVrms |

| 每格 100mV | 0.78mVrms | 0.96uVrms | 1.2mVrms | 1.3mVrms | 2.8mVrms | 2.3mVrms | 3.1mVrms |

| 每格 200mV | 1.6mVrms | 2.0mVrms | 2.6mVrms | 2.8mVrms | 6mVrms | 4.9mVrms | 6.4mVrms |

| 每格 500mV | 3.5mVrms | 4.2mVrms | 5.5mVrms | 6mVrms | 10.1mVrms | 10.0mVrms | 13.3mVrms |

| 每格 1V | 5.1mVrms | 6.8mVrms | 9.2mVrms | 10.1mVrms | 12.5mVrms | 17.6mVrms | 24.1mVrms |

表 1-1:對于電源紋波測試,建議使用最靈敏的垂直刻度,盡可能使用示波器的小量程,否則,示波器自身的本底噪聲會帶來較大的測量誤差,該表給出 Infiniium S 系列示波器在不同量程設(shè)置下的本底噪聲,因其內(nèi)部采用真實的硬件 10-bit 40GSa/s ADC,其指標(biāo)遠(yuǎn)高于其它示波器。

10 bits 的示波器,Infiniium S 系列示波器,其噪聲相對小的多,而且硬件支持 2mV/div 的靈敏度,所以,放棄 8 比特,采用 10 bits 示波器,是最好的選擇。

世面上也有一些其它 12 bits 的示波器,或者由于其內(nèi)部 ADC 是商用產(chǎn)品或者由于其 ADC 本身是 8bit(2G 帶寬 6.25GSa/s 時只有 8bit)采用低帶寬的 ADC 拼接技術(shù)因而本底噪聲偏大,在和示波器自身硬件配合之后,其實際有效位比 Infiniium S 系列示波器要低 1 bit 左右,另外也不支持下一章介紹的電源完整性專用高阻探頭。

第二章 電源完整性時域分析之專用測試探頭

基于同樣的原因,在電源測量中也應(yīng)該盡量使用 1:1 的探頭而不是示波器標(biāo)配的 10:1 的探頭, 使用 10:1 的探頭,示波器的最小量程會被放大十倍,示波器的噪聲也會被放大。目前 N7020A 2GHz 1:1 單端有源探頭,N2820A探頭 500KHz~ 3MHz 帶寬,衰減比為 1:330,最小可測信號電壓為 3uV,電流為500nA,N2870A 1:1 35MHz 無源探頭是最常被工程師認(rèn)可的探頭。其中 N7020A 是最適合電源完整性測試的探頭,可測量毫伏以及亞毫伏級的信號,N2870A 是最便宜的探頭,可測量 10mV 或以上的信號,N2820A 是最精密的探頭,即可用作差分探頭,也可用作電流探頭,電壓測量范圍為 3 uV~1.2 V,電流測量范圍為 500nA~5A,但帶寬僅為 500 KHz~3 MHz 。

探頭帶來的噪聲是在衰減器前面耦合進(jìn)來的,在某些不正確的使用方法下,探頭可能會帶來額外的噪聲,一個典型的例子就是使用長地線。為了方便測試,示波器的的無源探頭通常會使用 15cm 左右的鱷魚夾形式的長地線,這對于電源紋波的測試是不適用的,特別是板上存在開關(guān)電源的場合。由于開關(guān)電源的切換會在空間產(chǎn)生大量的電磁輻射,而示波器探頭的長地線又恰恰相當(dāng)于一個天線,所以會從空間把大的電磁干擾引入測量電路。一個簡單的驗證方法就是把地線和探頭前端接在一起,靠近被測電路(不直接接觸)就可能在示波器上看到比較大的開關(guān)噪聲。因此測量過程中應(yīng)該使用盡可能短的地線。

現(xiàn)在很多被測件要求測量出峰峰值為幾毫伏的紋波和噪聲,比如有些 10Gbps 以上的 SerDes 要求 3mv 峰峰值的電源紋波和噪聲。這時候最好用 N7020A 來進(jìn)行測量,它的直流阻抗為 50K 歐姆,對于毫歐甚至更高阻抗級別的被測電源來說,負(fù)載影響很小,測試精度非常高。

最后要注意的一點是,通常電源測試都規(guī)定了某個頻率范圍內(nèi)的紋波和噪聲,比如 20MHz 以內(nèi)的,但為了分析電源噪聲來源,需要在更寬的頻率范圍內(nèi)分析,一般示波器的帶寬在滿足分析要求的同時,還要支持靈活的帶寬限制功能,這對于減小高頻噪聲會有比較好的效果。

小結(jié)一下,對于電源紋波噪聲的測試,通常需要注意以下幾點:

盡量不使用 8bits 示波器,而用S 系列 10 比特示波器

盡量使用專用的電源測試探頭 N7020A

盡量使用小衰減比的探頭,如 N7020A, N2820A,N2870A;

盡量使用示波器最小量程(硬件實現(xiàn)的量程,不是軟件放大),以降低示波器本底噪聲;

探頭的接地線盡量短,構(gòu)成的環(huán)路面積盡可能小

根據(jù)需要使用帶寬限制功能,低通濾波器和高通濾波器,甚至帶通濾波器。

另外 N7020A 探頭還支持選配 N7023A 點測套件,該套件提供了全系列的靈活的連接附件,除了傳統(tǒng)的無源探頭探頭針尖和彈簧地針外還配有雙列直插式探針,以及小夾子,可直接夾在最小達(dá) 0201 封裝的貼片元件上。

第三章 電源完整性頻域分析之網(wǎng)絡(luò)分析儀

要測量 PDN 性能,首先需要用示波器測試 CPU 和 IC 管腳的電源紋波和噪聲。但是要精確衡量PDN 的性能,還需要測試PDN 的輸出阻抗(隨頻率變化的阻抗)和PDN 的傳輸阻抗(也是隨頻率變化的阻抗),就像表征一個單端口網(wǎng)絡(luò)或雙端口網(wǎng)絡(luò)一樣去表征 PDN。由于現(xiàn)在的 PDN 大都是開關(guān)電源結(jié)構(gòu),還需要測量PDN 或關(guān)鍵 DC 到 DC 轉(zhuǎn)換器件的環(huán)路增益。

小結(jié)一下,電源完整性的測量對象是電源分配網(wǎng)絡(luò) PDN。主要測量內(nèi)容包括四部分:

紋波和噪聲的測量;

輸出阻抗的測量;

環(huán)路增益的測量;

濾波器件(電容/磁珠等)性能參數(shù)的測量。

電源完整性測試挑戰(zhàn)和方法:毫歐級電源分配網(wǎng)絡(luò) PDN 的輸出阻抗和傳輸阻抗測量

電源完整性分析對象主要是電源分配網(wǎng)絡(luò) PDN(Power Distribution Network)。要衡量 PDN 性能,只用示波器測試 CPU 和 IC 管腳的電源紋波和噪聲是不夠的,而且出現(xiàn)問題后也沒有辦法定位問題。要精確衡量 PDN 的性能,還需要測試 PDN 的輸出阻抗(隨頻率變化的阻抗)和 PDN 的傳輸阻抗(也是隨頻率變化的阻抗),就像表征一個單端口網(wǎng)絡(luò)或雙端口網(wǎng)絡(luò)一樣去表征PDN。這就要用到網(wǎng)絡(luò)分析儀工具。

用網(wǎng)絡(luò)分析儀去測試 PDN,有兩大挑戰(zhàn):

1、PDN 的輸出阻抗和傳輸阻抗是豪歐級的,想準(zhǔn)確測試,是一件比較困難的事情。

2、PDN 工作時是帶直流電壓的,即帶偏置的,需要網(wǎng)絡(luò)分析儀有偏置測量的功能。

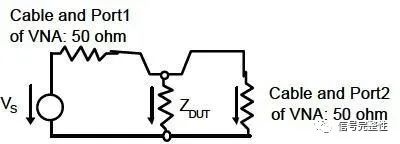

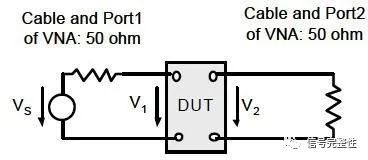

圖 3-1. 用雙端口方法測試 PDN 輸出阻抗

用網(wǎng)絡(luò)分析儀測試毫歐級的輸出阻抗,不能簡單的用一端口測試方法,因為阻抗太小,反射太大。這時比較好的方法是用雙端口測試方法,如圖 3-1 所示。測試時用 S21 代替 S11。

假設(shè)探測試電纜電感約為 0,Z(DUT)遠(yuǎn)小于 Zo(VNA 端口阻抗),PDN 輸出阻抗的計算公式如下:

Z(DUT)=Z11=S21*25(ohm)

用網(wǎng)絡(luò)分析儀測試毫歐級的輸出阻抗,也是用雙端口測試方法,如圖 3-2 所示。

圖 3-2. 用雙端口方法測試 PDN 的傳輸阻抗

假設(shè)探測試電纜電感約為 0,Z11,Z21,Z22 遠(yuǎn)小于 Zo,PDN 傳輸阻抗的計算公式如下:

Z21=Z12=S21*25(ohm)

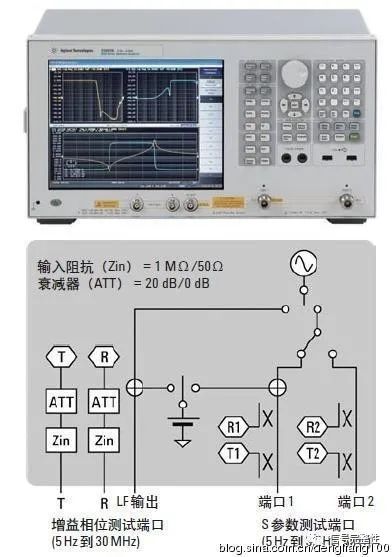

針對這種的特殊測量要求,是德科技的矢量網(wǎng)絡(luò)分析儀 E5061B 推出了一個特殊的選件 3L5 幫助測試PDN。

1、功能全面的低頻到中頻網(wǎng)絡(luò)分析儀

圖 3-3. E5061B-3L5 網(wǎng)絡(luò)分析儀

E5061B 低頻 - 射頻網(wǎng)絡(luò)分析儀的選件 3L5 可以在從 5 Hz 至 3 GHz 的率范圍內(nèi)提供常用的網(wǎng)絡(luò)測量和分析功能。功能全面的低頻網(wǎng)絡(luò)測量能力 (包括內(nèi)置的 1 MΩ 輸入) 都被完美地集成到這個高性能的射頻網(wǎng)絡(luò)分析儀之中。E5061B-3L5 是研發(fā)環(huán)境中進(jìn)行器件和電路測量的理想儀表和工具,選件 005 提供阻抗參數(shù)和等效電路分析。

2、S 參數(shù)測試端口

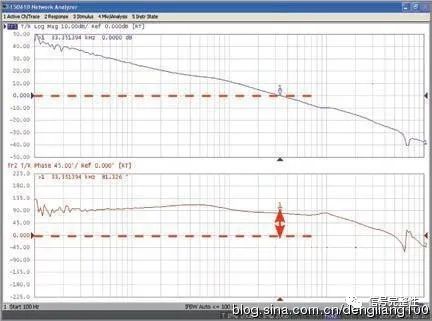

圖 3-4. 使用 S 參數(shù)測試端口 S21

E5061B-3L5 在其完全能夠測量的從 5 Hz 到 3 GHz 的頻率范圍都有非常高的動態(tài)范圍,這可以使您對各種幾乎從直流到射頻的器件進(jìn)行測試。

3、增益相位測試端口是德科技:雙端口測量和 S參數(shù) - 靈活應(yīng)用網(wǎng)絡(luò)分析儀3、增益相位測試端口

圖 3-5. 直流到直流傳輸阻抗測量和環(huán)路增益測量

增益相位測試端口可以在從 5 Hz 到 30 MHz 的低頻測量范圍內(nèi)直接把測試信號接入測量接收機。內(nèi)置的 1 MΩ輸入使您能夠使用測量探頭輕松地對所測電路內(nèi)的放大器和直流 - 直流轉(zhuǎn)換器的控制環(huán)路的參數(shù)進(jìn)行測量。接收機端口可以精確地測量放大器的 CMRR/PSRR 和 PDN 毫歐量級的輸出阻抗,并且消除了測量中接地環(huán)路引入的測量誤差。

4、直流偏置源

E5061B-3L5 內(nèi)置的直流偏置源可以從儀表內(nèi)部把最高可達(dá) ±40 Vdc 的直流偏置電壓疊加到從端口 1 或 LF OUT 端口上輸出的交流信號上。此外,如果在儀表的 S 參數(shù)測試端口上對被測器件進(jìn)行測量時,它還可以從 LF OUT 端口輸出直流電壓。

小結(jié):E5061B-3L5 是專門針對測試 PDN 而設(shè)計的網(wǎng)絡(luò)分析儀,滿足測量 PDN 輸出阻抗和傳輸阻抗的測量要求。

第四章 電源完整性仿真之仿真軟件

電源完整性的仿真

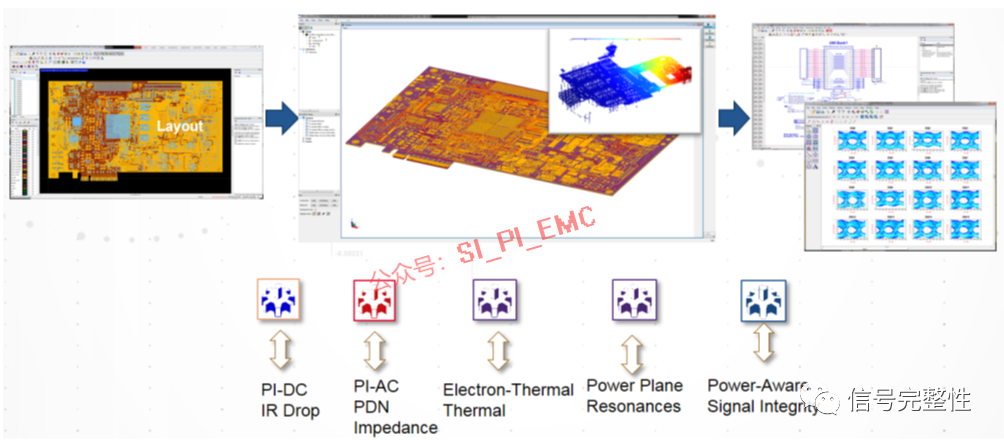

是德科技 EEsof 軟件家族中的 ADS(Advanced Design System)是一個完整的高速電路仿真設(shè)計平臺, 提供了完整的電源完整性設(shè)計解決方案。ADS 的版圖設(shè)計環(huán)境集成了 SIPro/PIPro 仿真分析工具,通過對電源完整性進(jìn)行仿真, 可以完成以下工作:

直流電壓降分析

PCB溫度分布情況

PDN 阻抗提取與去耦電容優(yōu)化

電源平面諧振分析

與電源相關(guān)的信號完整性分析, 如開關(guān)同步噪聲(SSN)

SI/PIPro 仿真分析工具包含以下功能:

PI-DC ,用于直流電壓降分析

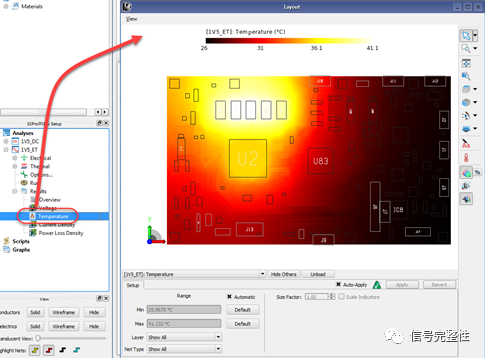

PI-ET,用于電熱聯(lián)合仿真分析

PI-AC, 用于PDN 阻抗分析

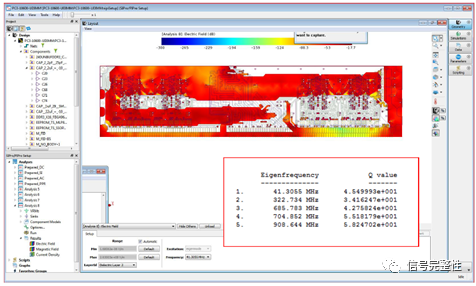

PPR(Power Plane Resonance Analysis) ,用于電源平面諧振分析

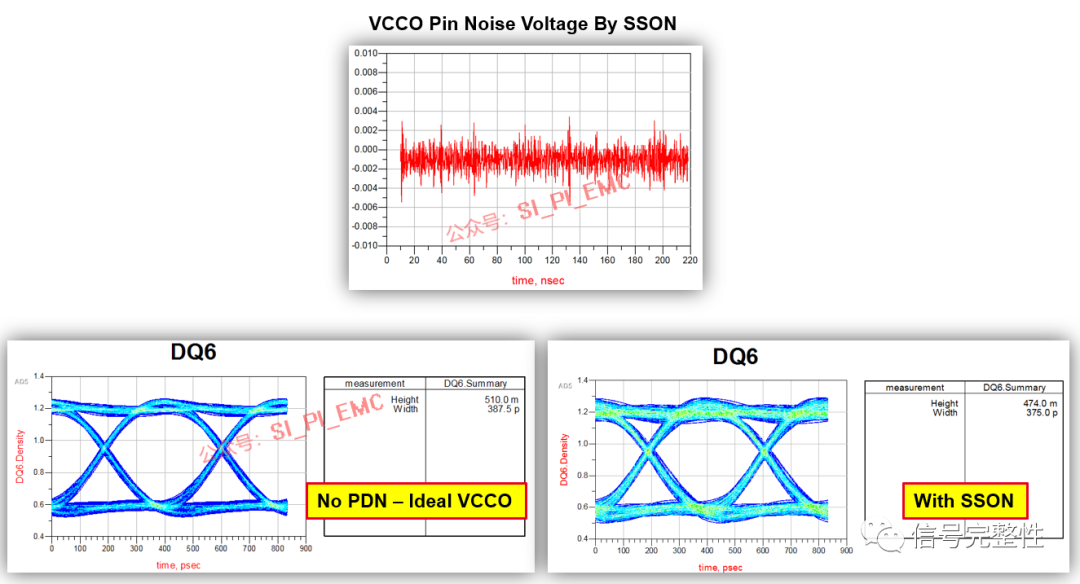

SIPro(Power-Aware Signal Integrity Analysis),用于與電源相關(guān)的信號完整性分析。

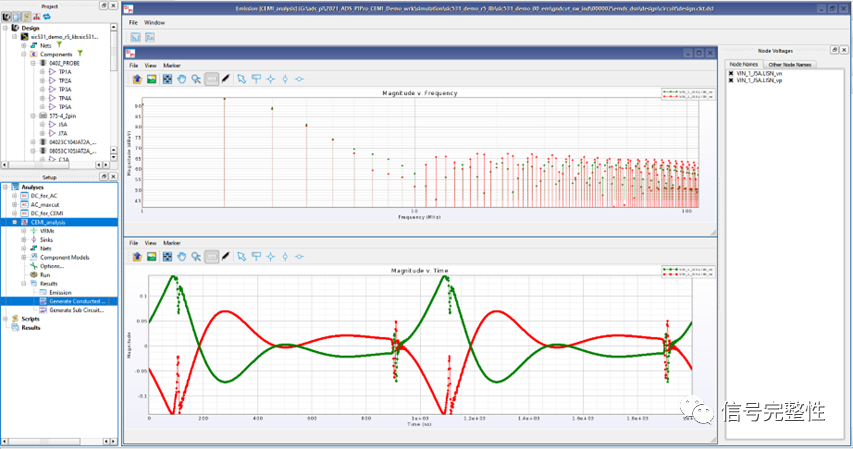

CEMI,用于電源傳導(dǎo)仿真分析。

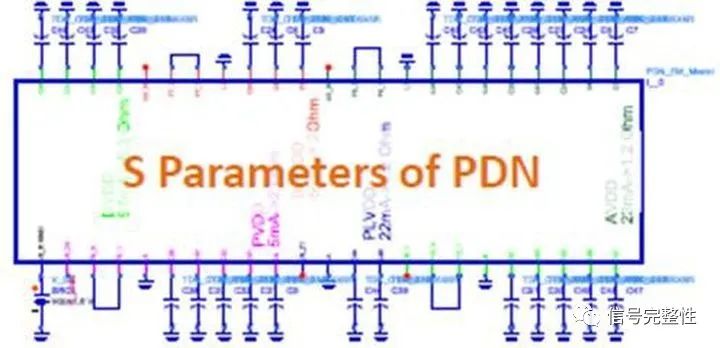

下圖 4-1 演示了 SI/PIPro 的軟件界面仿真能力。

圖 4-1SI/PIPro 的軟件界面

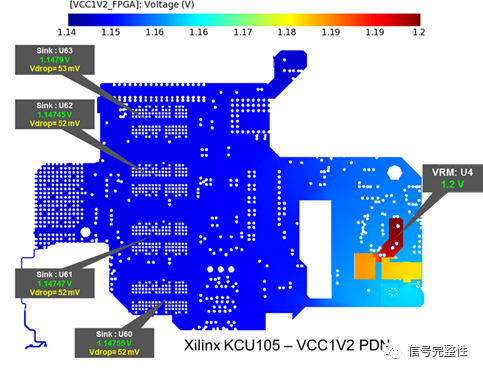

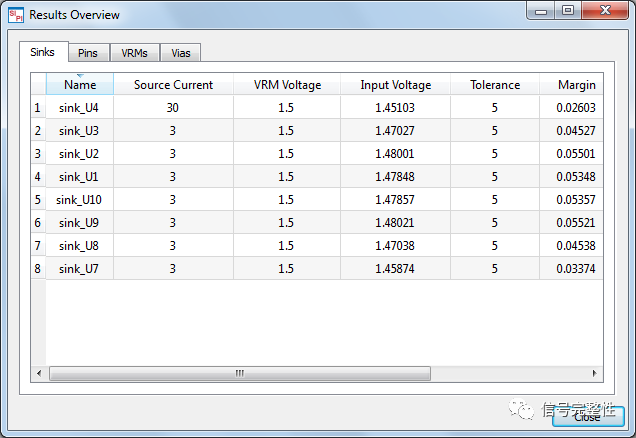

PI-DC 分析

由于過大的直流電壓降,落在IC 電源端的電壓可能低于建議的最低電壓。這可能導(dǎo)致 IC 的故障。過高的電流密度在過孔處會生成過多的熱量,引起電路板裂開或燒化,導(dǎo)致故障。PI-DC 可以計算直流條件下的電壓、 電流,IR Drop (電壓降)、 電源供應(yīng)網(wǎng)功率損耗密度等。它可以幫助你識別IC 和連接器的管腳和連接過孔等在直流工作條件下流過的電流密度,顯示芯片管腳電壓, 并給出設(shè)計裕量。

(a)

(b)

圖 4-2 直流電壓降分析結(jié)果

PI-AC 分析

PI-AC 分析用于提取PDN 阻抗特性,并且可以顯示電流密度, 了解熱點區(qū)域。提取的阻抗網(wǎng)絡(luò)可以直接轉(zhuǎn)化為 ADS 的原理圖,與電壓調(diào)節(jié)模塊(VRM)模型和去耦電容進(jìn)行優(yōu)化。

去耦電容優(yōu)化的目的是達(dá)到目標(biāo)阻抗的要求。目標(biāo)阻抗可以通過以下公式計算:

其中,? 表示最大允許的電源紋波, 是最大瞬態(tài)電流波動,通常設(shè)置為芯片最大電流的一半。

圖 4-3 提取的 PDN 阻抗網(wǎng)絡(luò)與 VRM 和去耦電容的聯(lián)合仿真

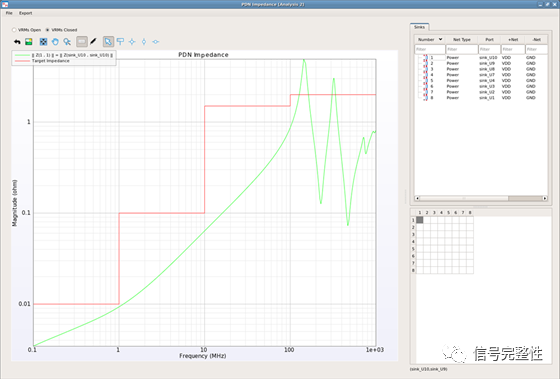

圖 4-4 仿真的 PDN 阻抗結(jié)果

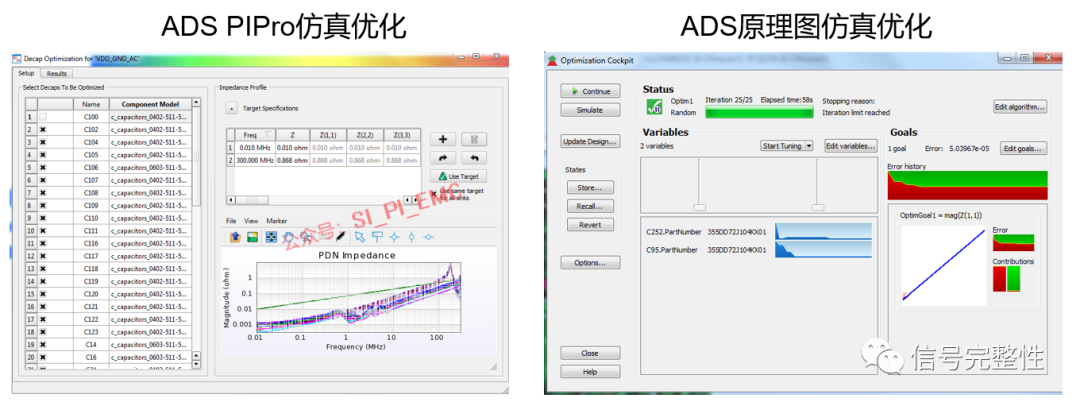

ADS 提供了 10 余種優(yōu)化方法, 可以實現(xiàn)去耦電容參數(shù)的快速搜索,實現(xiàn)最佳性能。通過分析去耦電容通過電流的大小, 可以剔除冗余電容, 降低設(shè)計成本。

圖 4-5 PDN 阻抗的優(yōu)化

電源平面諧振(PPR) 分析

電源平面諧振分析可以計算配電網(wǎng)絡(luò)(PDN)的自諧振頻率和相應(yīng)的 Q 值。它可以幫助你實現(xiàn)去耦電容和過孔的優(yōu)化布置。電源平面諧振會干擾敏感的模擬電路,并生成過量的輻射。這可能導(dǎo)致設(shè)計不能滿足 EMC 規(guī)范。

圖 4-6電源平面諧振分析

電熱聯(lián)合仿真

電源完整性分析中還集成了電熱仿真功能,能夠?qū)崿F(xiàn)電/ 熱協(xié)同仿真。電源完整性仿真引擎(DC Drop) 對電源網(wǎng)絡(luò)進(jìn)行仿真,提供功率密度給熱分析器,熱分析器再根據(jù)器件功耗運行熱分析,系統(tǒng)多次迭代上述過程,獲取更新后的溫度值直到仿真收斂。電熱聯(lián)合仿真溫度顯示分布圖

圖 4-7PCB電熱聯(lián)合仿真分析

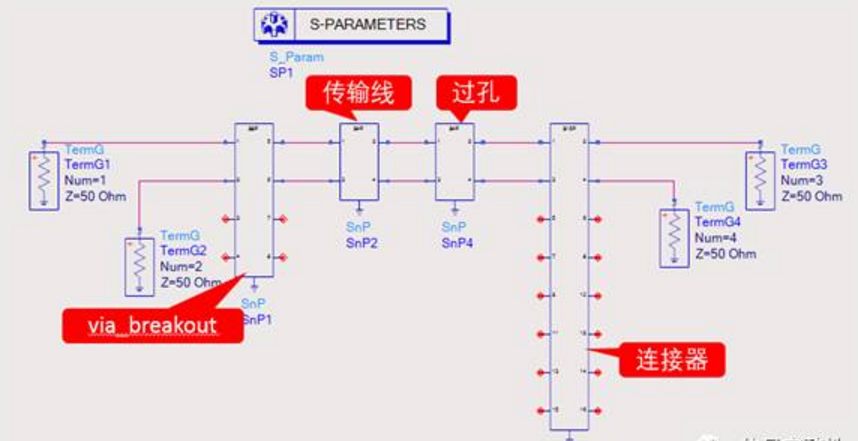

與電源相關(guān)的信號完整性分析(SIPro)

SIPro 使用獨有的混合算法,可以同時快速提取信號走線(包含過孔)與電源平面的頻域模型。這一頻域模型可以直接轉(zhuǎn)換成 ADS 的原理圖, 用于電路仿真, 如時域瞬態(tài)(Transient)仿真, 通道(Channel) 仿真, DDR 總線仿真等。

開關(guān)同步噪聲(SSN)是電源噪聲的主要來源,也是造成信號完整性性能下降的重要問題。要進(jìn)行 SSN 分析, 需要有詳細(xì)的元器件模型(通常是 SPICE 模型), 這類模型通常難以從芯片廠家直接獲得,并且仿真時間很長。IBIS 模型是由 IBIS Forum 提出的一種行為級模型, 它通過 I-V 和V-T 曲線表征芯片輸入輸出 Buffer 特性, 不涉及元器件的內(nèi)部電路設(shè)計, 能夠有效保護(hù)廠家的知識產(chǎn)權(quán), 因此, 芯片廠家更愿意提供 IBIS 模型給用戶進(jìn)行信號完整性的設(shè)計。IBIS 5.0 和 5.1 的標(biāo)準(zhǔn)中提出了多個新特性(BIRD95.6,98.3,141), 用于支持對芯片電源特性的描述。ADS 軟件在業(yè)界率先實現(xiàn)了對以上新特性的支持,解決了之前的 IBIS 模型不能用于電源完整性分析的問題。

圖 4-8 支持電源特性的 IBIS 模型仿真結(jié)果

傳導(dǎo)仿真分析(CEMI)

隨著在電子產(chǎn)品中往往需要進(jìn)行EMC的檢測分析,傳導(dǎo)就是EMC的一種。為了更好地發(fā)現(xiàn)、避免以及解決傳導(dǎo)的問題。在PIPro中可以利用CEMI對電路進(jìn)行傳導(dǎo)的仿真分析。下圖所示為CE的仿真結(jié)果。

仿真后,還可以生成test bench,在ADS原理圖中做進(jìn)一步的電路分析,以找到解決問題的方法。

第五章 電源完整性激勵域測試之碼型發(fā)生器

引言

脈沖函數(shù)任意波形噪聲發(fā)生器在壓力測試應(yīng)用中的重要作用

情況分析

集成電路芯片通常安裝在印刷電路板(PCB)上,由電源分布網(wǎng)絡(luò)(PDN)供電。使用每個集成電路芯片時,都必須考慮到它對電源分布網(wǎng)絡(luò)的影響。大多數(shù)集成電路芯片只在改變狀態(tài)時消耗電流,這種不規(guī)律的用電給PDN帶來了很大失真,產(chǎn)生電源完整性的問題。

電源分布網(wǎng)絡(luò)出問題,會對其它電路產(chǎn)生干擾,增加噪聲,進(jìn)而導(dǎo)致信噪比降 低,影響集成電路芯片輸出端口處的信號完整性。在最壞的場景中,電源噪聲有可能對集成電路的工作產(chǎn)生負(fù)面影響。同樣,直流電源電平的波動也會干擾集成電路的正確工作。

為了限制這些不利因素的影響,硬件工程師設(shè)計了一系列保護(hù)電路。保護(hù)集成電路芯片的常用方法包括:使用去耦電容抑制電壓波動,加入電感器限制噪聲電平。可是所有補償方法在最大限度減少直流電源失真的同時,也都存在各自的限制。

例如使用去耦電容時,電容器中的材料缺陷會產(chǎn)生等效的串聯(lián)電阻。電容器和封裝會產(chǎn)生等效的串聯(lián)電感。這些寄生效應(yīng)會嚴(yán)重影響電容器的技術(shù)特性。電容器在高頻范圍內(nèi)的特性更像是電感或電阻器――有違于它在電路中的最初用途。

方案配置

在真實條件下測試元器件和電路是一個必不可少的環(huán)節(jié)。在這個過程中,工程師可以評估PCB 的設(shè)計和功耗。測試還可以使工程師深入了解被測對象,增強被測件的總體性能。

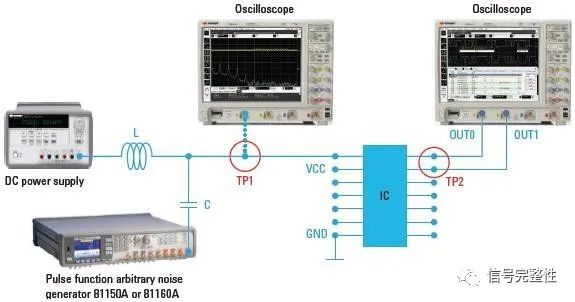

圖 5-1 顯示了在設(shè)計過程中模擬真實環(huán)境的有效方法。表5-1 中匯總了該方案的組成部分。在圖 5-1 所示的配置中,Keysight E36311A 直流電源用于模擬被測電路中的電壓源。Keysight 81160A 任意波形噪聲發(fā)生器用于模擬信號失真。電源和噪聲發(fā)生器的輸出通過電感和電容器所構(gòu)成的網(wǎng)絡(luò)合并。電感 L 可以防止信號的射頻分量進(jìn)入直流電源。電容器 C 可以避免信號發(fā)生器(81160A)直流負(fù)載效應(yīng)。這個網(wǎng)絡(luò)在技術(shù)資料中經(jīng)常被稱為偏置 T 形接頭,因為它的形狀為 T 形,并可以提供“直流偏置”。

圖 5-1. 模擬真實條件的測試裝置

| 是德科技解決方案 | |

| 直流電源 | E3631A 80W 三路輸出電源,6 V,5 A,以及 ±25 V,1A 或類似型號 |

| 發(fā)生器 | 81160A 或 81150A 脈沖函數(shù)任意波形噪聲發(fā)生器 |

| 示波器 | Infiniium S 或 9000 系列示波器 |

表5-1 (81150A的噪聲碼型重復(fù)速率為26天。)

實現(xiàn)深入分析

Keysight Infiniium S 或 9000 系列示波器的一個主要特性是它能夠校準(zhǔn)測試配置。換句話說,示波器能夠確認(rèn)向被測器件(DUT)的輸入端,是否施加了正確的直流電壓和失真。(參見圖5-1 中測試點(TP1)處的連接。)

在圖 5-1 中的測試點(TP2)上,使用同一臺 9000 系列示波器來分析集成電路芯片輸出信號(圖中畫了兩臺示波器,但你可以只用一臺示波器)。一旦 81160A 添加的失真變得太大而無法補償時,集成電路芯片將產(chǎn)生物理層錯誤或協(xié)議層錯誤。這兩類錯誤可以用示波器檢測和分 析。

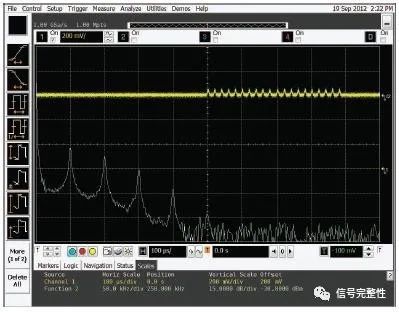

為了仿真真實條件下的功率失真,81160A 能夠生成上升時間/下降時間僅為 1 ns 的快速脈沖、隨機噪聲和各種任意波形。該發(fā)生器的另一個關(guān)鍵特性是能夠內(nèi)部合并不同類型的信號,因此可以同時疊加電源分布網(wǎng)絡(luò)中的高斯白噪聲和間歇性毛刺。這種通道疊加(Channel Add)功能不僅能夠靈活地生成復(fù)雜波形,而且避免了外部接線的麻煩。可選擇的噪聲發(fā)生器波峰因數(shù), 以及可以在20 1 天內(nèi)不重復(fù)噪聲碼型的功能,確保噪聲接近于隨機噪聲,而不是確定性噪聲(這些功能是其它同類儀器無法提供的)。圖 5-2 顯示了通道疊加和噪聲產(chǎn)生功能的示例。在此例中,81160A 在通道 1 生成高斯白噪聲,在通道 2 生成高斯脈沖,然后在內(nèi)部合并這兩種信號,再與電源的直流信號疊加,得到黃色軌跡。這是在時域中測得的結(jié)果。圖 5-2 所示的綠色軌跡是FFT頻譜分析結(jié)果 。利用這個功能,工程師可以深入分析被測器件的輸出性能。

圖 5-2. 81160A 任意波形噪聲發(fā)生器的通道疊加功能在時域(黃色)和 頻域(綠色)下生成的壓力信號示例。

結(jié)論

工程師在開發(fā)新的電子器件時會遇到許多挑戰(zhàn)。印刷電路板上的集成電路芯片密度日益提 高,因此評測直流電源性能以及電源分布網(wǎng)絡(luò)(PDN)對設(shè)計中其他元器件的影響也變得越來越重要。要正確評測設(shè)計,工程師需要使用能夠模擬真實條件的測試配置。當(dāng)工程師分析自己的設(shè)計時,測試方案各組件可以發(fā)揮重要作用,幫助他們最大限度減少失真并提高電源和信號的完整 性。

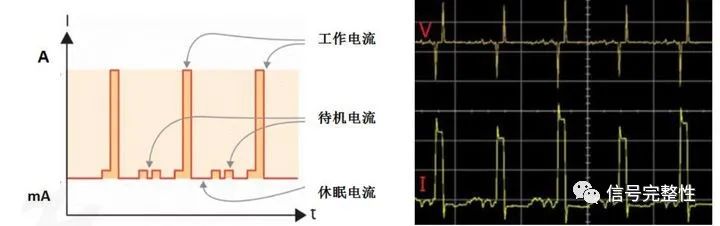

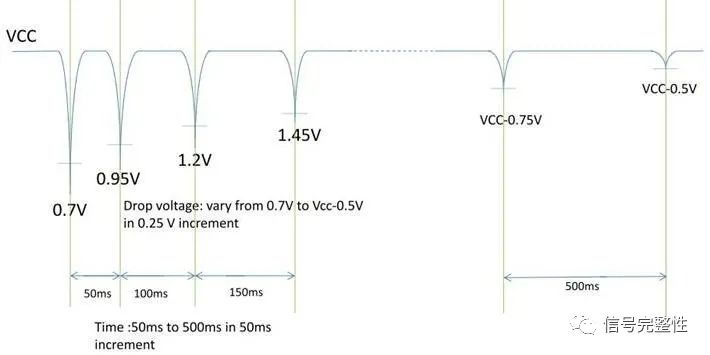

第六章 電源完整性測試之直流瞬態(tài)電壓及紋波噪聲模擬

如上圖所示, 智能手機或筆記本電腦在待機或休眠狀態(tài)時,通常電流較小(mA 級別),但處于工作狀態(tài)下,消耗電流會瞬間提升至安培(A)級別。這種高達(dá)上千倍的電流動態(tài)會通常會導(dǎo)致供電電壓出現(xiàn)明顯的毛刺(幅度高達(dá)數(shù)十甚至數(shù)百 mV),造成處理器、存儲芯片等 IC 無法正常工作。

如何對電源在上述動態(tài)電流的條件下輸出電壓瞬態(tài)特性,或者芯片設(shè)計時進(jìn)行 IC 對上述供電電壓瞬態(tài)的變化時的穩(wěn)定性進(jìn)行驗證?

動態(tài)負(fù)載模擬驗證電源的瞬態(tài)特性:

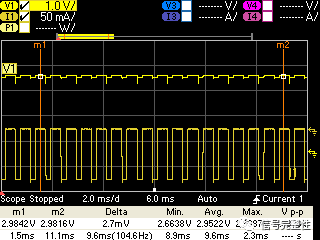

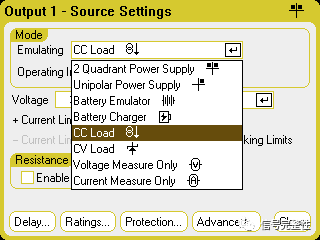

N6705C 直流電源分析儀的 N678x 系列 SMU 模塊,支持任意波形的負(fù)載模擬,可以模擬幅度從 uA 級至A 級的大動態(tài),us 至 ms 級的脈沖負(fù)載,并且支持高速,高精度的電壓及電流實時波形的測量,用于精確評估PMU, PMIC, LDO電源的瞬態(tài)性能。

模擬具有瞬態(tài)特性的供電電壓驗證 IC 穩(wěn)定性:

N6705C 直流電源分析儀

N676X 系列精密模組或 N678X 系列 SMU 模組,具有噪聲小,精度高,電壓調(diào)節(jié)速度快等特征,可用于任意瞬態(tài)供電電壓模擬,用于測試電路或 IC 在電壓瞬態(tài)時的可靠性。

典型配置

| 型號 | 描述 |

| N6705C |

直流電源分析儀主機,支持任意波形,示波器, 數(shù)據(jù)記錄儀,電壓、電流表等功能 |

| N6781A | 20V,±1A 或 6V,±3A SMU 模塊 |

| N6782A | 20V,±1A 或 6V,±3A SMU 模塊 |

| N6784A | ±20V,±1A 或±6V,±3A SMU 模塊 |

| N6785A | 20V,±4A 或 6V,±8A SMU 模塊 |

| N6786A | 20V,±4A 或 6V,±8A SMU 模塊 |

| N6761A | 50V,1.5A 精密模塊 |

| N6762A | 50V,3A 精密模塊 |

| 14585A | PC 端直流電源分析及控制軟件 |

最后一個部分,關(guān)于電源完整性測試系統(tǒng)和仿真軟件配置如下:

示波器部分

DSOS254A 2.5GHz 帶寬 10 比特示波器

N7020A 2GHz 1:1 電源完整性探頭(2 根)+N7023A點測套件

N2870A 35MHz 1:1 無源探頭 (2 根)

建議但不必須 : N2820A 極小信號測試差分電壓和電流探頭(500nA 或 3uV )

建議但不必須:N8833B-1FP 串?dāng)_分析軟件

網(wǎng)絡(luò)分析儀部分

E5061B(Opt 005,3L5) 網(wǎng)絡(luò)分析儀

1250-1250(x2),15442A

85033E

11667L

8120-1840(x4)

16201A(Opt 001),16195B

16092A,16192A(16192A/B/C/D,16197A 根據(jù)需要選擇),16047E

直流電源激勵部分

N7900 系列高級電源

N670C 直流電源分析儀 + N6762A DPS 模塊 + N6781A SMU 模塊

高速數(shù)字信號的電源完整性激勵部分

81160A 脈沖碼型任意波發(fā)生器

仿真部分

ADS W3625B,其中包含了ADS 核心環(huán)境、EMPro 核心環(huán)境、Layout、PIPro、SIPro、HSD電路仿真

審核編輯:湯梓紅

-

cpu

+關(guān)注

關(guān)注

68文章

10902瀏覽量

213000 -

仿真

+關(guān)注

關(guān)注

50文章

4124瀏覽量

133987 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1629瀏覽量

80821 -

電源完整性

+關(guān)注

關(guān)注

9文章

211瀏覽量

20779

原文標(biāo)題:最全電源完整性仿真和測試白皮書

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

信號完整性與電源完整性的仿真分析與設(shè)計

Voltus-Fi定制型電源完整性解決方案

誰更重要 || 信號完整性 vs 電源完整性

信號完整性與電源完整性的相關(guān)資料下載

信號完整性測試及典型應(yīng)用解決方案

ADS的信號完整性和電源完整性仿真應(yīng)用方案

電源完整性仿真和測試解決方案

電源完整性仿真和測試解決方案

評論