”=“阻塞賦值與”<=“非阻塞賦值是verilog語言中的兩種不同的賦值方式,下面將對兩種賦值方式進行比較。方便進行理解和使用。

阻塞賦值:=阻塞賦值為執行完一條賦值語句之后再執行下一條,可以理解為順序執行,而且賦值是立即執行;

非阻塞賦值:<=可以理解為并行執行,不考慮順序,在always塊語句執行完成之后才進行賦值。

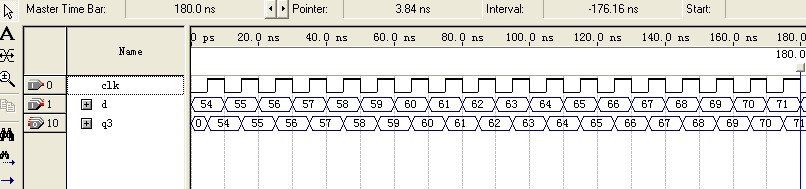

下面提供一段黑金官方的仿真程序,各位可以自行進行仿真對比:

(源程序)

module top (din , a , b , c , clk) ;

input din ;

input clk ;

output reg a, b, c;

always @ (posedge clk)

begin

a = din ;

b = a ;

c = b ;

end

endmodule

(激勵文件)

`timescale 1ns / 1ns

module top_tb () ;

reg din ;

reg clk ;

wire a, b, c ;

initial

begin

din = 0 ;

clk = 0 ;

forever

begin

#({$random}%100)

din = ~din ;

end

end

always #10 clk = ~clk ;

top

t0 (.din(din) , .a(a) , b(b) , .c(c) , .clk(clk)) ;

endmodule

同時也可以通過RTL圖的不同來發現兩者的區別:

注意 :一般情況下,在時序邏輯電路中使用非阻塞賦值,可以避免仿真時出現競爭冒險現象;在組合邏輯中使用阻塞賦值,執行賦值語句之后立即改變;在assign語句中必須使用阻塞賦值。

審核編輯:湯梓紅

-

RTL

+關注

關注

1文章

385瀏覽量

59950 -

時序邏輯電路

+關注

關注

2文章

94瀏覽量

16594 -

阻塞賦值

+關注

關注

0文章

9瀏覽量

9170 -

非阻塞賦值

+關注

關注

0文章

10瀏覽量

10019

發布評論請先 登錄

相關推薦

【連載視頻教程(六)】小梅哥FPGA設計思想與驗證方法視頻教程之例解阻塞賦值與非阻塞賦值

Verilog中阻塞賦值和非阻塞賦值的正確使用

verilog中阻塞賦值和非阻塞賦值

FPGA學習系列:5.阻塞賦值與非阻塞賦值

阻塞賦值與非阻塞賦值

阻塞賦值與非阻塞賦值

評論