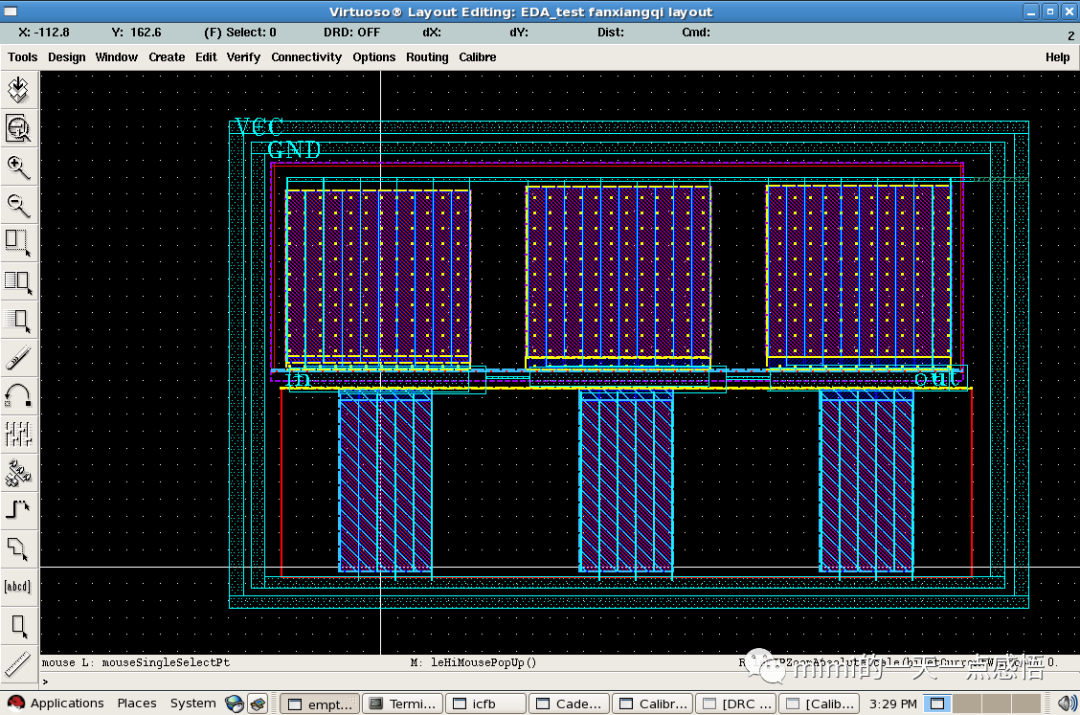

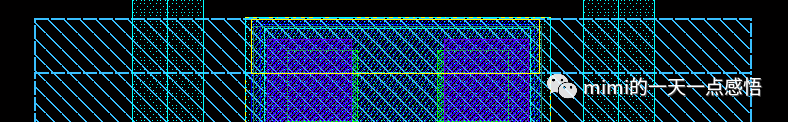

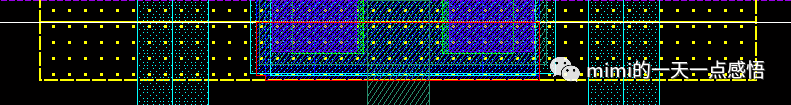

我改完之后的圖:

今天的內容包括:反相器鏈路版圖驗證步驟和模擬版圖驗證中常見的問題及修改。

反相器鏈路版圖驗證步驟

完成反向器鏈路的版圖設計后,還需要對版圖進行驗證和后仿真,主要是應用Mentor Calibre工具進行。

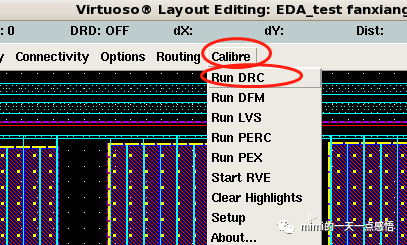

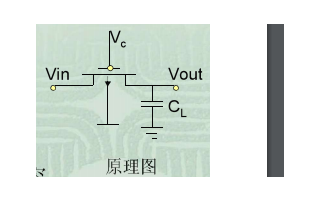

(1)在版圖視圖窗口中執行菜單命令

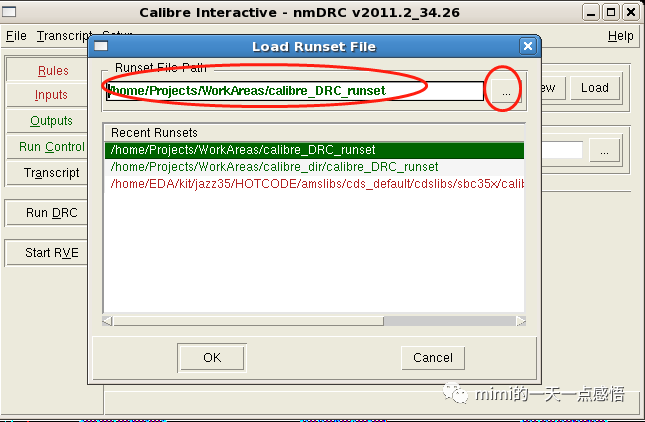

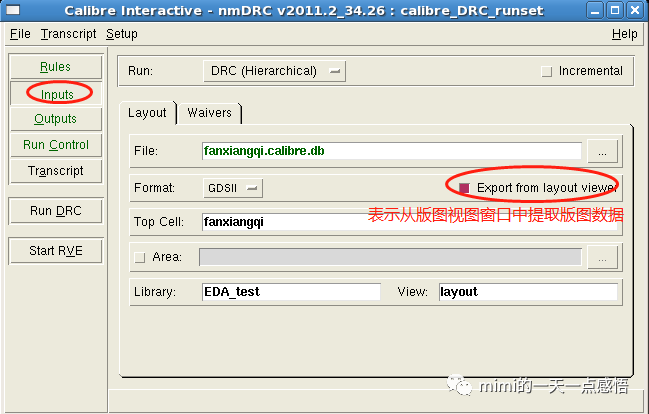

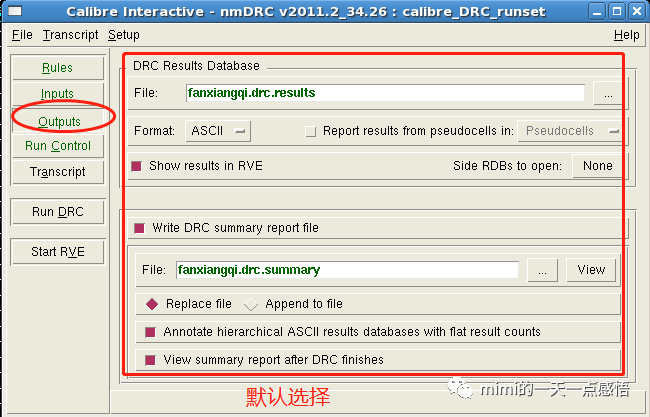

(2)選擇運行的文件和運行的目錄。

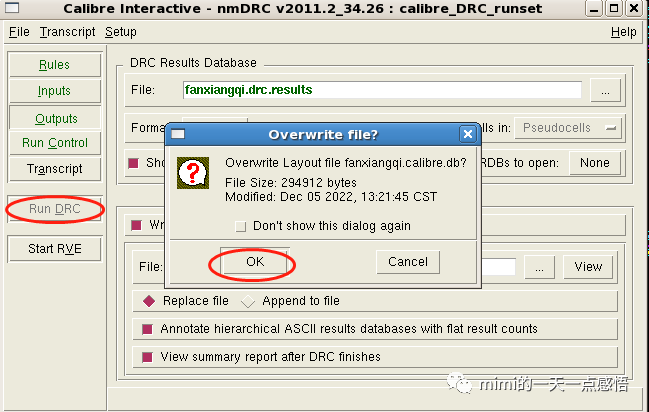

(3)單擊“run Control”按鈕,這時Calibre開始導出版圖文件并對其進行DRC檢查。

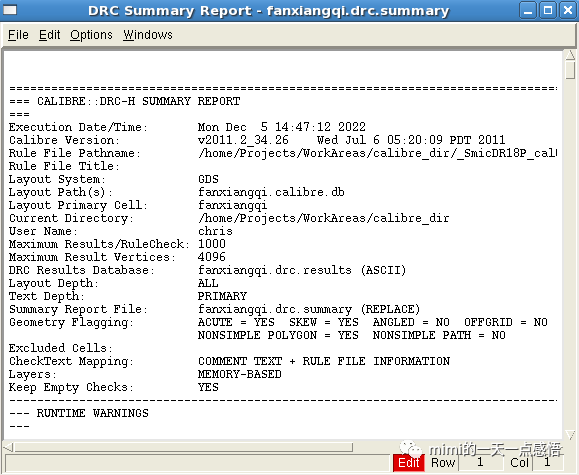

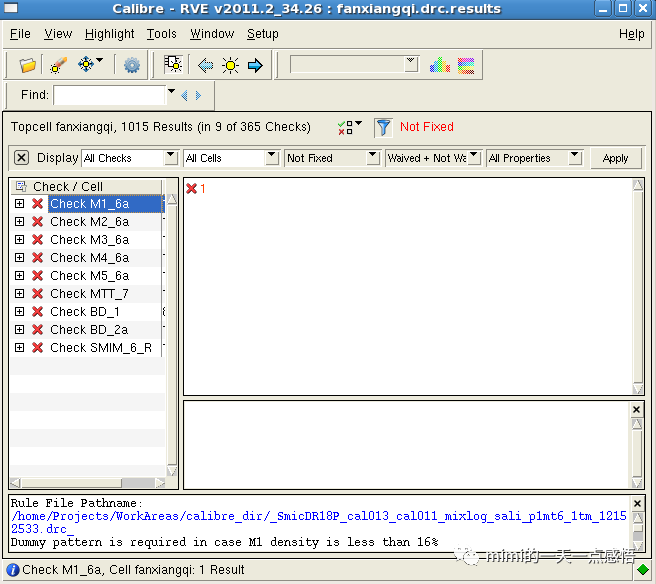

這個時候Calibre開始導出版圖文件并對其進行DRC檢查。Calibre DRC完成后,自動彈出輸出結果。包括一個圖形界面的錯誤文件查看器和一個文本格式文件。

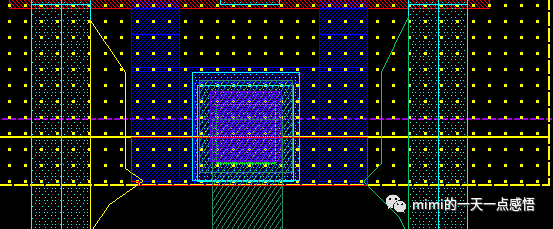

一般都是間距、密度和邊界的問題,間距的問題必須解決,密度和邊界可以暫時忽略。打開layout圖,雙擊錯誤可以定位到錯誤的位置,進行編輯修改就行。

直到錯誤修改完成。

常見的錯誤

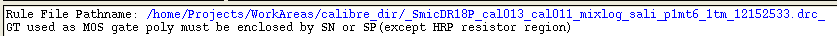

錯誤的地方一般都會標記:

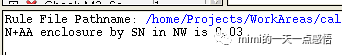

意思是這個是MOS晶體的Gate層,必須被SN或SP全部包圍

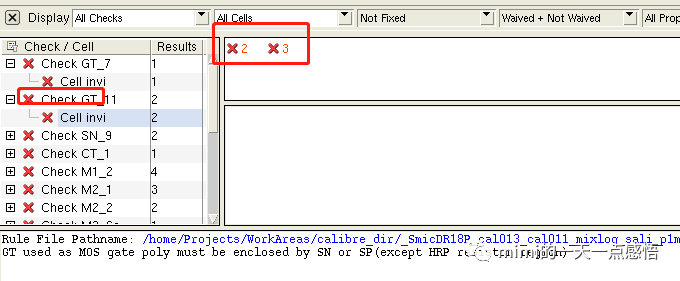

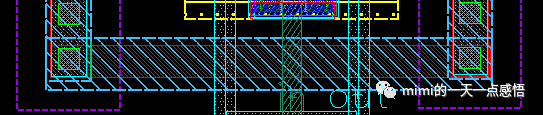

查看,有2個錯誤

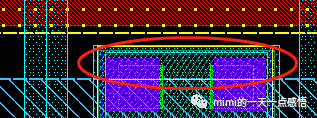

雙擊紅色的之后,再打開版圖的方框,就可以顯示出錯誤的位置。沒有被SP或者SN所包圍

選擇SN層,添加一個矩形,把它包圍進去,這樣這個錯誤就修復好了,同理另外一個也是

保存。

最小寬度是0.03um

拉寬

改為1個過孔

就這樣一個個的改

M2金屬的線寬要為0.2

間距要大于0.2

全部選擇之后再移動

密度,邊界的問題,現在都忽略,后期再處理。

-

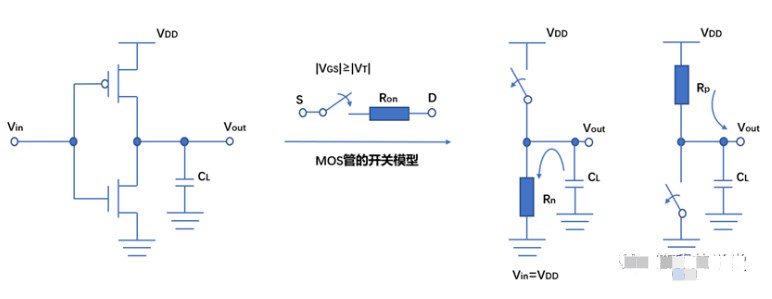

反相器

+關注

關注

6文章

311瀏覽量

43507 -

DRC

+關注

關注

2文章

150瀏覽量

36351 -

模擬器

+關注

關注

2文章

881瀏覽量

43421

發布評論請先 登錄

相關推薦

怎么用Cadence16.5設計集反相器??

集成電路設計學習筆記(二)基于IC617反相器設計之layout 精選資料分享

virtuoso中進行CMOS反相器和靜態寄存器的電路設計

反相器芯片有哪些

cmos反相器設計電路圖

MOS反相器和CMOS反相器的詳細資料說明

反相器鏈路版圖驗證步驟

反相器鏈路版圖驗證步驟

評論