本文介紹一個FPGA 開源項目:PCIE I/O控制卡。上一篇文章《FPGA優質開源項目– PCIE通信》開源了基于FPGA的PCIE通信Vivado工程,用于實現上位機通過PCIE接口訪問FPGA的DDR3以及RAM內存數據。PCIE I/O控制卡工程是在上一個工程的基礎上進行了部分模塊和參數的修改。

下面圍繞FPGA PCIE I/O控制卡通信方案以及Vivado BD工程的創建進行簡要介紹。

01軟硬件平臺

- 軟件平臺:Vivado 2017.4;

- 硬件平臺:XC7Z035FFG676-2;

02通信方案

系統通信方案如下圖所示。PC上位機端通過PCIE接口與FPGA連接,FPGA端通過XDMA模塊的AXI4總線實現對DDR3的讀寫,通過AXI4-Lite總線實現對多個GPIO外設的控制。其中AXI SmartConnect模塊可用于自動完成XDMA與多個GPIO模塊的通信仲裁,以及不同時鐘域、不用數據位寬自動轉換。

03創建Vivado BD工程

Vivado BD工程的創建可在上一個PCIE通信工程的基礎上完成。首先,刪除AXI BRAM Controller 以及RAM模塊:

然后,依次添加兩個AXI GPIO模塊。將axi_gpio_0配置為 All Outputs ,位寬根據實際情況選擇,這里配置為 4bits 。

將axi_gpio_1配置為 All Inputs ,位寬根據實際情況選擇,這里同樣配置為 4bits 。

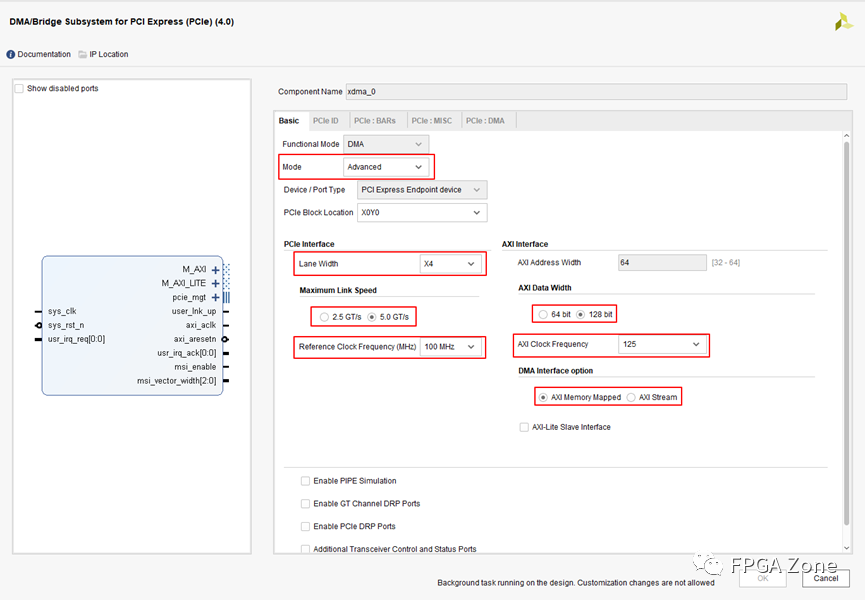

XDMA IP核參數配置:

- Mode:BASE;

- Lane Width:根據FPGA硬件型號選擇,通道越多,傳輸速度越快;

- Max Link Speed:5.0GT/s;

- Reference Clock:參考時鐘100MHZ;

- DMA Interface Option:選擇AXI4接口;

- AXI Data Width:AXI4總線位寬選擇128bits;

- AXI Clock:AXI4總線時鐘125MHZ;

- PCIE to AXI Translation:BAR地址到AXI地址偏移,這里設置為0x44a0_0000;

其它參數配置可參考上一篇文章中的介紹。

04Vivado BD工程結構

下圖為最終創建好的Vivado BD工程。同樣的,本工程雖然是基于Zynq平臺建立,但實際只用到了PL端資源。

地址配置如下圖所示:DDR3初始地址偏移配置為0,AXI_GPIO_0初始地址配置為0x44a3_0000,AXI_GPIO_1初始地址配置為0x44a4_0000,與XDMA中地址偏移保持一致即可。

05實現功能

該Vivado工程實現了基于FPGA的PCIE I/O控制卡功能。FPGA端把AXI_GPIO地址映射到BAR地址空間,上位機端通過PCIE總線讀取FPGA端GPIO1 I/O口輸入狀態信息,以及控制GPIO0 I/O口輸出信息。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605987 -

控制卡

+關注

關注

2文章

60瀏覽量

13049 -

PCIe

+關注

關注

15文章

1260瀏覽量

83186 -

上位機

+關注

關注

27文章

945瀏覽量

55003 -

Vivado

+關注

關注

19文章

815瀏覽量

66886

發布評論請先 登錄

相關推薦

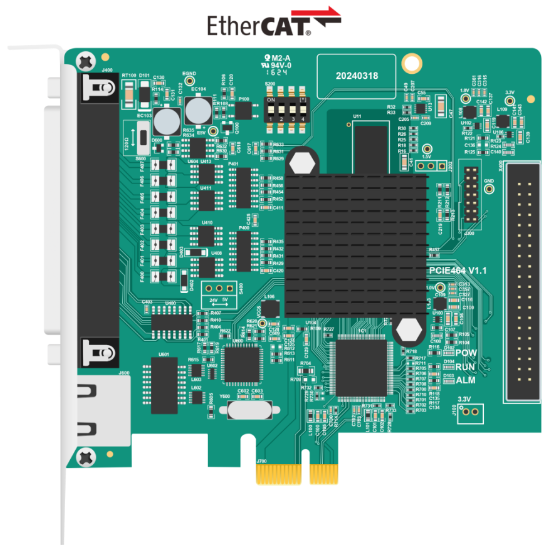

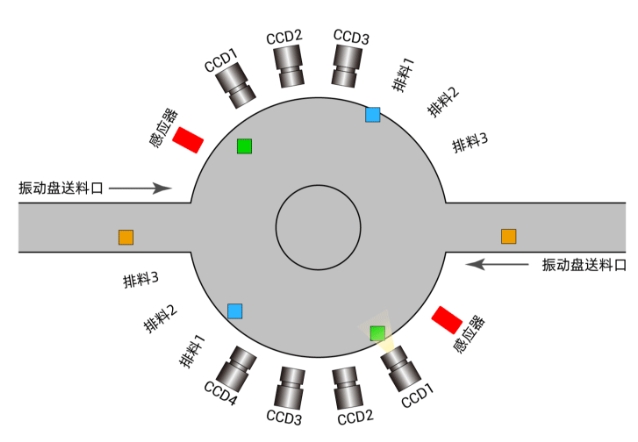

【正運動】高速高精,超高實時性的PCIe EtherCAT實時運動控制卡 | PCIE464

采用LabVIEW FPGA模塊和可重新配置I/O設備開發測量與控制應用

如何利用FPGA設計運動控制卡?

使用LabVIEW FPGA模塊和可重新配置I/O設備開發測

基于FMC標準的FPGA夾層卡I/O設計

基于FPGA I/O接口的五大優勢與FPGA深層分析

FPGA器件的I/O引腳布局的優化方案分析

PCIe中三種基本的I/O架構

基于FPGA的PCIE I/O控制卡通信方案

基于FPGA的PCIE I/O控制卡通信方案

評論