FPGA算法是指在FPGA(現(xiàn)場可編程門陣列)上實現(xiàn)的算法。FPGA是一種可重構(gòu)的硬件設(shè)備,可以通過配置和編程實現(xiàn)各種不同的功能和算法,而不需要進行硬件電路的修改。

FPGA算法可以包括各種不同的計算和處理任務(wù),例如數(shù)字信號處理(DSP)、圖像處理、機器學習、通信協(xié)議處理等。FPGA的特點使得它非常適合實現(xiàn)需要高度并行計算和低延遲的算法。

實現(xiàn)FPGA算法的過程通常涉及以下幾個方面:

1. 硬件描述語言(HDL)編寫:使用硬件描述語言(如VHDL或Verilog)來描述算法的硬件結(jié)構(gòu)和計算邏輯。

2. 綜合和優(yōu)化:使用綜合工具將HDL代碼轉(zhuǎn)換為FPGA的可編程邏輯塊和數(shù)字信號處理塊。通過優(yōu)化和資源利用率的考慮,提高算法的性能和效率。

3. 約束與布局:應用約束以滿足時序、時鐘頻率和信號完整性的要求,并使用布局工具進行物理布局以最小化信號傳輸?shù)穆窂健?/p>

4. 下載與調(diào)試:將設(shè)計下載到FPGA設(shè)備中,利用開發(fā)板支持工具進行功能驗證和性能調(diào)試。

FPGA算法的優(yōu)點在于它們可以提供高度的定制化和靈活性,使得算法可以根據(jù)實際需求進行優(yōu)化和調(diào)整。此外,F(xiàn)PGA還可以實現(xiàn)硬件加速,提供比傳統(tǒng)處理器更高的計算性能和吞吐量。因此,F(xiàn)PGA算法在許多領(lǐng)域中被廣泛應用,包括嵌入式系統(tǒng)、高性能計算和實時信號處理等。

怎么用FPGA做算法

使用FPGA(現(xiàn)場可編程門陣列)來實現(xiàn)算法是一種常見的方法,它可以提供高效的硬件加速和靈活的算法設(shè)計。下面是一般的步驟來用FPGA實現(xiàn)算法:

1. 算法設(shè)計與驗證:首先,你需要根據(jù)你的需求來設(shè)計算法。這包括確定輸入和輸出的數(shù)據(jù)格式、算法的處理步驟和計算流程等。你還可以使用軟件工具如MATLAB或Python等進行算法驗證,以確保其正確性和效果。

2. 硬件描述語言(HDL)編寫:使用硬件描述語言如VHDL或Verilog,將算法轉(zhuǎn)換成可在FPGA上實現(xiàn)的硬件描述。通過將算法進行邏輯門級的建模,你可以描述算法的功能和計算結(jié)構(gòu)。

3. 綜合和優(yōu)化:使用綜合工具,將HDL代碼轉(zhuǎn)換為對應 FPGA 的可編程邏輯塊(PL)和數(shù)字信號處理(DSP)塊。在綜合期間,你可以選擇各種優(yōu)化選項,以提高資源利用率和性能。

4. 約束與布局:在 FPGA 上實現(xiàn)算法時,你需要考慮電路的物理限制。為了確保正確的時序和信號完整性,你需要應用各種約束,如時鐘頻率、I/O 路由和時序調(diào)整等。布局工具可以幫助你對設(shè)計進行布局,以使信號傳輸?shù)穆窂阶疃獭?/p>

5. 時序分析與時序約束:在算法實現(xiàn)的過程中,你需要進行時序分析以驗證設(shè)計是否滿足時序要求。通過應用時序約束,你可以確保數(shù)據(jù)在正確的時間窗口內(nèi)被傳輸和處理。

6. 下載與調(diào)試:當你完成 FPGA 的編程和配置后,將設(shè)計下載到 FPGA 開發(fā)板中。使用相應的開發(fā)板支持工具,你可以進行功能和性能的調(diào)試和驗證。

如何在FPGA上實現(xiàn)最大公約數(shù)算法

如何在FPGA上實現(xiàn)最大公約數(shù)算法,簡單介紹在FPGA上實現(xiàn)算法的基本思想。希望通過本文的介紹,讓各位朋友管中窺豹,初步形成如何用FPGA實現(xiàn)算法的基本概念。

輾轉(zhuǎn)相除法是求解兩個數(shù)的最大公約數(shù)最常用的方法,例如,計算a=1071和b=462的最大公約數(shù)的過程如下:

用1071除以462得到余數(shù)為147: 1071 mod 462 = 147

用462除以147得到余數(shù)為21: 462 mod 147 = 21

用147除以21得到余數(shù)為0: 147 mod 21 = 0

此時余數(shù)為0,所以1071和462的最大公約數(shù)為21。

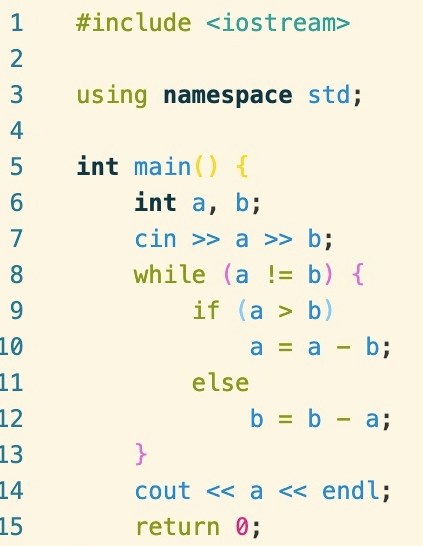

下圖是該過程的C++實現(xiàn),輸入a和b,當b不為0時,不斷進行上述過程直到b為0,此時a為最大公約數(shù)。各位同學有興趣可以自行仿真上述代碼并通過單步調(diào)試觀察中間過程。

輾轉(zhuǎn)相除法求最大公約數(shù)的實現(xiàn)

在驗證算法的正確性后,可以進入算法實現(xiàn)階段。在FPGA上實現(xiàn)該算法主要有以下兩個步驟,首先需要優(yōu)化算法,使算法更容易在硬件上實現(xiàn)。之后便是將算法模型轉(zhuǎn)化為RTL模型,并用硬件描述語言將模型描述出來。下面分別介紹這兩個步驟。

算法優(yōu)化

在上述過程中,存在使用除法求余數(shù)的步驟。用硬件實現(xiàn)除法開銷較大,一般情況下會考慮將除法替換為其它運算操作。由于除法和減法之間存在等價關(guān)系,除法取余數(shù)本質(zhì)上是不斷做減法直到被除數(shù)小于除數(shù)。在這里可以首先考慮將該使用減法實現(xiàn)求余操作,可以使用以下方式實現(xiàn)輾轉(zhuǎn)相除法:

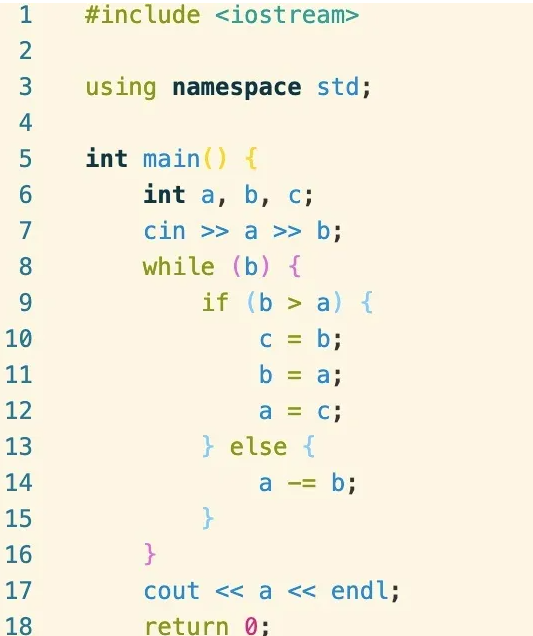

使用減法實現(xiàn)求余操作

當a大于b時不斷用a減去b,最后a的結(jié)果就是a mod b。當a小于b時則不斷用b減去a,最后a的結(jié)果就是a mod b。當a等于b時,此時無論是a mod b還是b mod a都為0,因此,此時a的值即為a與b的最大公約數(shù)。

修改后的算法用減法實現(xiàn)取模操作,降低了硬件實現(xiàn)的開銷。但是取模操作始終是用大的數(shù)去減小的數(shù)得到余數(shù),因此并不需要兩個減法器。如果規(guī)定a為a和b中的大數(shù),每次取模運算都都求a mod b的值,則只需要使用到一個減法器。但這需要一個判斷的步驟,在a小于b時交換a和b的值,以維護a始終大于b這一關(guān)系。按照這種思路可以寫出如下代碼:

用于最終實現(xiàn)的版本

在以上代碼中,當b大于a時交換a和b,確保a永遠是兩個數(shù)中較大的那個數(shù)。否則不斷用a減去b得到a mod b,直到b為0,此時a的值即為a和b的最大公約數(shù)。至此,我們將算法優(yōu)化為更易于硬件實現(xiàn)的版本:首先將取模使用減法實現(xiàn),再減少減法器的數(shù)量,得到了用于最終實現(xiàn)的版本。

簡要總結(jié)一下,優(yōu)化算法的目標有以下幾點:

1. 減少硬件開銷

2. 提高吞吐率,降低延遲

3. 降低系統(tǒng)功耗

而要實現(xiàn)這些目標主要可以考慮以下優(yōu)化方向:

1. 將復雜的計算模塊用簡單的替換,比如使用減法算余數(shù),但可能會帶來計算時間的增加

2. 通過量化等方法減少數(shù)據(jù)位寬

3. 提高系統(tǒng)的并行度,增加數(shù)據(jù)處理的并發(fā)性

4. 調(diào)整計算順序,優(yōu)化計算過程以更符合硬件結(jié)構(gòu)

在算法優(yōu)化完成以后,下一步便是設(shè)計合適的硬件結(jié)構(gòu)。

編輯:黃飛

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605998 -

圖像處理

+關(guān)注

關(guān)注

27文章

1300瀏覽量

56890 -

算法

+關(guān)注

關(guān)注

23文章

4630瀏覽量

93352 -

數(shù)字信號處理

+關(guān)注

關(guān)注

15文章

563瀏覽量

45999 -

機器學習

+關(guān)注

關(guān)注

66文章

8438瀏覽量

133082

發(fā)布評論請先 登錄

相關(guān)推薦

Qsys系統(tǒng)生成之后,沒有reset輸入引腳是怎么回事?

Python求最大公約數(shù)遇到問題

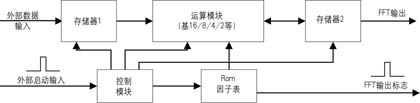

如何在FPGA上實現(xiàn)硬件上的FFT算法

DCT域數(shù)字水印算法的FPGA實現(xiàn)

用FPGA實現(xiàn)FFT算法

怎么用FPGA做算法 如何在FPGA上實現(xiàn)最大公約數(shù)算法

怎么用FPGA做算法 如何在FPGA上實現(xiàn)最大公約數(shù)算法

評論