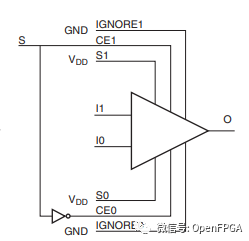

大部分開發(fā)者使用 BUFGCTRL 或 BUFGMUX進行時鐘切換,它們在時鐘切換上可以提供無毛刺輸出。然而,了解所涉及的原理是有好處的。

當然,無論我們在同步邏輯中使用哪種技術(shù),重要的是要確保在進行時鐘切換時輸出上沒有毛刺。任何故障都可能導致下游邏輯的錯誤行為。

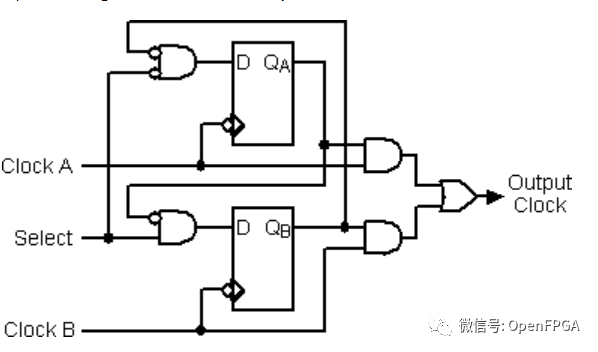

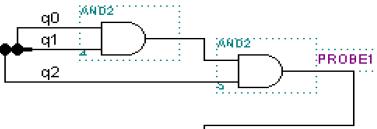

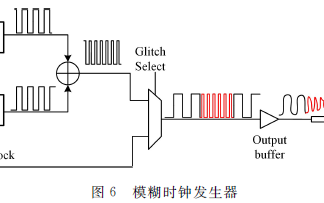

那么,讓我們看看如何僅使用邏輯門和寄存器產(chǎn)生無毛刺輸出的時鐘切換。Peter 大神介紹了如下電路。

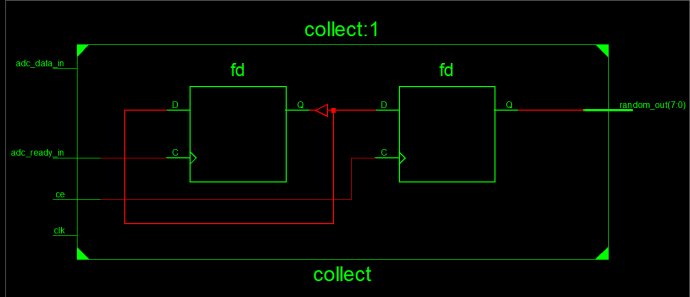

使用兩個寄存器來存儲選擇信號的狀態(tài)。這些狀態(tài)在時鐘的下降沿更新,并且取消選擇的寄存器將其時鐘保持在復位狀態(tài)。由于下降沿,時鐘處于低電平,并且輸出時鐘保持低電平。它將保持低電平,直到所選時鐘變低(以更新其控制寄存器)并變高。

在 Vivado 中實現(xiàn)這一點很簡單。只需幾行代碼即可創(chuàng)建時鐘切換。

libraryieee; useieee.std_logic_1164.all; entityclk_swisport( clk_a:instd_logic; clk_b:instd_logic; sel:instd_logic; clk_out:outstd_logic); endentity; architecturertlofclk_swis signalclk_a_reg:std_logic:='0'; signalclk_b_reg:std_logic:='0'; begin cntrl_a:process(clk_a) begin iffalling_edge(clk_a)then clk_a_reg<=?(not?sel)?and?(not?clk_b_reg); ????end?if; end?process; cntrl_b?:?process(clk_b) begin ????if?falling_edge(clk_b)?then? ????????clk_b_reg?<=?sel?and?(not?clk_a_reg); ????end?if; end?process; clk_out?<=?(clk_a_reg?and?clk_a)?or?(clk_b_reg?and?clk_b); end?architecture;

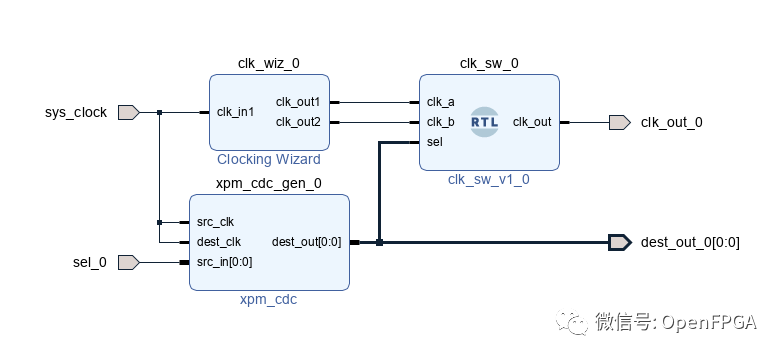

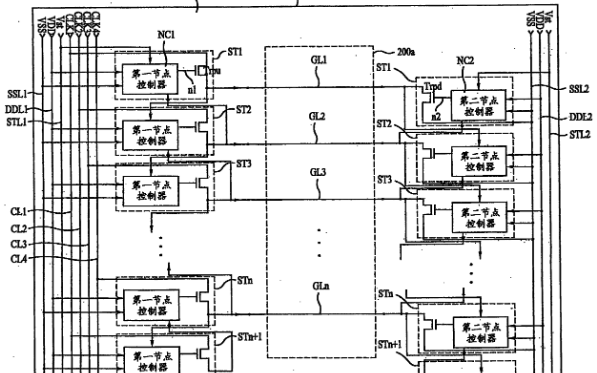

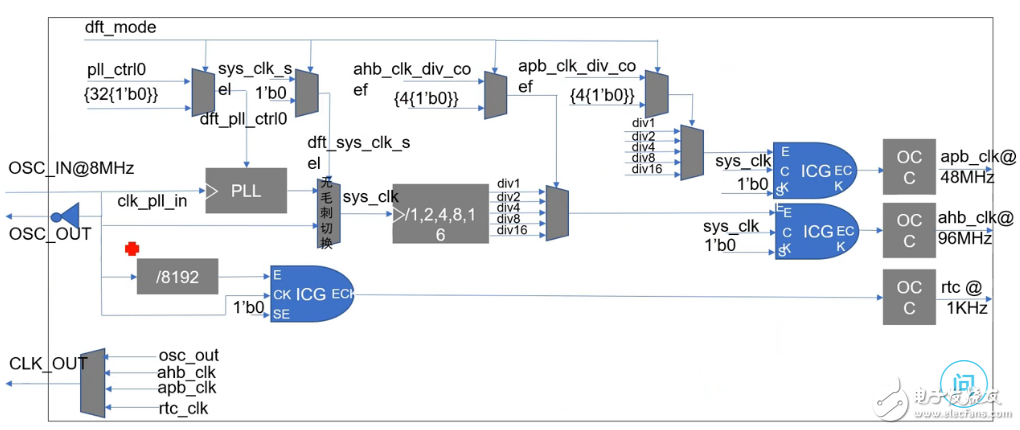

使用PLL將系統(tǒng)的時鐘 (100MHz) 劃分為兩個隨機且不相關(guān)的頻率。輸出時鐘引出到GPIO 引腳 。

使用 100 MHz 的 XPM 同步器宏來對其進行去抖。XPM 宏的輸出用于切換時鐘并路由至 GPIO 引腳 。

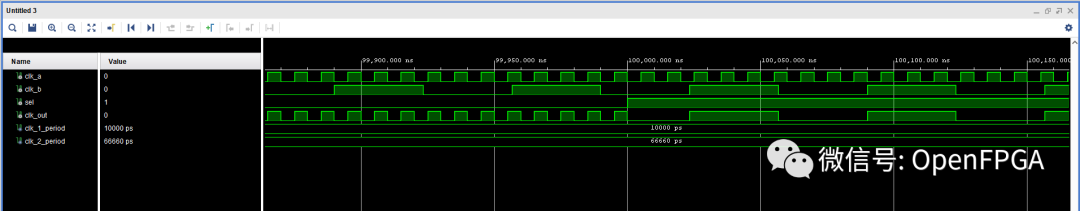

創(chuàng)建了一個簡單的測試平臺,可以在時序仿真中運行仿真,以確定實現(xiàn)中是否存在故障。

在上圖中可以看到時序仿真中沒有觀察到任何故障。

下一步是對電路板進行編程,并觀察在硬件中實現(xiàn)設(shè)計時設(shè)備中是否存在故障。

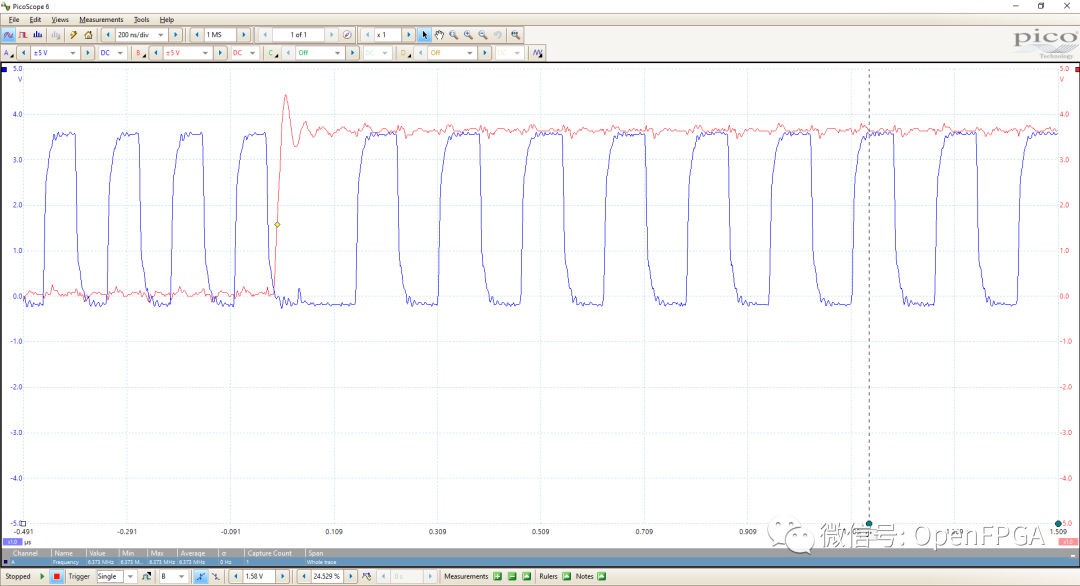

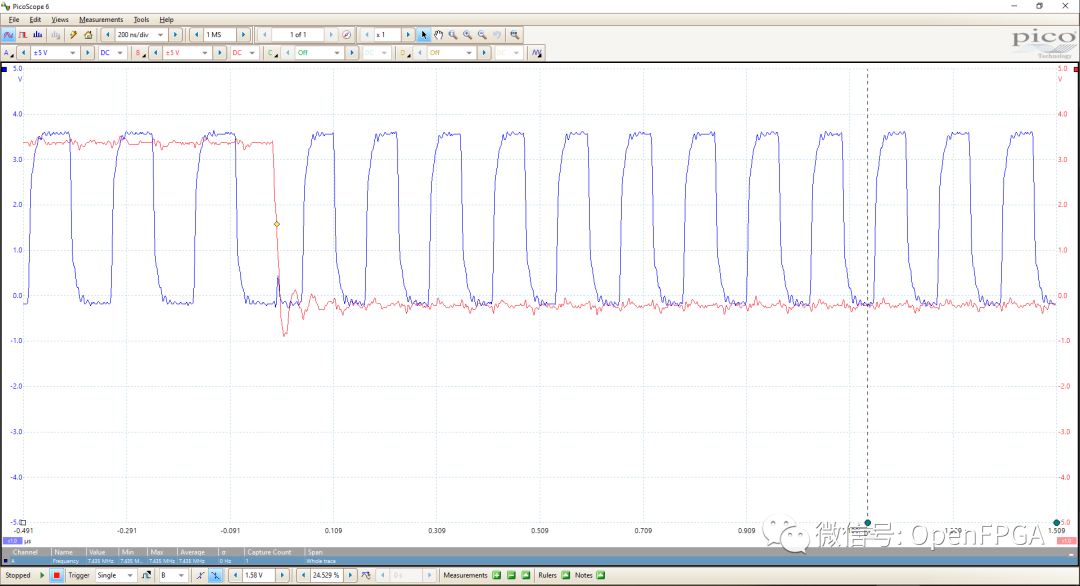

將頻率設(shè)置為 6.25 MHz 和 8.125 MHz。默認情況下,當選擇輸入為低電平時,將輸出 8.125 MHz 時鐘。將其切換至高電平將輸出切換至 6.25 MHz 時鐘。

當然,我們需要能夠確定切換發(fā)生時輸出上是否存在任何毛刺。因此,使用示波器監(jiān)測內(nèi)部同步選擇信號和時鐘輸出引腳。

從下面觀察輸出時鐘時可以看出,當時鐘的選擇線改變時,在輸出時鐘線上沒有觀察到毛刺。

盡管現(xiàn)代 FPGA 包含更先進、功能更強大的時鐘管理和時鐘電路,但一些低端FPGA上這些電路并不存在,我們就需要自己去創(chuàng)建始終切換電路。

審核編輯:劉清

-

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

121171 -

存儲器

+關(guān)注

關(guān)注

38文章

7528瀏覽量

164345 -

邏輯門

+關(guān)注

關(guān)注

1文章

142瀏覽量

24127 -

時鐘切換電路

+關(guān)注

關(guān)注

0文章

7瀏覽量

5790 -

PLL電路

+關(guān)注

關(guān)注

0文章

92瀏覽量

6475

原文標題:【數(shù)字實驗室】時鐘切換

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA實戰(zhàn)演練邏輯篇47:消除組合邏輯的毛刺

寄存器、鎖存器和觸發(fā)器的區(qū)別

psoc4-4200裝置是可能的CPU寄存器的輸出路由到邏輯門的輸入嗎?

簡談FPGA的競爭冒險和毛刺問題

FPGA | 競爭冒險和毛刺問題

消除組合邏輯產(chǎn)生的毛刺—PLD設(shè)計技巧

傳統(tǒng)的移位寄存器與光耦合器隔離移位寄存器有什么不同

MCU時鐘設(shè)計方案

時鐘毛刺注入攻擊的研究分析綜述

STM32寄存器點燈

直接修改寄存器來輸出內(nèi)部時鐘的方法

如何僅使用邏輯門和寄存器產(chǎn)生無毛刺輸出的時鐘切換?

如何僅使用邏輯門和寄存器產(chǎn)生無毛刺輸出的時鐘切換?

評論