首先拋出重點:使用Xilinx的平臺,最大的難點在于,要自己設計一個Flash讀寫控制器

具體如何設計一個合適的Flash讀寫控制器,鑒于Flash有諸多型號諸多接口,設計需求也不盡相同,所以這里不詳細論述了。文本討論一些與Xilinx FPGA相關的、大概率會遇到的問題。

這個Xapp的附件中,有一個用VHDL實現的Flash讀寫控制器設計可以參考。設計提供了源代碼。

關于這一篇,xapp1081,有幾點需要注意:

1.這一篇文檔的重點不是Flash讀寫控制器,提供的Flash讀寫控制器代碼在文檔中沒有詳細說明。

2.提供的Flash讀寫控制器只針對文檔中提到的特定用法。如果有更換FPGA、Flash等任何改變,均不保證能正常工作。

3.Xilinx默認對Xapp不提供任何官方支持。

自行設計Flash讀寫控制器的優勢是:

1.理論上可以通過修改設計來支持任何Flash,不用擔心兼容問題。

2.在時鐘、數據位寬、Flash操作命令等方面更靈活,可以充分挖掘FPGA和Flash的潛力。

假設已經有了Flash讀寫控制器的RTL設計,下一步應該是集成到FPGA設計中,其中主要的工作是連接FPGA I/O。

Pin安排

對于Xilinx的平臺的配置Pin,一般分為兩類,專用和復用。專用Pin是指只能用于配置模式,用戶無法(或者不方便)直接控制Pin的行為。復用Pin是指加載完成之后,這個Pin會變為User I/O,即和普通的User I/O一樣,可以由加載后的FPGA設計來控制Pin的行為。

控制Flash的配置Pin,基本都是復用類型Pin。在配置完成之后,都可以作為用戶可控的User I/O。所以可以設計一個Flash讀寫控制器,連接到這些Pin上。這樣FPGA在加載之前和加載的過程中,這些Pin工作在配置模式,從Flash中讀取配置數據;在加載完成之后,這些Pin變為User I/O模式,由讀寫控制器設計控制進行讀寫操作。

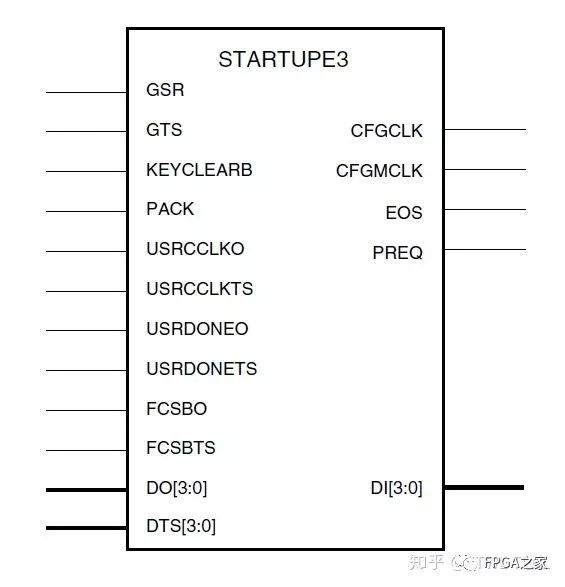

需要注意的是配置時鐘的處理。部分FPGA的CCLK是復用模式,加載完成之后可以作為User I/O。內部通過ODDR輸出時鐘即可提供Flash需要的時鐘。但是另外一部分FPGA的CCLK是專用Pin,用戶無法直接控制。這個時候可以查查是否有STARTUP這個模塊,往這個模塊的 USRCCLKO Port上送某個時鐘,就等于CCLK Pin上輸出這個時鐘。

假設現在Flash讀寫控制器已經集成到FPGA中了,數據的握手傳輸也完成了。那么下一步,就是,把什么數據往Flash中寫入了。

這個問題Xilinx的處理就方便多了。最簡單的方案,是寫入bin文件。不過即使是bin文件,也可能會犯錯。下面分析一下Xilinx的配置文件。

Xilinx常用的配置文件格式有三個(大部分情況下知道這三個就足夠了):bit/bin/mcs

直接寫入Flash的數據,對應的是bin文件。bin文件和bit文件都是二進制格式,bin文件直接對應Flash中的二進制數據。

下面用A7 100T為例子,生成一個bit文件作為基準。分析一下三種文件。

默認的情況下沒有任何約束,生成的bit文件作為基準,取名為original.bit。

在Vivado工程生成bit的同時,可以同時生成一個bin文件,取名original.bin。

另外,當獲取bit文件之后,可以使用write_cfgmem命令來生成bin文件和MCS文件。這種方法生成的bin文件,在默認情況下,取名g.bin,可以發現g.bin和original.bin兩個文件不太一樣。不過如果在使用write_cfgmem命令時添加參數 -interface SPIx1,生成文件spix1.bin,會發現spix1.bin和original.bin兩個文件幾乎一樣。

這個原因就是,write_cfgmem這個命令生成的文件是給Flash使用的。所以生成的文件內容會隨著Flash配置的改變而改變。

默認情況下,生成的bit文件original.bit是原始文件,伴隨生成的bin文件original.bin是直接轉為bin文件,不包含針對Flash的配置。

而write_cfgmem生成的bin文件,默認情況下認為Flash接口格式為SMAPX8(可以參考同時生成的.prm文件),所以生成的bin文件g.bin做了相關處理(一般是位序和大小端的轉換)。而SPI模式下,不需要額外的轉換,所以生成的bin文件spix1.bin和original.bin幾乎一樣。

類似,如果選擇BPIx8模式生成BPIx8.bin,可以發現和SMAPX8模式下的g.bin文件幾乎一樣。

所以可以明確,生成bit文件時生成的bin文件并不含有配置的相關信息。如果需要使用bin文件,那么用write_cfgmem,并同時提供相關配置接口信息,是更好的方案。上文提到的使用bin文件時可能會犯錯,就在于此。

至于MCS文件,由于是文本格式,所以直接讀取文件的數據是無法直接寫入Flash的,需要進行一定程度的轉換。如果僅僅是遠程更新中燒錄Flash的操作,那么可能用不到這個MCS文件。

注:三種文件雖然是在Vivado平臺下進行討論。由于配置文件的內容,應該與工具無關而和器件相關,所以ISE環境下的原理是一樣的,只是生成各個文件的操作步驟有不同而已。ISE工程生成bit文件后,使用Impact工具進行文件的轉換。

另外,寫入Flash時需要注意:

1.Flash需要先擦除再寫入。

2.寫入可能遇到大小端的問題,比較簡單的方法就是先試一下,如果不行,數據大小端改換一下再進行嘗試。

3.對于7系列及以后的芯片,基本上都是從0地址開始寫入Flash即可。Spartan-6可能其實位置不是0地址,需要查看文檔確認一下。

到此,Xilinx平臺下遠程更新的Flash讀寫控制方案已經基本介紹完了。更多配置的細節,可以參考相關FGPA的配置文檔,例如7系列是UG470。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605996 -

控制器

+關注

關注

112文章

16445瀏覽量

179446 -

FlaSh

+關注

關注

10文章

1642瀏覽量

148665 -

Xilinx

+關注

關注

71文章

2171瀏覽量

122129 -

RTL

+關注

關注

1文章

385瀏覽量

59948

原文標題:Xilinx平臺遠程更新中FPGA讀寫Flash設計的討論

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于FPGA的SPI Flash控制器的設計方案

基于VHDL的微型打印機控制器設計

基于PicoBlaze的Nand Flash控制器的實現

基于VHDL的DRAM控制器設計

Flash讀寫控制方案 Altera似乎“沒有”開放配置Flash的Pin的控制

基于VHDL語言和可編程邏輯器件實現Petri網邏輯控制器的設計

使用VHDL實現Flash讀寫控制器設計

使用VHDL實現Flash讀寫控制器設計

評論