在 SPI 中,主機可以選擇時鐘極性和時鐘相位。在空閑狀態(tài)期間,CPOL 為設置時鐘信號的極性。空閑狀態(tài)是指傳輸開始時 CS

為高電平且在向低電平轉(zhuǎn)變的期間,以及傳輸結(jié)束時 CS 為低電平且在向高電平轉(zhuǎn)變的期間。CPHA 為選擇時鐘相位。

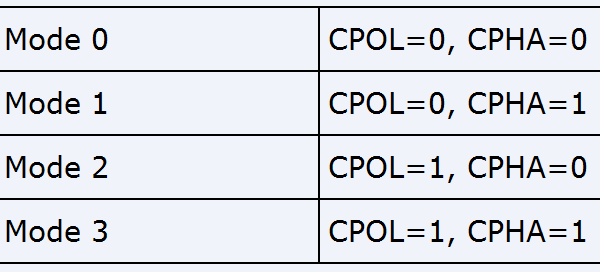

根據(jù)CPHA位的狀態(tài),使用時鐘上升沿或下降沿來采樣和/或移位數(shù)據(jù)。主機必須根據(jù)從機的要求選擇時鐘極性和時鐘相位。根據(jù) CPOL 和 CPHA

位的選擇,有四種SPI 模式可用。表1顯示了這 4 種 SPI 模式。

表1.通過CPOL和CPHA選擇SPI模式

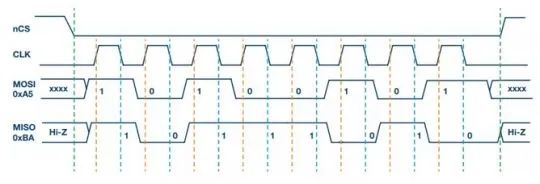

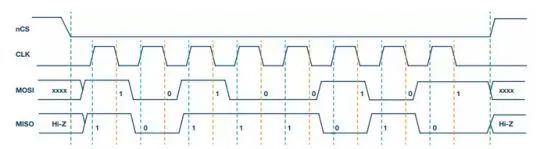

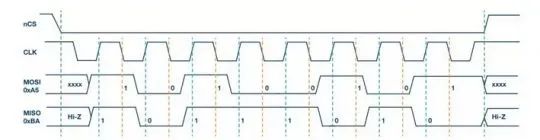

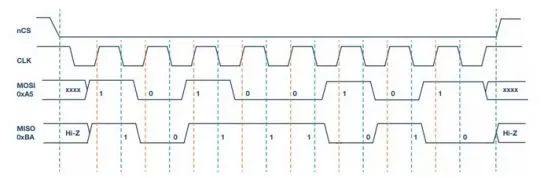

圖2至圖5顯示了四種SPI模式下的通信示例。在這些示例中,數(shù)據(jù)顯示在MOSI和MISO線上。傳輸?shù)拈_始和結(jié)束用綠色虛線表示,采樣邊沿用橙色虛線表示,移位邊沿用藍色虛線表示。請注意,這些圖形僅供參考。要成功進行SPI通信,用戶須參閱產(chǎn)品數(shù)據(jù)手冊并確保滿足器件的時序規(guī)格。

圖2給出了SPI模式0的時序圖。在此模式下,時鐘極性為0,表示時鐘信號的空閑狀態(tài)為低電平。此模式下的時鐘相位為0,表示數(shù)據(jù)在上升沿采樣(由橙色虛線顯示),并且數(shù)據(jù)在時鐘信號的下降沿移出(由藍色虛線顯示)。

圖2. SPI模式0,CPOL = 0,CPHA = 0:CLK空閑狀態(tài) = 低電平,數(shù)據(jù)在上升沿采樣,并在下降沿移出

圖3給出了SPI模式1的時序圖。在此模式下,時鐘極性為0,表示時鐘信號的空閑狀態(tài)為低電平。此模式下的時鐘相位為1,表示數(shù)據(jù)在下降沿采樣(由橙色虛線顯示),并且數(shù)據(jù)在時鐘信號的上升沿移出(由藍色虛線顯示)。

圖3. SPI模式1,CPOL = 0,CPHA = 1:CLK空閑狀態(tài) = 低電平,數(shù)據(jù)在下降沿采樣,并在上升沿移出

圖4. SPI模式2,CPOL = 1,CPHA = 1:CLK空閑狀態(tài) = 高電平,數(shù)據(jù)在下降沿采樣,并在上升沿移出

圖4給出了SPI模式2的時序圖。在此模式下,時鐘極性為1,表示時鐘信號的空閑狀態(tài)為高電平。此模式下的時鐘相位為1,表示數(shù)據(jù)在下降沿采樣(由橙色虛線顯示),并且數(shù)據(jù)在時鐘信號的上升沿移出(由藍色虛線顯示)。

圖5. SPI模式3,CPOL = 1,CPHA = 0:CLK空閑狀態(tài) = 高電平,數(shù)據(jù)在上升沿采樣,并在下降沿移出

圖5給出了SPI模式3的時序圖。在此模式下,時鐘極性為1,表示時鐘信號的空閑狀態(tài)為高電平。此模式下的時鐘相位為0,表示數(shù)據(jù)在上升沿采樣(由橙色虛線顯示),并且數(shù)據(jù)在時鐘信號的下降沿移出(由藍色虛線顯示)。

-

通信

+關注

關注

18文章

6071瀏覽量

136426 -

SPI

+關注

關注

17文章

1722瀏覽量

92129

發(fā)布評論請先 登錄

相關推薦

時鐘相位噪聲測量中雜散的討論及應用

SPI通信的四種方式 FPGA的SPI從機實現(xiàn)方案

SPI中的極性CPOL和相位CPHA介紹

淺談SPI總線

時鐘相位噪聲中如何生成和使用雜散

HbirdV2-SoC中如何配置QSPI1和QSPI2的時鐘極性CPOL和時鐘相位CPHA?

AD7606 SPI通信的時鐘極性和時鐘相位要求是什么?

根據(jù)時鐘極性和時鐘相位的不同,SPI有四個工作模式

如何生成和使用雜散進行測試:時鐘相位噪聲探討資料下載

為什么雜散會帶來額外抖動?時鐘相位噪聲測量解析資料下載

SPI實時時鐘與微控制器的接口

SPI通信協(xié)議介紹

SPI時鐘極性和時鐘相位

SPI時鐘極性和時鐘相位

評論