為了減少在高速信號(hào)傳輸過程中的反射現(xiàn)象,必須在信號(hào)源、接收端以及傳輸線上保持阻抗的匹配。單端信號(hào)線的具體阻抗取決于它的線寬尺寸以及與參考平面之間的相對(duì)位置。特定阻抗要求的差分對(duì)間的線寬/線距則取決于選擇的PCB疊層結(jié)構(gòu)。

由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結(jié)構(gòu)必須能實(shí)現(xiàn)板上的所有阻抗需求,包括內(nèi)層和外層、單端和差分線等。

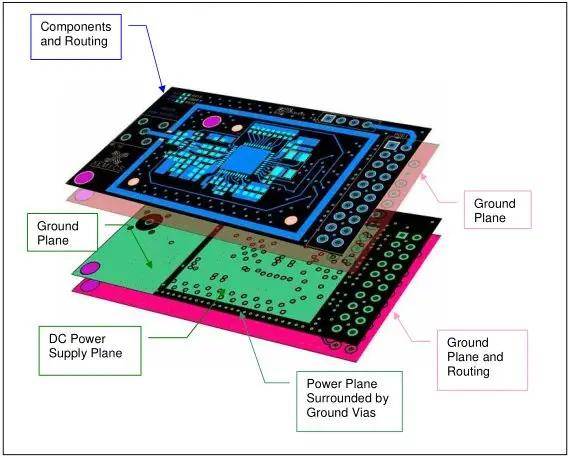

PCB疊層設(shè)計(jì)

“

層的定義設(shè)計(jì)原則

1、主芯片相臨層為地平面,提供器件面布線參考平面;

2、所有信號(hào)層盡可能與地平面相鄰;

3、盡量避免兩信號(hào)層直接相鄰;

4、主電源盡可能與其對(duì)應(yīng)地相鄰;

5、原則上應(yīng)該采用對(duì)稱結(jié)構(gòu)設(shè)計(jì),對(duì)稱的含義包括:介質(zhì)層厚度及種類、銅箔厚度、圖形分布類型(大銅箔層、線路層)的對(duì)稱。

“

PCB的層定義推薦方案

具體的PCB層設(shè)置時(shí),要對(duì)以上原則進(jìn)行靈活掌握,根據(jù)實(shí)際的需求,確定層的排布,切忌生搬硬套。以下給出常見的層排布推薦方案,供參考。在層設(shè)置時(shí),若有相鄰布線層,可通過增大相鄰布線層的間距,來(lái)降低層間串?dāng)_。對(duì)于跨分割的情況,確保關(guān)鍵信號(hào)必須有相對(duì)完整的參考地平面或提供必要的橋接措施。

本文以RK3588方案的PCB設(shè)計(jì)為例,其10層1階,10層2階,8層通孔等PCB疊層結(jié)構(gòu)的相關(guān)介紹,給客戶在疊層結(jié)構(gòu)的選擇和評(píng)估上提供幫助。如果選擇其他類型的疊層結(jié)構(gòu),請(qǐng)根據(jù)PCB廠商給出的規(guī)格,重新計(jì)算阻抗。

本文使用華秋DFM軟件的阻抗計(jì)算功能,為大家展開相關(guān)疊層和阻抗設(shè)計(jì)的案例講解。這是一款國(guó)內(nèi)免費(fèi)的PCB可制造性和PCBA裝配分析軟件,幫助設(shè)計(jì)工程師在生產(chǎn)前檢查出可制造性問題,且能夠滿足工程師需要的多種使用場(chǎng)景。

https://dfm.elecfans.com/uploads/software/promoter/hqdfm_DFMGZH.zip

8層通孔板1.6mm厚度疊層設(shè)計(jì)

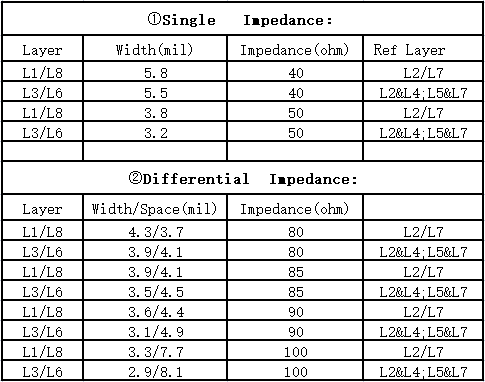

在8層通孔板疊層設(shè)計(jì)中,頂層信號(hào)L1的參考平面為L(zhǎng)2,底層信號(hào)L8的參考平面為L(zhǎng)7。建議層疊為TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基銅厚度建議全部采用 1oZ,厚度為1.6mm,其疊層設(shè)計(jì)如下圖所示。

8層通孔板1.6mm厚度阻抗設(shè)計(jì)

“

外層單端50歐姆阻抗設(shè)計(jì)

使用華秋DFM工具,選擇外層單端阻抗模型,輸入對(duì)應(yīng)參數(shù),計(jì)算出對(duì)應(yīng)線寬為3.8mil,L1與L8層是對(duì)稱設(shè)計(jì),故L1層與L8層50歐姆單端走線為3.8mil,如下圖所示。

“

外層差分100歐姆阻抗設(shè)計(jì)

使用華秋DFM工具,選擇外層單端阻抗模型,輸入對(duì)應(yīng)參數(shù),計(jì)算出對(duì)應(yīng)線寬/間距為3.3/7.7mil,L1與L8層是對(duì)稱設(shè)計(jì),故L1層與L8層100歐姆差分走線為3.3/7.7mil,如下圖所示。

“

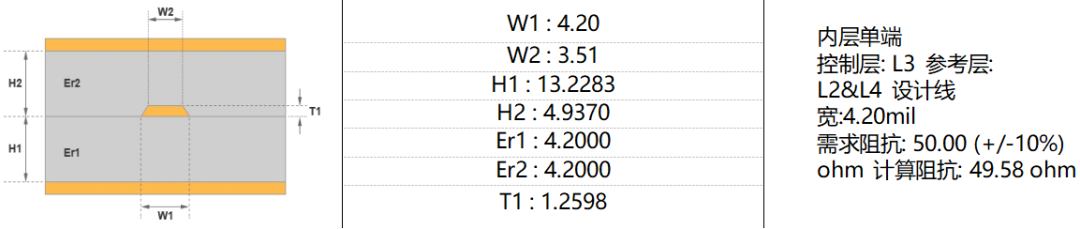

內(nèi)層單端50歐姆阻抗設(shè)計(jì)

使用華秋DFM工具,選擇外層單端阻抗模型,輸入對(duì)應(yīng)參數(shù),計(jì)算出對(duì)應(yīng)線寬為4.2mil,L3與L6層是對(duì)稱設(shè)計(jì),故L3層與L6層50歐姆單端走線為4.2mil,如下圖所示。

“

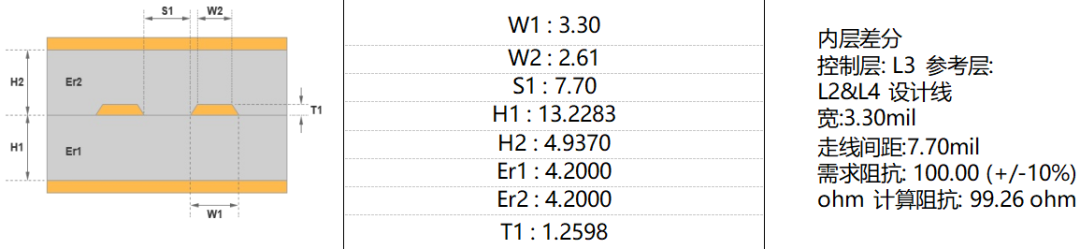

內(nèi)層差分100歐姆阻抗設(shè)計(jì)

使用華秋DFM工具,選擇外層單端阻抗模型,輸入對(duì)應(yīng)參數(shù),計(jì)算出對(duì)應(yīng)線寬/間距為3.3/7.7mil,L3與L6層是對(duì)稱設(shè)計(jì),故L3層與L6層100歐姆差分走線為3.3/7.7mil,如下圖所示。

“

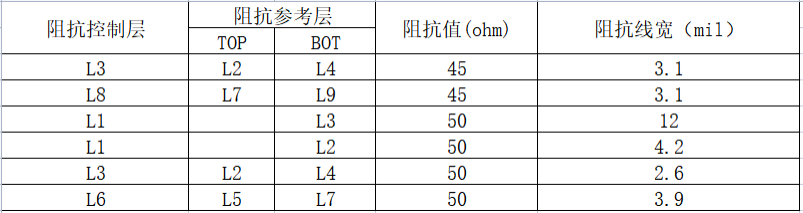

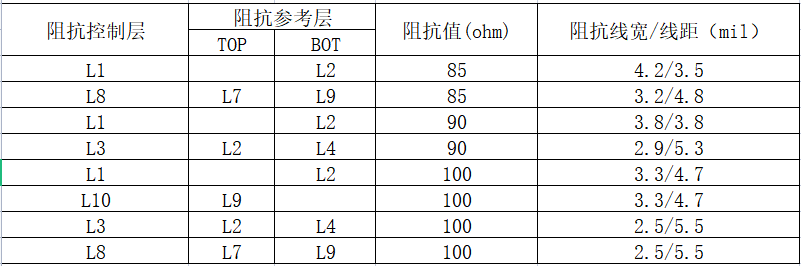

總體阻抗走線線寬

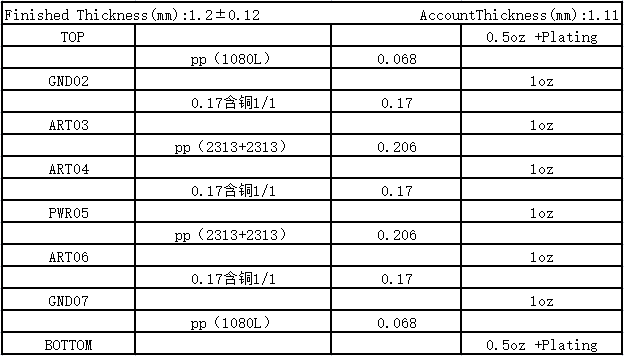

8層通孔板1.2mm厚度疊層設(shè)計(jì)

在8層通孔板疊層設(shè)計(jì)中,頂層信號(hào)L1的參考平面為L(zhǎng)2,底層信號(hào)L8的參考平面為L(zhǎng)7。建議層疊為TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基銅厚度建議全部采用 1oZ,厚度為1.2mm,詳細(xì)的疊層設(shè)計(jì)如下表所示。

8層通孔板1.2mm厚度阻抗設(shè)計(jì)

按照疊層設(shè)計(jì)參數(shù),使用華秋DFM軟件進(jìn)行阻抗計(jì)算,計(jì)算方法與上述8層1.6MM通孔一致,不一一截圖,計(jì)算出的阻抗線寬線距如下表所示。

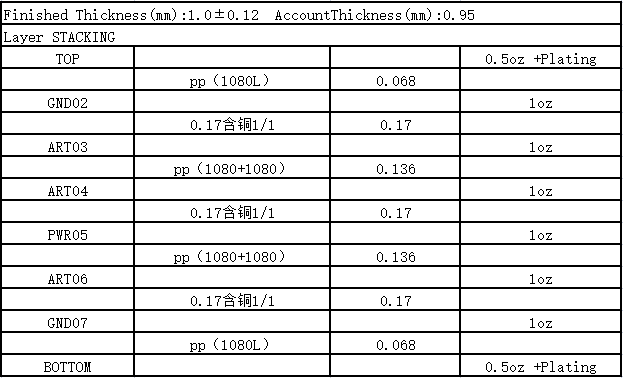

8層通孔板1.0mm厚度疊層設(shè)計(jì)

在8層通孔板疊層設(shè)計(jì)中,頂層信號(hào)L1的參考平面為L(zhǎng)2,底層信號(hào)L8的參考平面為L(zhǎng)7。建議層疊為TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基銅厚度建議全部采用 1oZ,厚度為1.0mm,詳細(xì)的疊層設(shè)計(jì)如下表所示。

8層通孔板1.0mm厚度阻抗設(shè)計(jì)

按照疊層設(shè)計(jì)參數(shù),使用華秋DFM軟件進(jìn)行阻抗計(jì)算,計(jì)算方法與上述8層1.6MM通孔一致,不一一截圖,計(jì)算出的阻抗線寬線距如下表所示。

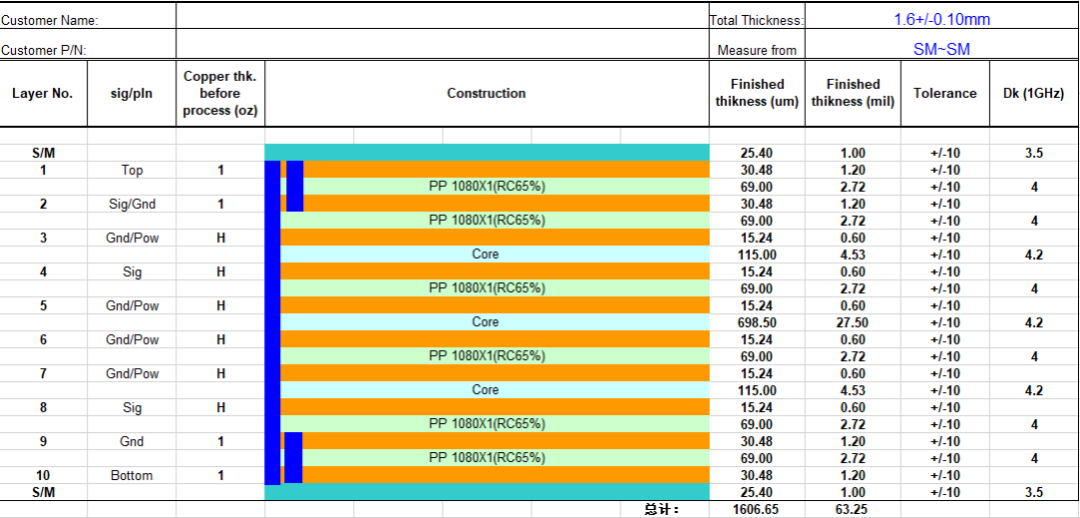

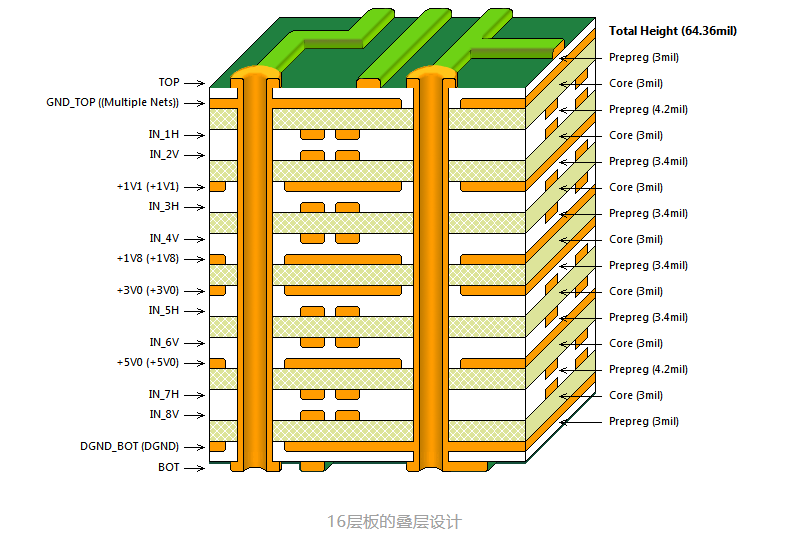

10層1階HDI板1.6mm厚度疊層設(shè)計(jì)

在10層1階板疊層設(shè)計(jì)中,頂層信號(hào)L1的參考平面為L(zhǎng)2,底層信號(hào)L10的參考平面為L(zhǎng)9。建議層疊為TOP-Signal/Gnd-Gnd/Power-Signal-Gnd/Power-Gnd/Power-Gnd/Power-Signal-Gnd-Bottom,其中L1,L2,L9,L10,建議采用1oZ,其它內(nèi)層采用HoZ。如下圖所示為1.6mm板厚的參考疊層。

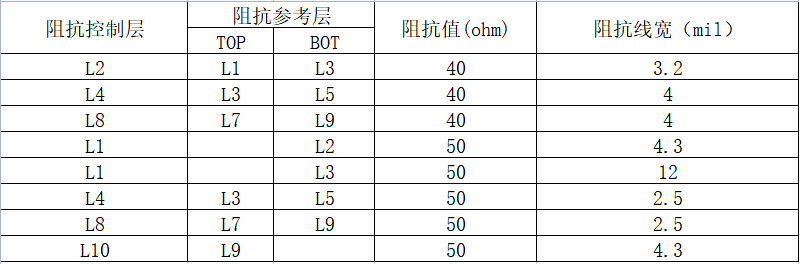

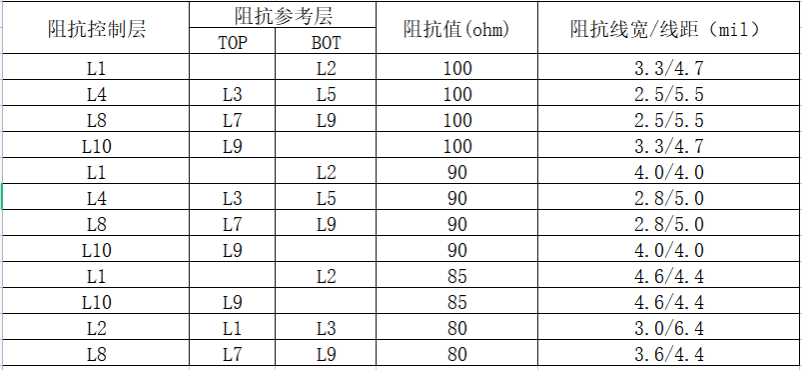

10層1階HDI板1.6mm厚度阻抗設(shè)計(jì)

按照疊層設(shè)計(jì)參數(shù),使用華秋dfm軟件進(jìn)行阻抗計(jì)算,計(jì)算方法與上述8層通孔一致,不一一截圖,計(jì)算出的單端阻抗線寬線距、差分阻抗線寬線距如下圖所示。

10層2階HDI板1.6mm厚度疊層設(shè)計(jì)

在10層2階板疊層設(shè)計(jì)中,頂層信號(hào)L1的參考平面為L(zhǎng)2,底層信號(hào)L10的參考平面為L(zhǎng)9。建議層疊為TOP-Gnd-Signal-Gnd-Power-Signal/Pow -Gnd-Signal-Gnd-Bottom,其中L1,L2,L3,L8,L9,L10,建議采用1oZ,其它內(nèi)層采用HoZ。下圖為1.6mm板厚的參考疊層。

10層2階HDI板1.6mm厚度阻抗設(shè)計(jì)

按照疊層設(shè)計(jì)參數(shù),使用華秋dfm軟件進(jìn)行阻抗計(jì)算,計(jì)算方法與上述8層通孔一致,不一一截圖,計(jì)算出的單端阻抗線寬線距、差分阻抗線寬線距如下圖所示。

華秋DFM軟件下載地址(復(fù)制到電腦瀏覽器打開):

https://dfm.elecfans.com/uploads/software/promoter/hqdfm_hqsc.zip

專屬福利

上方鏈接下載還可享多層板首單立減50元

每月1次4層板免費(fèi)打樣

并領(lǐng)取多張無(wú)門檻“元器件+打板+貼片”優(yōu)惠券

原文標(biāo)題:一文輕松搞定PCB疊層和阻抗設(shè)計(jì)

文章出處:【微信公眾號(hào):華秋商城】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

華秋商城

+關(guān)注

關(guān)注

8文章

110瀏覽量

6108

原文標(biāo)題:一文輕松搞定PCB疊層和阻抗設(shè)計(jì)

文章出處:【微信號(hào):華強(qiáng)芯城,微信公眾號(hào):華秋商城】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

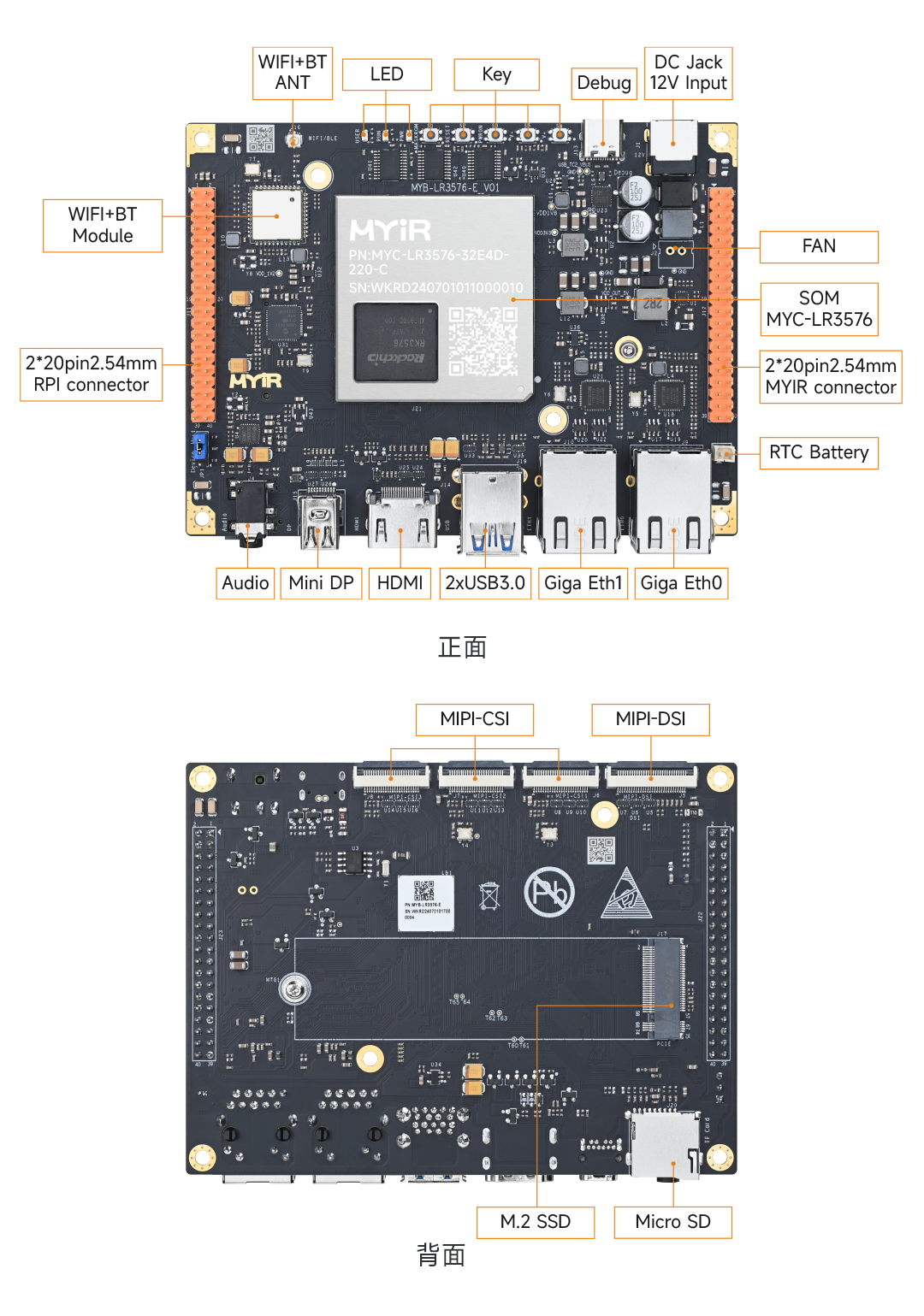

RK3576有多強(qiáng)?實(shí)測(cè)三屏八攝像頭輕松搞定

PCB線路板阻抗是怎么回事?帶你了解多層阻抗線路板的作用!

如何根據(jù)貼片疊層電感參數(shù)進(jìn)行選型

一文詳解九層板PCB結(jié)構(gòu)

一文讓你了解PCB六層板布局

PCB阻抗匹配過孔的多個(gè)因素你知道哪些?

PCB多層板為什么都是偶數(shù)層?奇數(shù)層不行嗎?

阻抗匹配有煩惱?來(lái)嘮一嘮~

PCB阻抗設(shè)計(jì)12問,輕松帶你搞懂阻抗!

谷景揭秘貼片疊層電感精度是不是越高越好

什么是PCB疊層?PCB疊層設(shè)計(jì)原則

鈣鈦礦疊層電池:Topcon與HJT底電池性能對(duì)比研究

一文輕松搞定PCB疊層和阻抗設(shè)計(jì)

一文輕松搞定PCB疊層和阻抗設(shè)計(jì)

評(píng)論