前言

隨著移動通信技術的發展,系統越趨復雜,同時產品集成度要求也越來越高,系統級封裝(SiP)成為了最具潛力的候選方案之一,其將不同制程工藝節點的裸芯片Die集成在一個封裝里,在滿足器件高性能需求的同時,也減少了芯片設計公司的研發成本和時間。

SiP有多種封裝形式,如引線鍵合、倒裝芯片、芯片堆疊、晶圓級封裝等。其中,QFN封裝由于其底部中央的一大塊裸露焊盤被焊接到PCB的散熱焊盤上,使得芯片具有極佳的電熱性能,使其能廣泛應用在射頻領域上。

一般芯片廠家主要從事片上設計,對于封裝部分交由封裝廠去進行設計,芯片設計公司為了保證射頻鏈路的阻抗連續性,需要對封裝鍵合線進行仿真,從而與片上版圖結合完成整鏈路的性能評估。

封裝廠一般只會給芯片設計公司提供DXF格式的設計文件,DXF是2D文檔,若根據封裝廠提供的三維參數進行手動建模,會相當繁瑣。為此,芯和半導體的Hermes平臺提供了Lead Frame流程解決方案,可實現QFN/QFP的DXF文件轉3D模型的快速建模,最后結合Hermes 高精度FEM三維全波電磁場求解算法可快速得到求解結果,指導設計優化。

Hermes的Lead Frame建模仿真流程

1.導入DXF設計文件

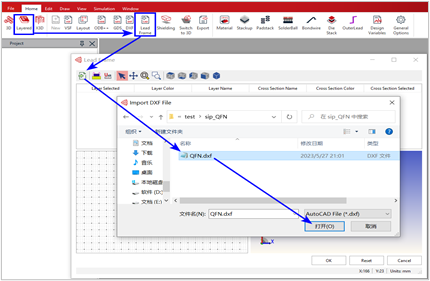

運行Hermes后,在左上角菜單欄中選擇Home的layered流程,再選擇Lead Frame流程。在彈出窗口中,選擇導入所需的DXF文件。

圖 1

Lead Frame中導入DXF文件

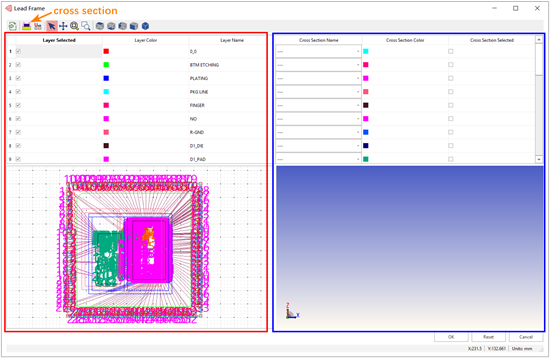

DXF文件導入后,如下圖所示。

紅色框:上方為DXF文件對應不同圖層,用戶可選擇打開不同的圖層顯示,下方為上方對應圖層的實時2D圖顯示結果。

藍色框:上方的cross section name為cross section(橙色箭頭)中配置不同圖層的選擇層,每確定選擇一個層后,下方會依據DXF中對應的圖形進行3D建模,用戶可實時查看模型的建模情況。

圖2

Lead Frame窗口說明

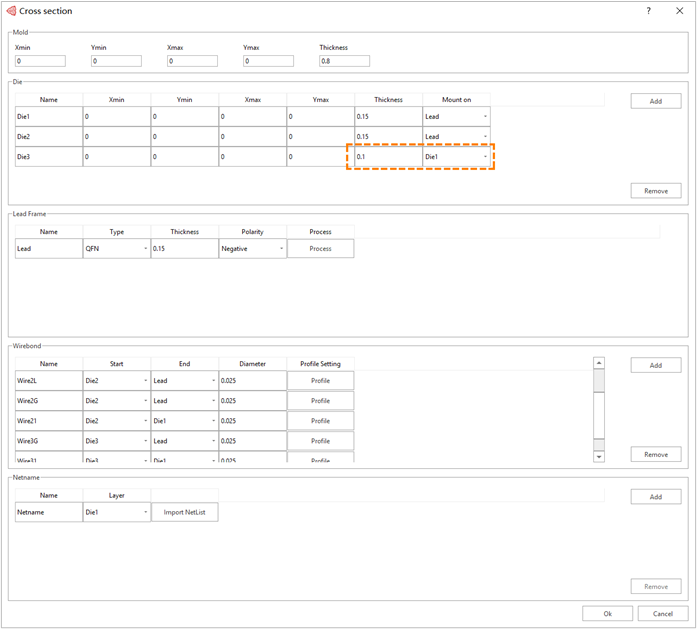

2. Cross Section的配置及說明

Mold:芯片的整體塑封外殼,此處設置高度為0.8mm。

Lead Frame:Lead層的厚度,這里設置為0.15mm。

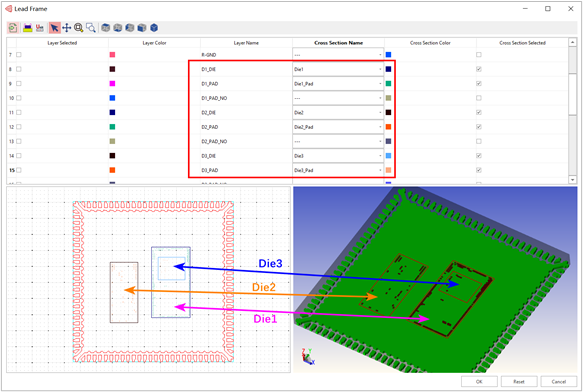

Die:芯片中Die的幾何信息,XY坐標可無需手動輸入,軟件可自動捕捉,用戶可根據實際需求,按add鍵進行Die的添加,只需要輸入每個Die的裝配高度即可。此案例中,一共有3個Die,Die1和Die2平行靠近lead放置,距離lead的高度為0.15mm,而Die3放置在Die1上,Die3的配置如下橙色框所示,參考Die1的裝配高度為0.1mm。

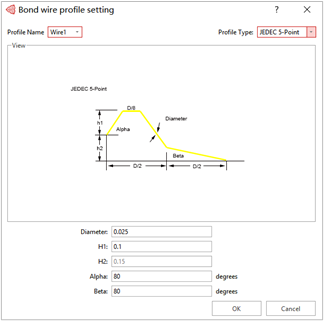

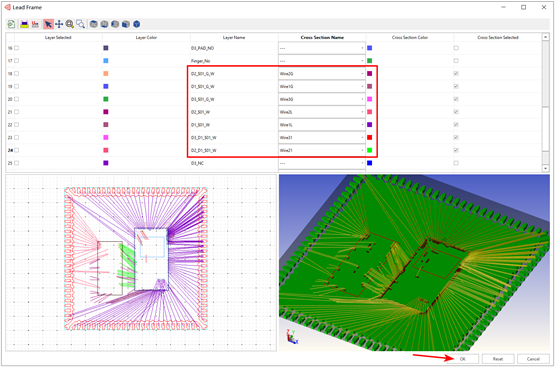

Wire bond:鍵合線層,用戶可在profile中定義鍵合線的JEDC4/5標準的相關幾何信息、線材,線寬等。Start和End分別為鍵合線打線時的起始和終止位置。此案例中,由于DXF中的wire bond圖層共有7個,所以需要設置7種wire bond組合,起始位置分別是Die1->Lead Pad、Die2->Lead Pad、Die1->E Pad、Die2->E Pad、Die3-> E Pad、Die2-> Die1、Die3-> Die1。

NetName:網絡名層,封裝廠會提供每個die上對應pad的坐標及對應網絡名的excel文件,用戶導入后,軟件可自動為對應的整個網絡賦予Excel中對應的網絡名。如果沒有Excel表格,此處可不填任何信息。

圖 3

Cross section配置設置

圖4

wire bond 的profile配置窗口

3. DXF模型的編輯及其Cross section映射配置

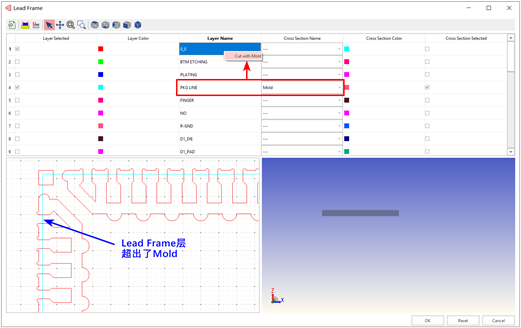

為了方便用戶使用,Hermes Lead frame流程提供了一定的編輯功能,能對導入的DXF進行有限的編輯。由于提供的DXF的Lead層超出了Mold層,需要對多出來的部分進行切割。首先把DXF的Mold層(PKG LINE)定義出來(紅色框),然后使用右鍵對DXF的Lead層(0_0)進行切割——Cut with Mold。

圖 5

Lead層編輯

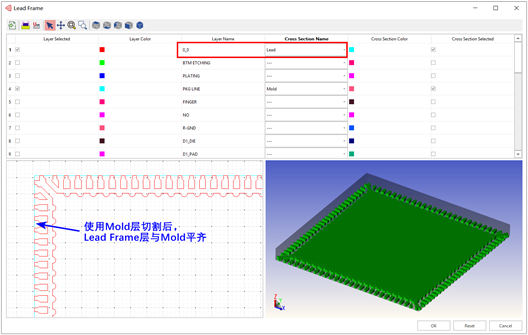

完成切割后,Lead層與Mold平齊,并定義DXF的0_0層為Lead層。

圖表 6

Lead層切割后

接著在cross section name中,為DXF對應圖層配置Die及Die Pad(下圖紅色框)。

圖 7

Die信息配置

最后完成鍵合線配置(下圖紅色框),此時,可在3D窗口中完整的查看整個QFN模型模型了。點擊OK,模型即可回導到Hermes平臺的工作界面上。

圖8

wire bond信息配置

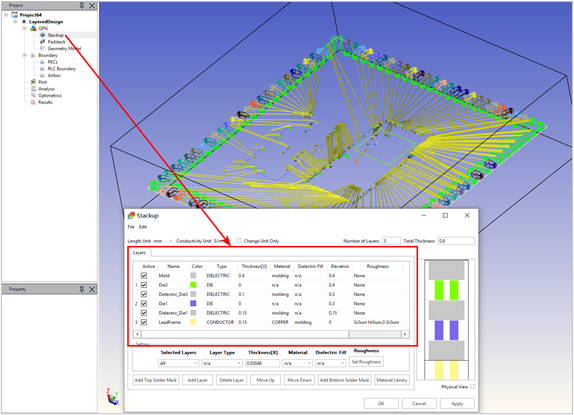

4.疊層屬性配置

模型導入到Hermes工作區后,雙擊Stackup,即可進行疊層及材料屬性等配置。

圖表 9

疊層設置

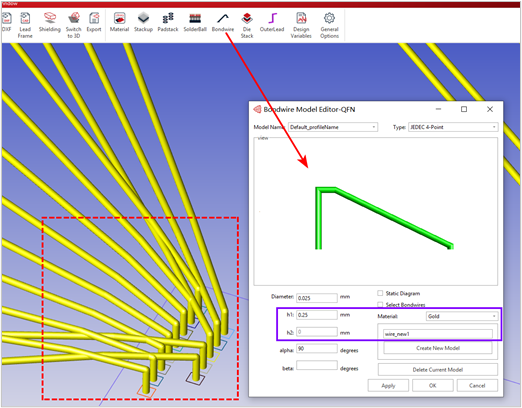

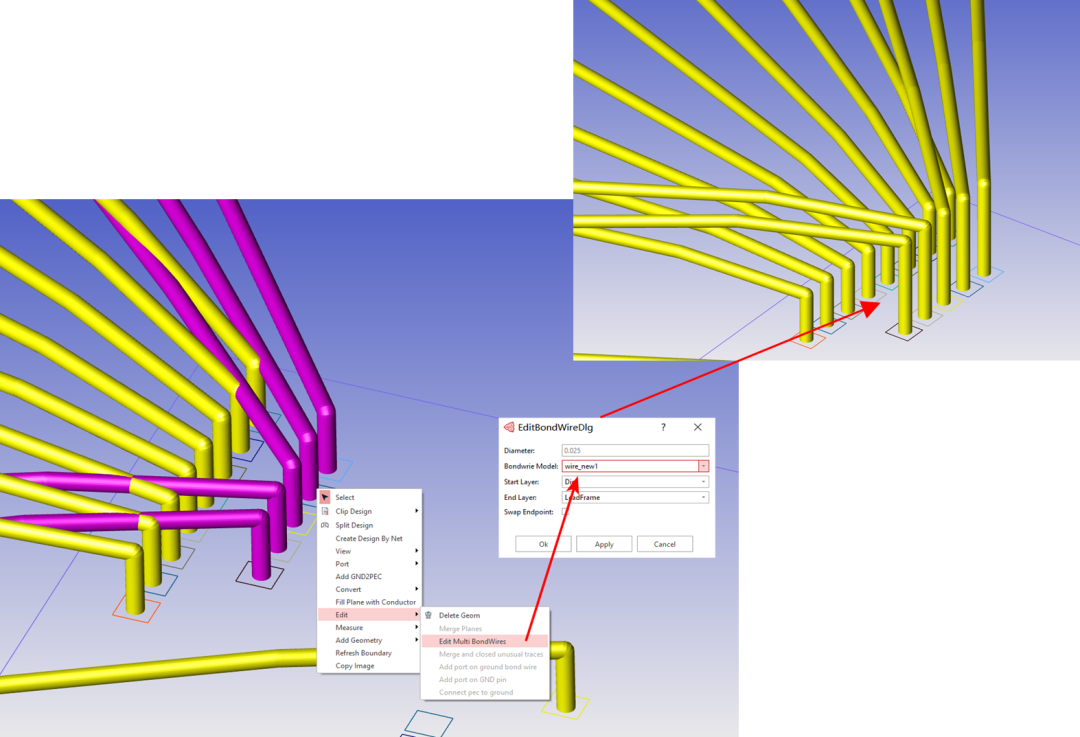

5.鍵合線的修改

如下圖紅色框所示,由于這部分的wire bond在DXF中都是同一個圖層,所以出線高度難免是一致的,造成短路問題。所以需要對Die內側的wire bond走線的起始高度進行抬高——新建一個wire bond模型,對高度及材質類型進行設置。

圖表 10

新建wire bond模型

選中需要加高的wire bond模型,右鍵編輯屬性,將其定義為上述新建的wire bond模型,至此,完成了wire bond的修改。

圖表11

對異常的wire bond進行重新定義修改

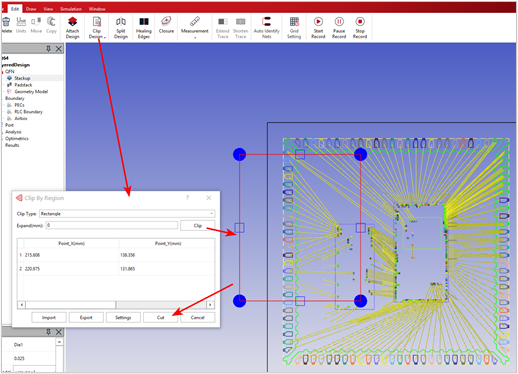

6.模型裁切

對QFN模型所需的仿真的部分進行切割。

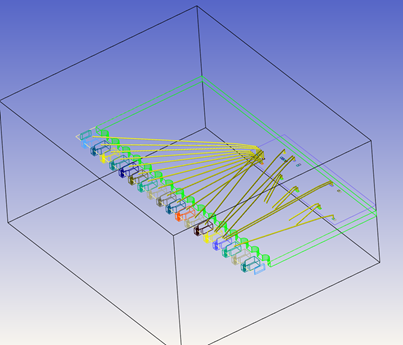

圖表 12

矩形切割

圖表 13

切割后的模型

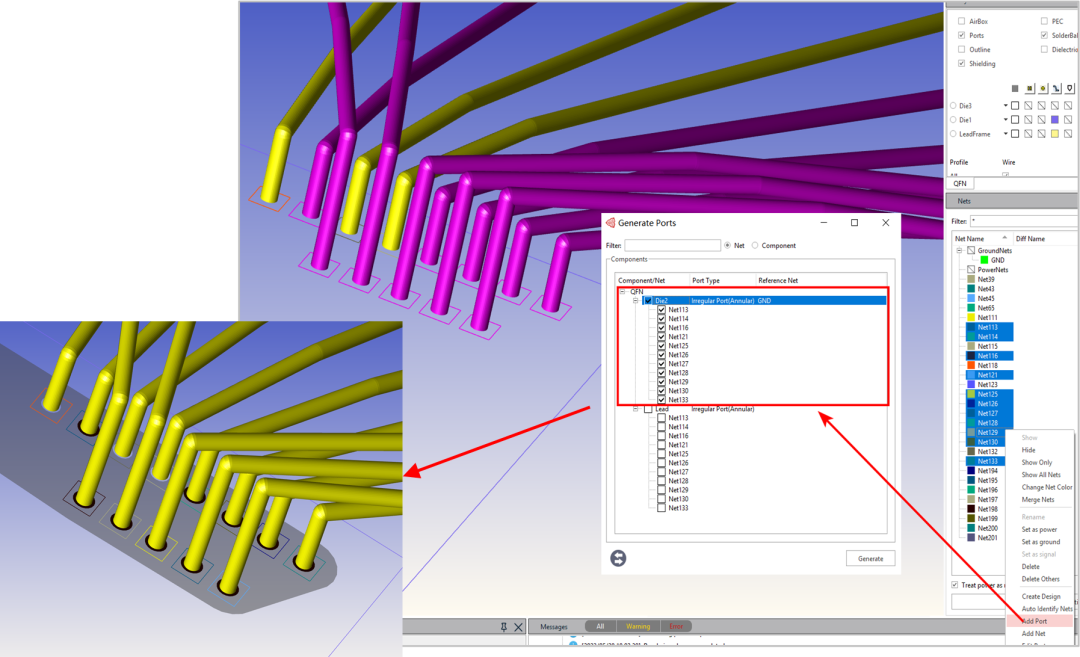

7.Port添加

圖表 14

Die上環形端口添加

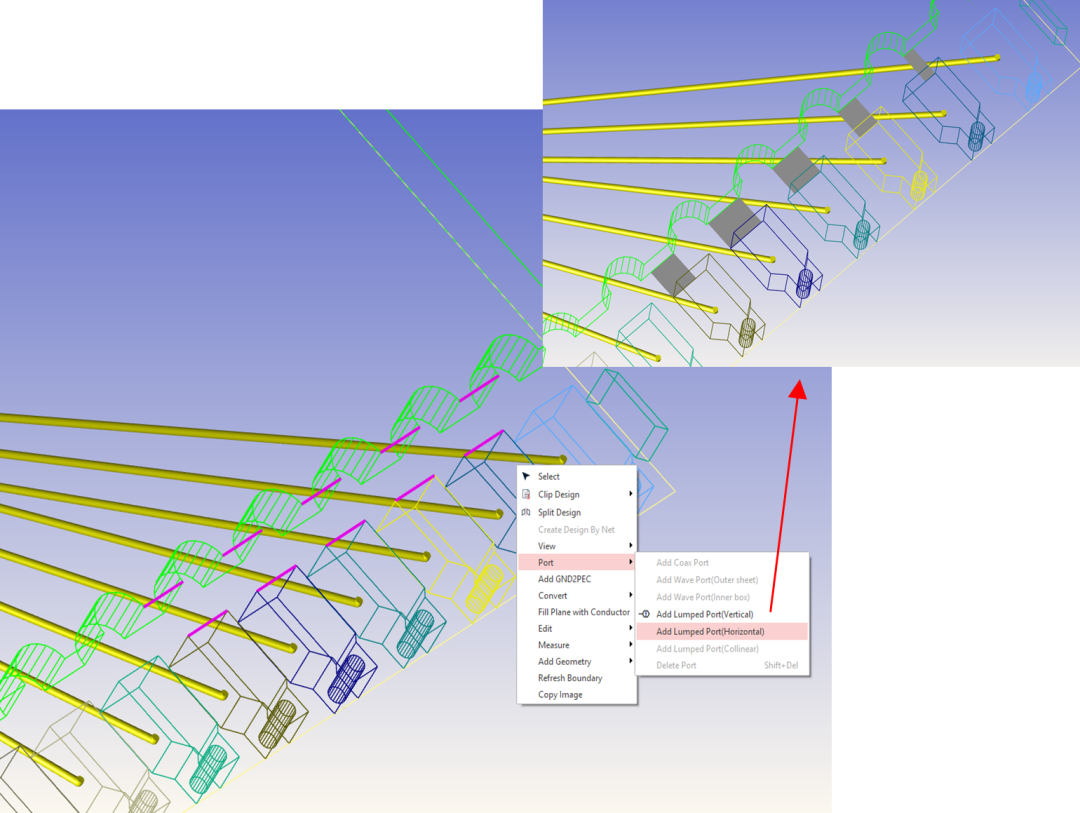

對于Lead層上pad的端口添加,可以選中pad與E pad的邊沿,然后右鍵添加水平lumped port。

圖表 15

Lead pad上lumped port添加

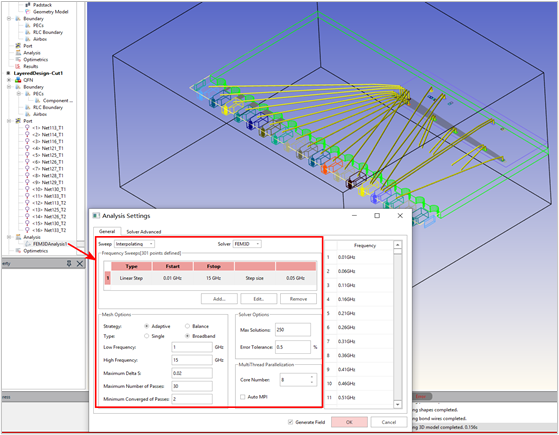

8.仿真配置

在Analysis選項中右鍵添加一個FEM3D_Analysis配置,通過solver option配置求解頻率、收斂條件、MPI以及求解Core數量等,完成后右鍵點擊Analysis開始仿真。

圖表 16

仿真配置

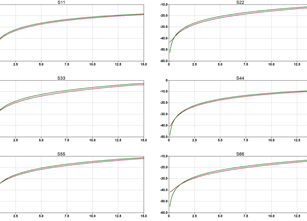

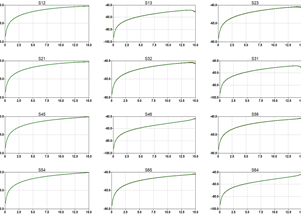

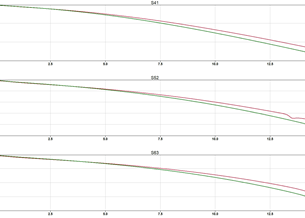

9.仿真結果查看

仿真求解完畢后,可方便地使用芯和半導體的SnpExpert工具進行S參數的批量查看及對比,下圖紅色曲線為Hermes求解結果,綠色曲線為業界知名的某FEM求解軟件結果。從左到右依次為回波損耗、插損及隔離度,其中插損相差不超過0.08dB。

--Hermes

--REF

圖表 17

仿真結果對比

(點擊各圖可查看原圖)

總結

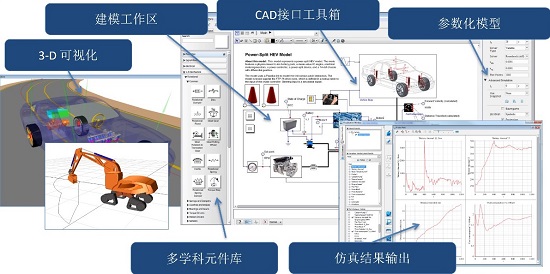

本文介紹了采用芯和半導體的Hermes平臺實現了多DIE下的QFN模型創建。Hermes內置了便捷易用的Lead Frame流程,實現了DXF 二維版圖到3D QFN模型的轉換,最后通過靈活的切割、端口創建功能快速完成模型的建模和仿真,可滿足芯片、封裝用戶對DXF設計文件進行快速建模仿真的應用場景需求。

關于芯和半導體EDA

芯和半導體提供“半導體全產業鏈仿真EDA解決方案”,是新一代智能電子產品中設計高頻/高速電子組件的重要工具,擁有領先的2.5D/3D Chiplet先進封裝設計分析全流程的EDA平臺。產品涵蓋三大領域::

芯片設計:匹配主流晶圓廠工藝節點,支持定制化PDK構建需求,內嵌豐富的片上器件模型,幫助用戶快速精準地實現建模與寄生參數提取。

封裝設計:集成多類封裝庫,提供通孔、走線和疊層的全棧電磁場仿真工具,為2.5D/3DIC先進封裝打造領先的統一仿真平臺,提高產品開發和優化效率。

系統設計:基于完全自主產權的EDA仿真平臺,打通整機系統建模-設計-仿真-驗證-測試的全流程,助力用戶一站式解決高速高頻系統中的信號完整性、電源完整性、熱和應力等設計問題。

關于芯和半導體

芯和半導體是一家從事電子設計自動化(EDA)軟件工具研發的高新技術企業,以仿真驅動設計,提供覆蓋IC、封裝到系統的具備完全自主知識產權的全產業鏈 EDA 解決方案,支持先進工藝與先進封裝,致力于賦能和加速新一代高速高頻智能電子產品的設計,已在5G、智能手機、物聯網、人工智能和數據中心等領域得到廣泛應用。

芯和半導體自主創新的下一代集成無源器件IPD平臺,以高集成、高性能、小型化為特色,為移動終端、IoT、HPC、汽車電子等客戶提供系列集成無源芯片,累計出貨量超20億顆,并被 Yole 評選為全球IPD 濾波器的主要供應商之一。

芯和半導體創建于2010年,運營及研發總部位于上海張江,在蘇州、武漢、西安設有研發分中心,在美國硅谷、北京、深圳、成都、西安設有銷售和技術支持部門。

審核編輯:湯梓紅

-

SiP

+關注

關注

5文章

506瀏覽量

105464 -

封裝

+關注

關注

127文章

7997瀏覽量

143413 -

仿真

+關注

關注

50文章

4124瀏覽量

133999 -

qfn

+關注

關注

3文章

191瀏覽量

56267 -

芯和半導體

+關注

關注

0文章

109瀏覽量

31482

原文標題:【應用案例】如何實現“多DIE的QFN建模仿真”

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于Cordic的正弦信號發生器建模仿真

DAC電流源失配建模仿真怎么做?

資料下載:基于MATLAB的風電場建模仿真研究牛步柯

為什么要進行建模仿真?

Simulink建模仿真實例快速入門

芯和的先進封裝建模仿真平臺Metis

虹科干貨|對于802.1CB協議,不同建模時的保護能力建模仿真分析

Maple—多領域系統級建模仿真和科學計算軟件

如何實現多DIE的QFN建模仿真

如何實現多DIE的QFN建模仿真

評論