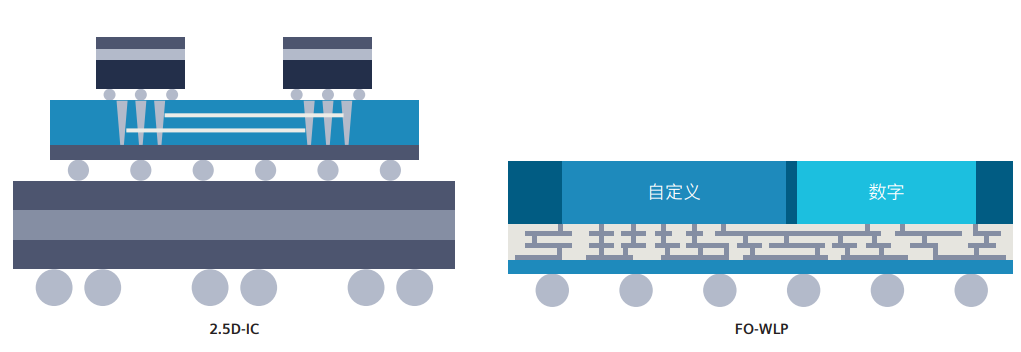

領(lǐng)先的晶圓代工廠組裝和封測代工廠 (OSAT) 已經(jīng)在為其客戶提供高密度先進(jìn)封裝(HDAP) 服務(wù)了。晶圓代工廠/OSAT 目前提供的常見方法包括 2.5D-IC(基于中介層)和扇出型晶圓級封裝(FOWLP) 方法(單裸片或多裸片),如圖 1 所示。

圖 1. 目前最常使用的封裝類型是 2.5D-IC 和 FO-WLP。

由于 2.5D-IC 的中介層類似于傳統(tǒng)的裸片(除了不包括有源器件),所以通常由 IC 設(shè)計組負(fù)責(zé) 2.5D-IC 設(shè)計,而這需要采用面向 IC 的設(shè)計方法(版圖數(shù)據(jù)庫中的曼哈頓形狀、SPICE/Verilog 作為源網(wǎng)表等)。

在 FO-WLP 中,IC 封裝組采用的設(shè)計方法通常基于電子表格(以捕捉設(shè)計意圖)、設(shè)計內(nèi)制造檢查的設(shè)計方法,而且(傳統(tǒng)上)沒有自動版圖與電路圖比較(LVS) sign-off。自動化的 LVS 過去在封裝領(lǐng)域并不流行,因為元器件和所需 I/O 的數(shù)量通常很少,一張簡單的電子表格或焊線圖足以滿足肉眼檢查的需要。但隨著 HDAP 的發(fā)展及其使用范圍的擴(kuò)大,對使用類似 LVS 的自動化流程來檢測和高亮顯示封裝連接關(guān)系錯誤的需求變得越來越明顯。

要想成功識別芯片缺陷,必須對器件應(yīng)用高質(zhì)量的測試,以及在出現(xiàn)失效時執(zhí)行準(zhǔn)確的診斷。設(shè)計人員通常選擇使用既針對固定故障,也針對各種時序故障模型的測試向量。高質(zhì)量的測試標(biāo)準(zhǔn)可以確保制造測試流程不會遺漏有缺陷的元件。

此外,嵌入式分析技術(shù)也被越來越多地用于識別芯片缺陷以及設(shè)計的預(yù)期功能中存在的異常,這些異常可能是由于缺陷,也可能是由于軟件錯誤和網(wǎng)絡(luò)安全威脅所致。本文聚焦的安全應(yīng)用需要極高水平的測試質(zhì)量,并且支持對現(xiàn)場退貨進(jìn)行全面診斷。本文將討論運(yùn)用嵌入式確定性測試來實現(xiàn)安全應(yīng)用所需的可測試性和高安全性水平的測試方法,以及如何應(yīng)用嵌入式分析技術(shù)在器件的功能層面提供一個安全層。

審核編輯:湯梓紅

-

晶圓

+關(guān)注

關(guān)注

52文章

4973瀏覽量

128313 -

IC設(shè)計

+關(guān)注

關(guān)注

38文章

1302瀏覽量

104285 -

封裝

+關(guān)注

關(guān)注

127文章

7992瀏覽量

143402 -

LVS

+關(guān)注

關(guān)注

1文章

36瀏覽量

9971

原文標(biāo)題:白皮下載丨封裝設(shè)計人員需要裝配級 LVS 進(jìn)行 HDAP 驗證

文章出處:【微信號:Mentor明導(dǎo),微信公眾號:西門子EDA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

器件高密度BGA封裝設(shè)計

簡單介紹IC的高性能封裝

直到PCBA裝配不了,才知道封裝設(shè)計絲印標(biāo)示的重要

【限時免費(fèi)】《PCB封裝設(shè)計指導(dǎo)白皮書》攜全套最新“封裝實戰(zhàn)課程”再度來襲!

解決高密度先進(jìn)封裝的設(shè)計與驗證挑戰(zhàn)

PCB設(shè)計人員需要掌握的技能

為什么需要封裝設(shè)計?

為什么需要封裝設(shè)計?

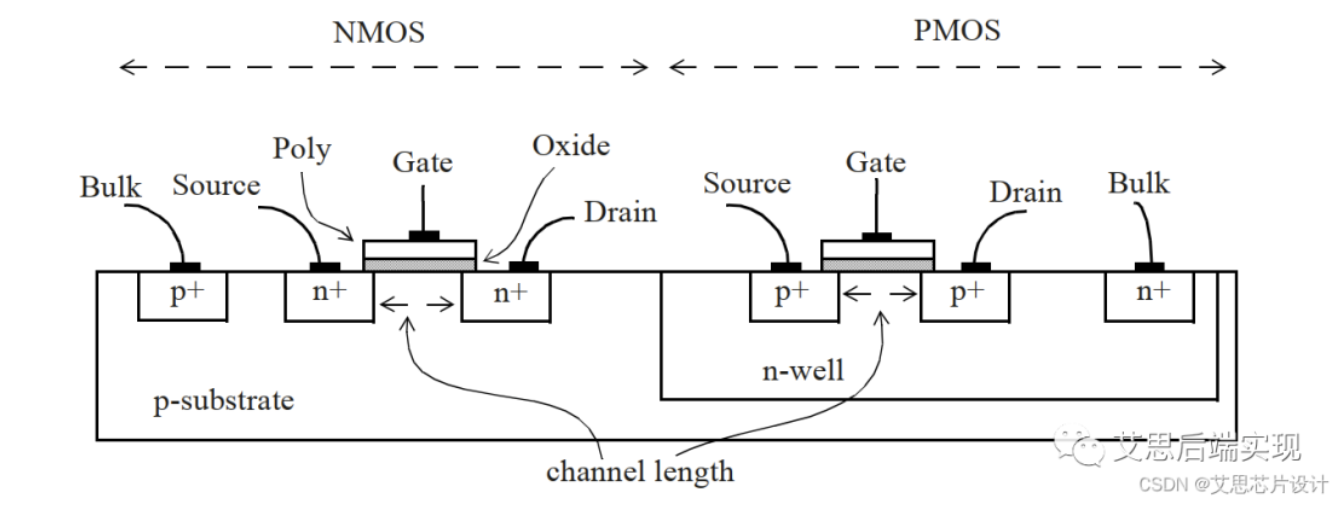

物理驗證LVS對bulk(體)的理解和處理技巧

探討一下std-cell在LVS的特殊處理

為什么需要封裝設(shè)計?封裝設(shè)計做什么?

封裝工藝簡介及元器件級封裝設(shè)備有哪些

封裝設(shè)計人員需要裝配級LVS進(jìn)行HDAP驗證

封裝設(shè)計人員需要裝配級LVS進(jìn)行HDAP驗證

評論