RISC-V、ARM 和x86微處理器之間的許多差異都很細微,并且與內(nèi)存尋址方式、分支執(zhí)行方式、異常處理方式等有關。本文將考慮更高層次的差異,并將簡要比較精簡指令集計算(RISC)和復雜指令集計算(CISC),考慮這些差異對功耗和計算性能之間的權衡的影響,看看安全性和預測性如何執(zhí)行被處理,虛擬化是如何實現(xiàn)的,最后是對RISC-V、ARM 和 x86 設備的應用程序適用性的概述。

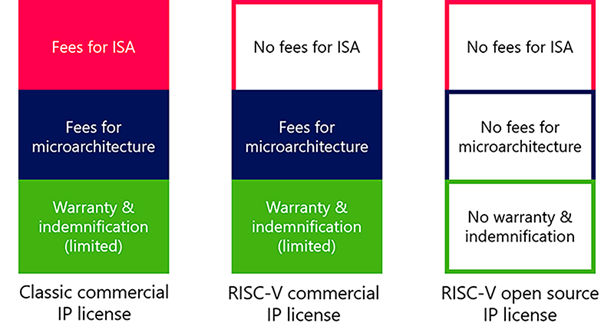

Intel的x86架構也在AMD的CPU上提供,ARM處理器和IP由ArmLimited提供,RISC-V國際組織正在開發(fā)RISC-V。英特爾、AMD、ARM 和 RISC-V之間的兩個非常顯著的區(qū)別在于商業(yè)模式和計算架構。英特爾、AMD 和 ARM 基于專有 IP,并且這些公司銷售和/或許可他們的產(chǎn)品。RISC-V是一個開放的規(guī)范和平臺;它不是開源處理器。可以使用開源 RISC-V 內(nèi)核,但也有商業(yè)許可的內(nèi)核。

RISC-V和ARM處理器在計算架構上基于RISC概念,而Intel和AMD的x86處理器則采用CISC設計。

一、RISC與CISC的計算

RISC體系結構具有可以在單個計算機時鐘周期內(nèi)執(zhí)行的簡單指令。因此,完成一項特定任務往往需要執(zhí)行多條指令。同樣的任務可以在CISC處理器上用更少的指令(甚至單個指令)完成。

CISC計算力求用盡可能少的代碼行完成一項任務。一條CISC指令可能需要多個計算機時鐘周期才能完成。例如,CISC處理器的兩個數(shù)相乘可以用一條指令完成:

MUL 1200, 1201

“MUL”是一個復雜的指令。它不需要程序員顯式使用任何調(diào)用、加載或存儲函數(shù)。它直接在計算機的內(nèi)存上運行,類似于高級編程語言中的命令。RISC

處理器上的乘法不能用單個命令完成;需要幾個更簡單的指令來從內(nèi)存中的特定位置加載每個操作數(shù)(下面示例中的 1200 和

1201),將數(shù)字相乘,然后存儲結果:

Load A, 1200

Load B, 1201

MUL A, B

Store 1200, A

在此示例中,Load指令將來自內(nèi)存位置1200和1201的數(shù)據(jù)分別存儲到寄存器A和B。MUL指令將兩個寄存器中的值相乘。它將結果保存在A中,Store指令將 A 的值存儲在內(nèi)存位置1200(或任何其他指定的內(nèi)存位置)中。在RISC處理器中,諸如MUL之類的操作僅在寄存器上執(zhí)行,而不是直接在內(nèi)存上執(zhí)行。雖然這增加了指令數(shù),但它允許使用更簡單的指令。

二、功率與性能

與CISC指令相比,執(zhí)行更簡單的 RISC 指令消耗的功率更少。CISC

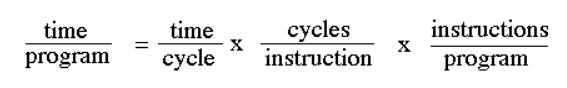

處理器試圖以每條指令的計算機時鐘周期數(shù)為代價來最小化每個程序的指令數(shù)。RISC采用相反的方法,使用可以在單個時鐘周期內(nèi)執(zhí)行的簡單指令,但需要更多的指令。以下等式顯示了計算機的性能能力(運行程序的時間)與每條指令的周期數(shù)以及每條程序的指令數(shù)之間的關系:

從這個等式來看,有兩種方法可以提高性能,最小化每個程序的指令數(shù)或減少每個指令的周期數(shù)。一般而言,RISC方法在降低整體功耗方面更為成功,有時會以降低性能為代價。然而,分歧正在縮小。ARM添加了更復雜的指令來提高處理器性能(以更高的功耗為代價)。英特爾將其一些操作碼分解為類似于RISC的微操作,以實現(xiàn)更低的功耗。

三、安全性

權限環(huán)(有時稱為保護環(huán))是為保護數(shù)據(jù)和功能免受故障、提高容錯能力和提高安全性免受惡意操作而建立的分層域。環(huán)按照從最高特權或最受信任到最低特權或最不受信任的層次結構設置。零環(huán)通常是最高特權級別,直接與

CPU 內(nèi)核和內(nèi)存交互。

x86 架構包括四個級別的特權環(huán)。ARM v7 架構包括三個特權級別;應用程序、操作系統(tǒng)和管理程序。ARM 和 RISC-V都使用隔離機制的概念。ARM 采用基于硬件的安全性,其中域被硬編碼到硬件中,而 RISC-V 使用軟件定義的隔離域。

OP-TEE 是實現(xiàn) ARM TrustZone 技術的開源可信執(zhí)行環(huán)境 (TEE)。OP-TEE 已被移植到許多 ARM 設備和平臺,包括 ARMv8。RISC-V MultiZone 安全軟件模型很小,因此速度更快。RISC-V內(nèi)置了多種安全機制,包括四級權限環(huán)、安全中斷處理和獨特的物理內(nèi)存保護(PMP)機制。RISC-V 還提供了商用安全增強功能,包括加密庫、信任根和多域

TEE。

RISC-V 的開源特性導致專有 ISA 缺乏的透明度,并為另一個級別的安全性提供了可能性。RISC-V社區(qū)龐大而多樣,許多設計人員不斷研究安全環(huán)境和潛在威脅向量。一旦識別出安全風險,它通常會與開放社區(qū)共享,使專家能夠快速開發(fā)或提出解決方案。

四、預測執(zhí)行

謂詞執(zhí)行允許某些指令僅在特定的先前條件為真時才執(zhí)行。例如,先前的結果必須大于零;否則,處理器繼續(xù)執(zhí)行下一條指令。ARM 和 x86

支持各種格式的謂詞執(zhí)行。

宏操作融合是一種硬件優(yōu)化技術,在解碼之前或解碼過程中,將一系列相鄰的宏操作合并為一個宏操作。ARM在其最近的微體系結構中支持許多宏操作融合操作。微操作融合在處理器內(nèi)部將兩條指令合二為一,有效實現(xiàn)無需指令集幫助的謂詞執(zhí)行。

基本的RISC-V指令集不支持謂詞執(zhí)行。然而,實驗性的BOOMv3亂序推測RISC-V處理器使用精簡指令集與微操作融合的組合來實現(xiàn)預測執(zhí)行。

五、CPU、內(nèi)存和I/O的虛擬化

ARM、x86 和 RISC-V 都支持 CPU 和內(nèi)存的虛擬化。RISC-V ISA 目前不支持 I/O 的虛擬化。在 x86生態(tài)系統(tǒng)中,Intel和AMD有自己的虛擬化方法。英特爾被稱為虛擬化技術或 VT。VT由 VT-x組成,包含核心側特征;VT-d,包含輸入輸出內(nèi)存管理單元(IOMMU);和 VT-c,它涵蓋了網(wǎng)絡接口。AMD在標簽AMD-V下提供核心端虛擬化,而IOMMU稱為AMD-Vi。英特爾和 AMD 的產(chǎn)品在實現(xiàn)細節(jié)上有所不同,但與 ARM

的產(chǎn)品相比,彼此的架構更加緊密。

與 x86 處理器采用的方法類似的虛擬化擴展已添加到ARM架構中。ARM虛擬化擴展使硬件方式能夠使用管理程序虛擬化 CPU。多個操作系統(tǒng)可以在每個虛擬

CPU 上運行。

RISC-V H(管理程序)擴展 v0.6.1 引入了 CPU 狀態(tài)的完整副本:一份副本用于來賓,一份副本用于主機(類似于 IntelVT-x)。RISC-V通過將敏感寄存器和指令賦予主機模式特權來支持 CPU 的虛擬化。從預發(fā)布版本號可以看出,RISC-V虛擬化是一項正在進行的工作。最近發(fā)布了用于嵌入式系統(tǒng)的 Rocket 芯片內(nèi)核中最新版本的 RISC-V 虛擬機管理程序擴展的首次公開實施和評估。

與x86和ARM架構一樣,RISC-V支持使用多階段頁表的內(nèi)存虛擬化。此外,RISC-V為來賓表和主機表實現(xiàn)了相同的頁表條目格式。

I/O虛擬化在RISC-V中留待指定。它主要是IOMMU和平臺級中斷控制器(PLIC)的一個特性,它位于RISC-VISA的域之外,需要指定。當前指定的 PLIC 不包括用于配置中斷注入的寄存器。

六、RISC-V和ISA的擴展

RISC-V

從一開始就設計為不僅支持基本ISA和標準擴展,而且還支持自定義ISA擴展。雖然ARM最初并未設計為使用自定義擴展,但這種情況正在發(fā)生變化,并且ARM生態(tài)系統(tǒng)開始使用自定義擴展。x86生態(tài)系統(tǒng)是封閉的,一般不支持自定義ISA擴展。

RISC-V ISA被組織成指令組(基本 ISA 和標準擴展)。使用對標準ISA的擴展的能力可以為特定應用程序提供支持。例如,最近發(fā)布的 RISC-V向量擴展(RVV)使基于RISC-VISA的處理器內(nèi)核能夠與傳統(tǒng)標量運算一起處理數(shù)據(jù)數(shù)組,以加速大型數(shù)據(jù)集上單指令流的計算。適合矢量處理器的任務示例包括:

(1)機器學習。

(2)壓縮圖像、zip文件等。

(3)密碼學。

(5)語音和手寫。

(6)奇偶校驗、校驗和。

(7)散列/連接。

RISC-V

ISA支持自定義擴展的能力可以成為特定用例或應用程序的關鍵區(qū)別。使用自定義擴展不會破壞與主要ISA的合規(guī)性。支持自定義擴展的處理器也可以運行通用 RISC-V

軟件。

上圖顯示了RISC-V軟件堆棧中的自定義ISA擴展。操作系統(tǒng)(OS)可以是實時操作系統(tǒng)(如embOS、FreeRTOS、LynxOS等),也可以是富操作系統(tǒng)(如Linux、Android、Windows等)。在此示例中,App1

確實需要性能增強并且不使用自定義 ISA 擴展。它可以符合標準編譯器。App2 和 App3 使用自定義 ISA 擴展來提高性能,并且必須使用包含自定義 ISA

擴展的編譯器進行編譯。

所以,x86、ARM和RISC-V微處理器之間的差異很多而且各不相同。這些差異推動了一般應用程序的適用性。來自AMD和Intel的x86處理器在計算機和服務器領域占據(jù)主導地位。在平板電腦和智能手機上,蘋果和高通的ARM處理器占主導地位。ARM處理器在嵌入式應用中也很強大。隨著

RISC-V 越來越多地用于嵌入式系統(tǒng)、汽車系統(tǒng)、磁盤驅動器、人工智能和機器學習應用程序,這種優(yōu)勢正在受到挑戰(zhàn)。

-

ARM

+關注

關注

134文章

9165瀏覽量

369170 -

微處理器

+關注

關注

11文章

2274瀏覽量

82769 -

X86

+關注

關注

5文章

295瀏覽量

43560 -

RISC-V

+關注

關注

45文章

2322瀏覽量

46587

發(fā)布評論請先 登錄

相關推薦

RISC-V、ARM與x86微處理器之間有什么區(qū)別?

RISC-V、ARM與x86微處理器之間有什么區(qū)別?

評論