今天我們要介紹的時序分析概念是 spice deck 。平時用得可能比較少,是PT產(chǎn)生的一個spice信息文件,可以用來和HSPICE做correlation。我們平時使用PT做得是gate level的時序分析,如果想做transistor level的時序分析,那可以采用HSPICE做電路仿真。

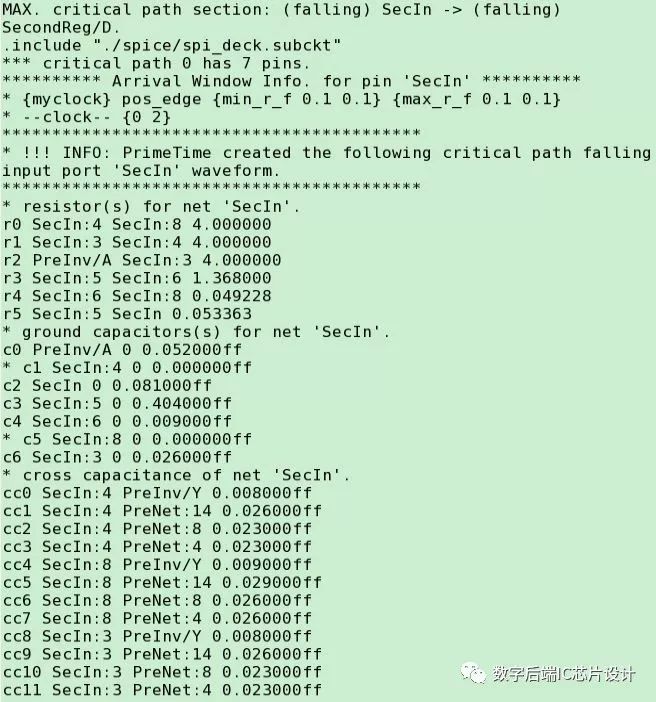

但是,如果要完全仿真整個網(wǎng)表是不大現(xiàn)實的,因為規(guī)模太大,速度難以接受。在PT里面,提供了一種方法,可以采用write_spice_deck命令來產(chǎn)生某一條timing path的spice網(wǎng)表文件,里面包含該條timing path上的resistors, capacitors信息。這對表征新工藝庫的準確性是很有幫助的。如下圖所示:

使用方法

write_spice_deck

pt_shell> write_spice_deck

-header header.spi \\ spice model信息文件

-output testcase.spi \\

-sub_circuit_file ./subckt.spi \\ spice subcircuit信息文件

[get_timing_paths -from A2 -to buf5/A] timing path

-

仿真器

+關(guān)注

關(guān)注

14文章

1019瀏覽量

83939 -

時序分析

+關(guān)注

關(guān)注

2文章

127瀏覽量

22617 -

SPICE仿真

+關(guān)注

關(guān)注

1文章

27瀏覽量

6449 -

時序分析器

+關(guān)注

關(guān)注

0文章

24瀏覽量

5293

發(fā)布評論請先 登錄

相關(guān)推薦

時序分析概念之spice deck介紹

時序分析基本概念介紹<Operating Condition>

時序分析基本概念介紹&lt;generate clock&gt;

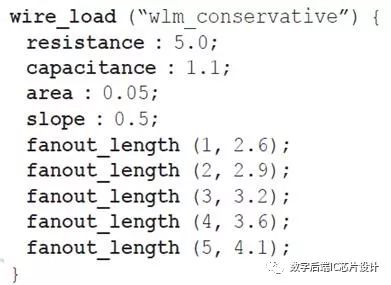

時序分析基本概念介紹&lt;wire load model&gt;

時序分析基本概念介紹&lt;ILM&gt;

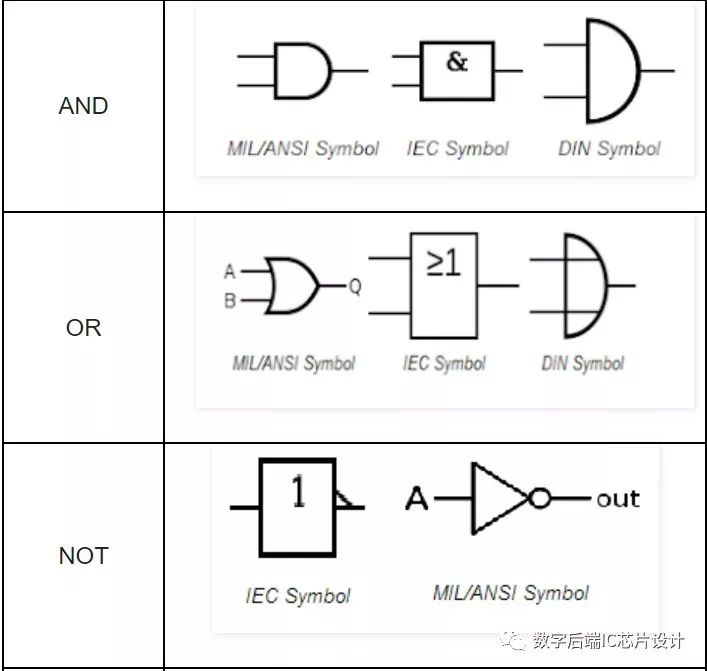

時序分析基本概念介紹&lt;Combinational logic&gt;

時序分析基本概念介紹<spice deck>

時序分析基本概念介紹<spice deck>

評論