semiengineering.com; JUNE 15TH,2023

High-Density Fan-Out Packaging With Fine Pitch Embedded Trace RDL

高密度扇出封裝與細間距嵌入式線路RDL;具有有機介電層的雙大馬士革工藝(Dual Damascene, DM)銅制程克服了細線路定義的挑戰。

在新冠疫情期間,人工智能(AI)、高性能計算(HPC)和數據中心應用對高性能設備的需求大幅增加。與此同時,集成電路(IC)行業努力將硅技術節點最小化,以滿足在緊密成本約束下對計算性能的無休止要求。目前,使用納米片技術引入了2納米節點技術。該設計在相同功耗下提供了45%的速度提升,與7納米節點相比。然而,隨著節點尺寸的減小和晶圓產出顯著降低,設計成本和開發時間大幅增加,因為微小的缺陷可能會導致單個芯片的整體功能受損。芯片組技術是克服這些限制、以合理和可承受的價格為消費者提供最先進產品的最有效解決方案之一。

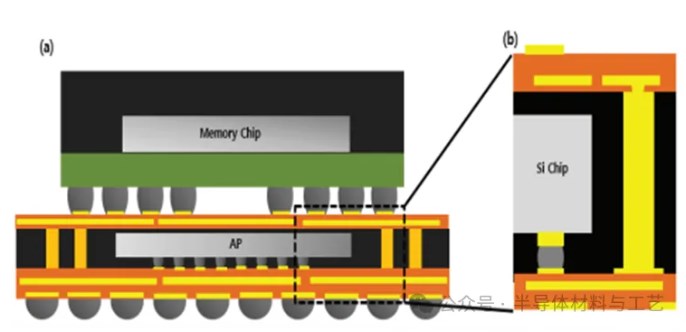

芯片組將先進節點大小的核心模塊與小型芯片分開,以提高晶圓產出并重復使用先前節點模塊的知識產權(IP),以降低設計成本。為了互連這些具有不同節點大小和不同材料的異構塊芯片,需要采用先進的集成電路封裝技術。以往,多芯片模塊(MCM)翻轉芯片球柵陣列(FCBGA)一直被傳統采用作為層壓基板上多芯片的異構接口。然而,由于基板的電路徑顯著長,它不適用于先進節點IC。采用2.5D硅穿孔(TSV)技術的模塊接口作為高性能封裝的新候選方案被引入,其具有極短的電路徑,但由于硅間質的限制,在高頻(4-6 GHz)應用中性能有限[1]。因此,最近出現了一種高密度扇出(HDFO)接口,它去除了硅(Si)和無機介質,并采用有機介質。特別是Amkor Technology的HDFO被稱為基于硅片的扇出技術(S-SWIFT)封裝,為異構集成提供了更高帶寬的芯片間互連。

先前的研究已經證明了它的出色性能[1, 2]。為了展示S-SWIFT方法,需要解決許多關鍵的設計方面,包括:微細間距μ-凸點接口、在熱組裝過程中準確控制組件的翹曲、毛細管封裝、過模封裝技術、穿模界面(如Cu高柱)、中端線(MEOL)過程和模側凸點過程。高密度重分布層(RDL)技術是展示HDFO插接模塊可行性的核心技術之一。HDFO中的RDL提供芯片間的接口,需要更高密度的RDL來互連具有較小節點大小的芯片塊。半添加工藝(SAP)用于制造HDFO模塊的RDL。

然而,SAP在定義細間距特征方面面臨一些挑戰。細線可能會因為高縱橫比而坍塌,由于與基板的接觸面積小,可能會出現分層,并且用作模板的光刻膠可能會殘留在通孔中[3]。為了克服這些問題,提出了一種使用有機介電層的DM銅制程的方法。在過程中,嵌入在有機介電層中的RDL可以防止種子層下挖問題。通過光刻在味之素疊層膜(ABF)型聚合物層上實現了DM銅制程的RDL [4]。評估了DM銅制程RDL在高頻應用中的優勢。隨后,引入了一種實現DM銅制程RDL中小通孔的特殊制作方法[5]。使用高數值孔徑(NA)(0.48)的光刻工具,實現了顯著高分辨率的RDL(500納米)。還研究了使用光刻和干法刻蝕的方法進行DM銅制程RDL的聚苯并噁唑(PBO)制作[6]。討論了干法刻蝕后的開裂和銅電沉積后的過載問題。

為了克服上述挑戰,開發了一種嵌入式線路RDL(ETR)工藝,并驗證了ETR的圖案性能和可靠性。為了實現ETR,進行了關鍵的工藝優化和材料修改。同時,還演示了使用ETR將ASIC、高帶寬存儲器(HBM)和基板相互連接的S-SWIFT封裝。這些設計元素成功通過了JEDEC標準的可靠性測試。

嵌入式線路RDL的能力

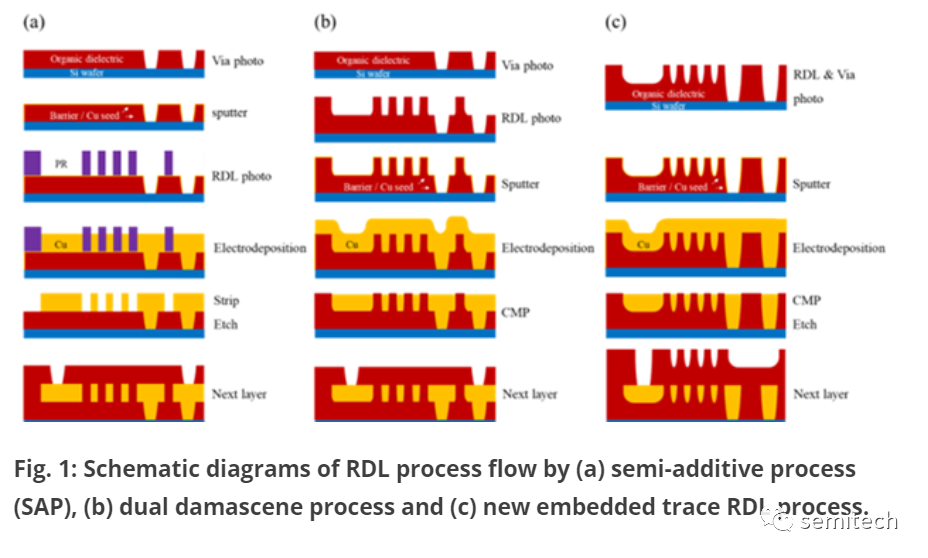

SAP通常用于制造通用封裝的RDL,其標準工藝流程如圖1(a)所示。首先,在載體晶圓上旋涂液態光可顯有機介電層,并通過光刻將通孔圖案對準。為了使Cu RDL能夠電沉積,通過濺射工藝在后烘烤的介電膜上沉積了屏障和Cu種子層。在種子層上,按照光刻膠(PR)工藝對齊RDL圖案,并進行Cu RDL的電沉積。最后,順序剝離和刻蝕PR模板以及Cu/屏障層。如前所述,由于其方便和可靠的工藝性能,SAP是通用IC封裝RDL解決方案的主流技術。然而,通過SAP進行RDL的尺寸縮小存在種子層下挖或側壁刻蝕等挑戰[7]。

通過在介電層中嵌入線路,可以解決這些挑戰而無需刻蝕過程。如圖1(b)和(c)所示,通過在預形成的鈍化層上電沉積Cu,并去除Cu過載,將DM銅嵌入有機介電圖案中。這種結構沒有Cu坍塌風險,也沒有側壁刻蝕問題,三面面對的屏障金屬具有增強的可靠性。此外,DM銅結構在高頻信號傳遞特性方面具有優勢,因為即使在高頻信號中電流集中在淺層RDL表面時,三面面對的光滑Cu表面受電子散射的影響較小。[4]在圖1(b)的頂部顯示了在有機介電膜上形成具有RDL和通孔的DM銅結構的工藝流程。通孔和RDL結構是通過兩遍光刻工藝分別形成的,其中包括有機介電材料的旋涂、軟烘烤、紫外(UV)曝光、顯影和熱固化過程。

通過采用新穎的光刻技術,簡化了先前的工藝流程。如圖1(c)的頂部所示,通過對厚涂有機介電膜進行單次紫外(UV)曝光,可以形成通孔和RDL圖案。與當前的DM銅方法相比,這種方法減少了40%的RDL工藝步驟,甚至比SAP減少了33%。因此,工藝成本也可以降低。此外,由于通孔和RDL可以通過一次特殊設計的光刻遮罩進行形成,可以避免通孔和捕獲墊之間的錯位。

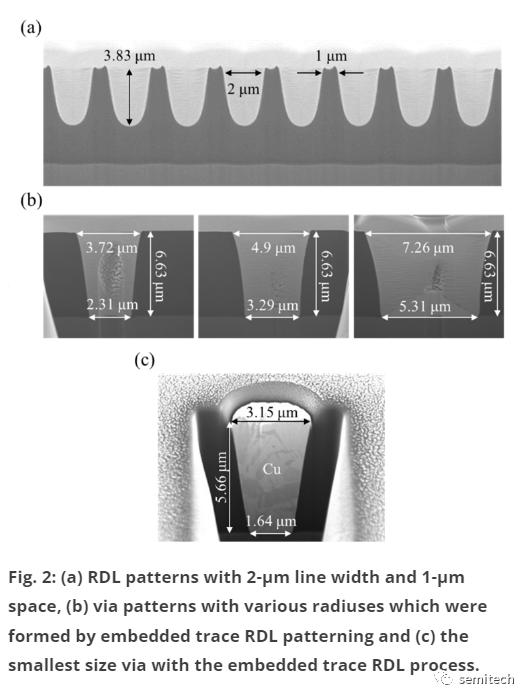

新的ETR工藝的圖案能力如圖2所示。可以形成具有2/1 μm線/空間的RDL溝槽圖案(圖2(a))和各種尺寸的通孔圖案(圖2(b))。如圖2(c)所示,ETR的最小通孔分辨率在頂部為3.15 μm,在底部為1.64 μm。這種方法在先進電路設計方面也具有優勢。在通孔和RDL層疊加期間,RDL層需要一個用于補充對準工具的布局精度的捕獲墊,但ETR工藝則不需要。因此,額外的區域可以用于RDL,從而增加RDL的密度。

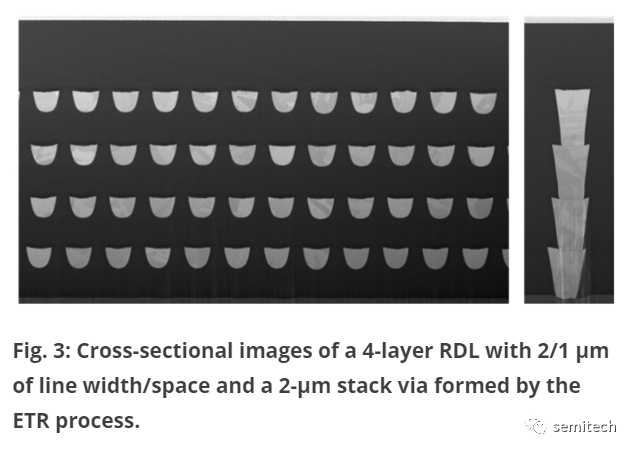

圖3展示了ETR工藝的RDL層疊加能力。由于細小的RDL圖案形成在介電膜的頂部,并且每個層面都是平坦的,因此ETR工藝可以實現顯著穩定的層疊加。使用ETR工藝可以獲得具有2/1-μm線/空間和堆疊的無墊通孔,關鍵尺寸為2 μm的四層RDL。

關鍵工藝開發

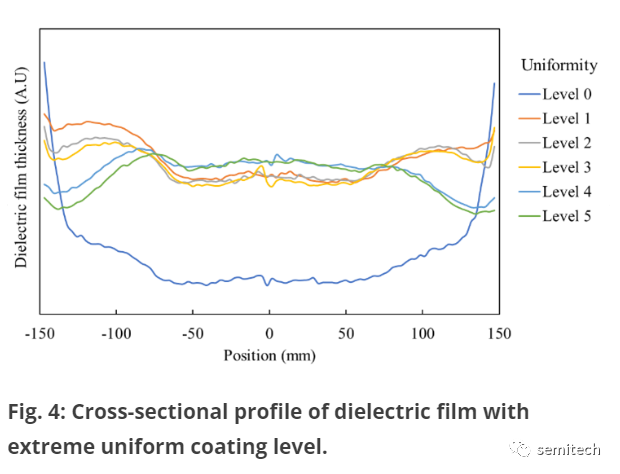

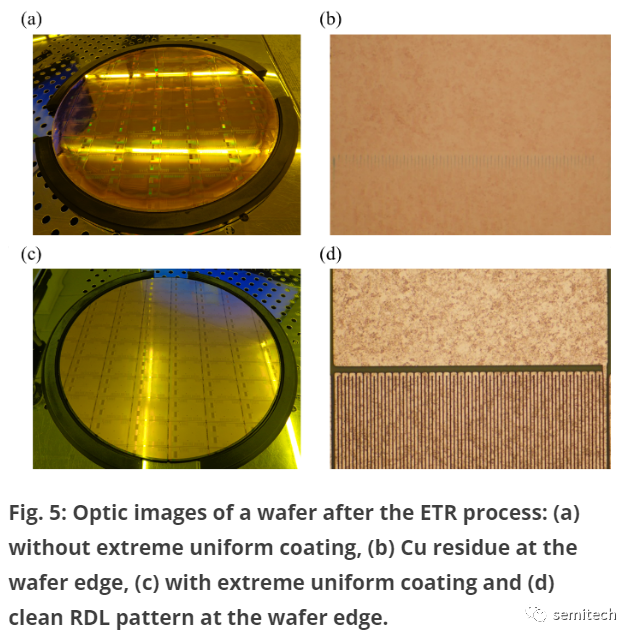

為了實現ETR工藝,需要從旋涂有機介電膜開始對工藝參數進行精細控制。開發了極端均勻涂覆技術,以防止在有機介電膜的非均勻涂覆區域形成的化學機械拋光(CMP)陰影中產生金屬殘留物。圖4顯示了隨著極端均勻涂覆因子水平的變化,有機介電膜的橫截面厚度分布的變化。在均勻度水平為0的情況下,未應用極端均勻涂覆。從晶圓邊緣到180毫米處存在0.26 μm的涂覆高度差,導致CMP產生陰影。因此,在DM工藝后,晶圓邊緣殘留了較厚的Cu殘留物,盡管中心區域清晰可見。從圖5(a)和(b)的整個晶圓和放大圖像中可以看出,晶圓邊緣的RDL電路短路。

隨著極端均勻涂覆水平的提高,晶圓邊緣的CMP陰影減小。隨著極端均勻涂覆水平增加到3級,凹型曲率涂覆剖面減小,而采用極端均勻涂覆水平4時,變為凸型涂覆剖面,沒有CMP陰影。此外,由于采用極端均勻涂覆,膜厚總差異從未進行極端均勻涂覆的0.47 μm降低到進行極端均勻涂覆水平4的0.12 μm。由于極端均勻涂覆減小了CMP陰影,DM銅工藝后晶圓邊緣不會殘留Cu殘留物。這在圖5(c)中顯示,并且晶圓邊緣的放大圖像顯示在圖5(d)中。因此,通過應用顯著改善涂覆均勻性的4級涂覆配方,實現了非常高的良率。

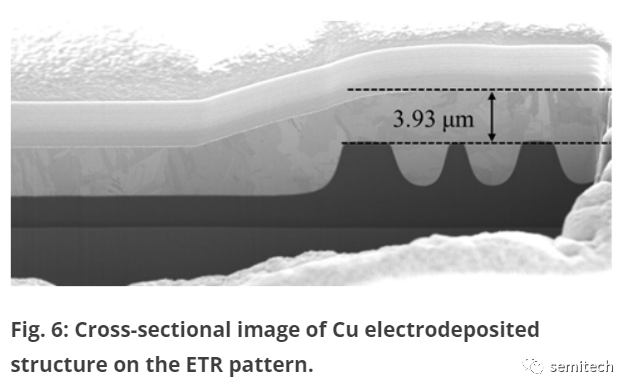

圖6顯示了具有寬且細的RDL混合圖案的Cu電沉積ETR結構的橫截面圖像。在細小的RDL和小孔圖案的狹窄溝槽結構中,可以實現快速的Cu填充,這是因為電鍍液中的加速劑集中在Cu生長表面的大曲率區域上,并減小了曲率[8]。最初,這種孔填充原理僅適用于SAP方法中的小孔,但在DM銅工藝中,它也適用于狹窄溝槽結構。然而,在寬RDL的大溝槽中,由于除了溝槽角部分以外沒有具有大曲率的區域來集中加速劑物種,因此孔填充不起作用。因此,溝槽底部的電鍍速率幾乎與頂部表面平行,并且為了填充寬RDL,不可避免地需要在頂部表面形成較厚的過盈層。因此,需要進行大量的Cu CMP。

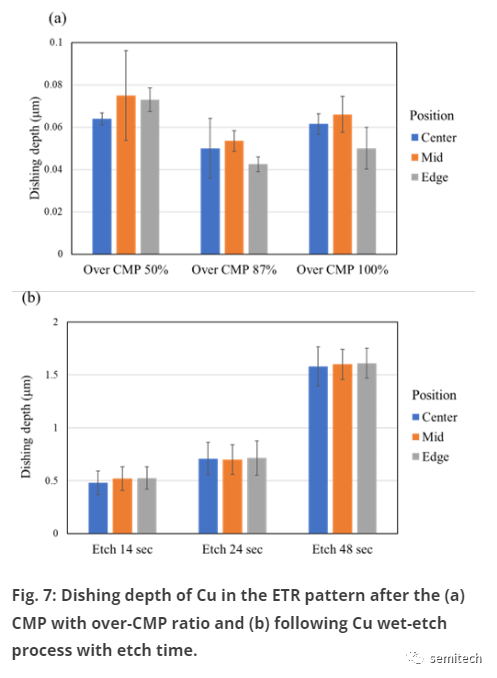

DM銅工藝的Cu CMP過程通常使用3個CMP平臺的3個步驟進行:(1)大塊Cu去除,(2)Cu拋光和(3)阻擋層和氧化層去除。在ETR工藝中,通過將Cu CMP與單個CMP平臺和濕法蝕刻工藝相結合,簡化了Cu去除過程。這種方法有利于降低工藝成本和提高工藝速度。首先,使用單個CMP平臺進行高速Cu CMP工藝進行大塊Cu去除。幾乎4μm的Cu過盈層以900 nm/min的去除速率迅速去除。在這種情況下,全晶圓區域的CMP均勻性的精細控制是困難的。因此,不可避免地需要超過CMP來完成整個晶圓表面的大塊Cu去除,并且阻止層的作用對于防止與過度CMP相關的問題(如過度凹陷或金屬或介電層消失)非常重要。圖7(a)顯示了晶圓區域的凹陷深度在整個超過CMP比例的情況下都受到均勻控制,且不超過90 nm,因為CMP停止層限制了超過CMP。

Cu殘留物在去除CMP和阻擋層之后通過經濟高效的濕法蝕刻工藝而不是多步驟的CMP去除。Cu濕法蝕刻工藝清除了Cu殘留物。此外,由于刻蝕時間可以均勻控制Cu凹陷,因此還可以實現額外的Cu RDL高度控制,如圖7(b)所示。最后,阻擋層也通過標準的濕法蝕刻工藝清除。

S-SWIFT演示

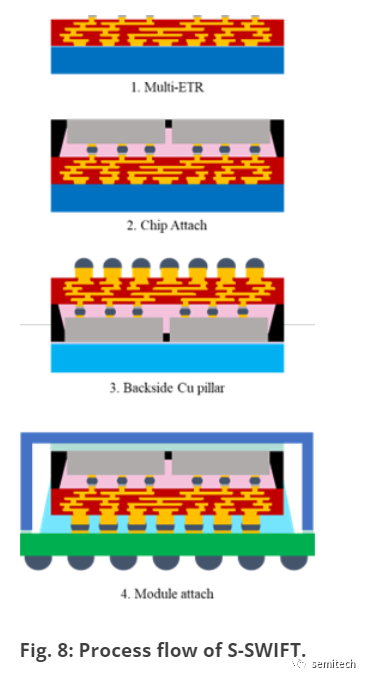

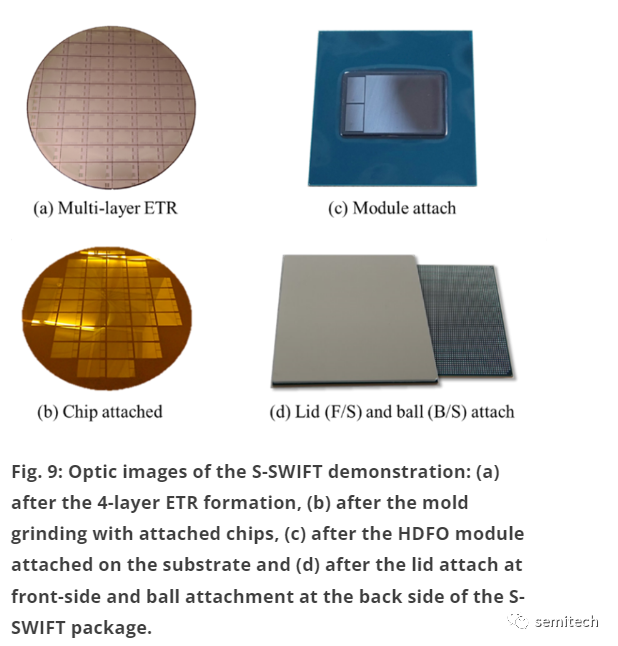

使用如圖8所示的標準S-SWIFT組裝流程進行了ETR的S-SWIFT演示[1]。四層ETR疊加在硅晶圓上,無鉛焊料微球在ETR頂部進行電沉積。將帶有ASIC和HBM的多芯片與微球對齊,并通過質量回流工藝連接。接下來,在ETR和多芯片之間進行毛細管填充。隨后,使用環氧模具化合物(EMC)對連接的芯片進行模具化處理,然后進行模具研磨以暴露多芯片以接觸熱界面材料(TIM)。使用紫外可分離膠粘劑在HDFO的前側上附著第二載體晶圓,并通過晶圓研磨和干法刻蝕工藝組合將背側晶圓移除,以形成背側的Cu柱。在Cu柱和無鉛焊料電沉積之后,使用紫外激光去除載體晶圓,并進行晶圓鋸切工藝。單個模塊被貼附在層壓基板上,并在模塊和基板之間施加填充材料。然后,使用TIM材料將蓋子貼附在S-SWIFT模塊的前側,并在背側附著焊球。

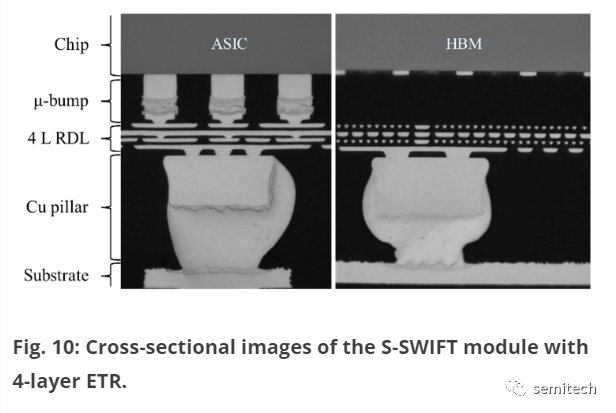

圖9顯示了S-SWIFT組裝過程的順序圖像。即使使用了SAP的標準組裝參數而沒有進行任何修改,S-SWIFT組裝仍然成功地進行了演示,沒有出現任何問題。如果對HDFO模塊使用了不同的RDL制造方法和不同的有機介電材料,由于機械特性的微小差異和包裝中可用的結構區域,它們可能對組裝過程沒有明顯影響。通過圖10中的橫截面圖像可以確定芯片和基板上的所有焊球都良好地附著在HDFO模塊上。雖然本文未提及,但通過X射線分析和掃描聲學斷層掃描(SAT)也已經確認了這一點。因此,可以得出結論,通過使用ETR的S-SWIFT封裝實現了多芯片和基板的異質互連。

可靠性性能

由于ETR周圍的種子層充當屏障,ETR的結構在電流、熱和濕度對可靠性的影響方面具有優勢。特別是,該層阻止了Cu離子在偏壓高度加速應力測試(BHAST)期間由電流流動進入封裝層。

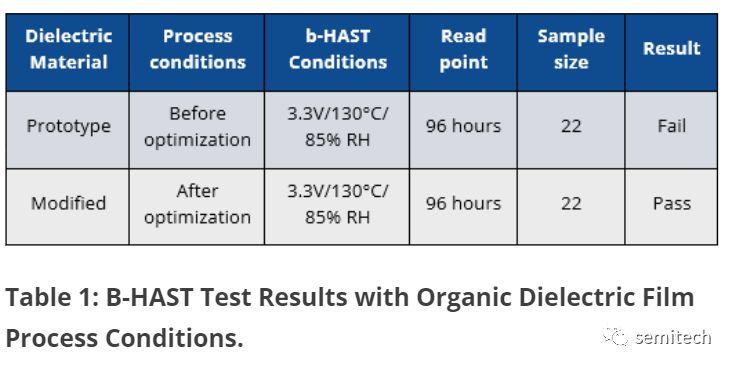

制作了兩層具有組合結構電路的ETR以驗證Cu離子遷移特性。在85%濕度和130°C條件下,對具有3.3 V偏壓的組合電路進行了96小時的BHAST。在此測試中使用了原型有機介電材料。在BHAST后,大多數組合電路由于來自沒有屏障層的ETR頂部的Cu離子遷移而短路(表1)。

在BHAST期間,有機介電材料內部的Cu離子遷移現象類似于金屬的電沉積過程[9]。組合電路陽極處的Cu被3.3V陽極電位離子化,并通過有機介電材料內部的水分,隨著溫度的支持而遷移到組合電路的陰極。Cu離子在組合電路的陰極處通過陰極電位被還原為Cu。這一連鎖反應導致了組合電路之間的樹枝狀Cu電極形成,從而引起了短路故障。最初,可以通過控制反應物的擴散來控制該反應。首先,通過控制工藝條件,防止水分吸附到聚合物內部。結果,水分吸收隨著優化的工藝條件而減少。接下來,進行了介電材料改進,以防止Cu被陽極電位電離。因此,抑制了Cu的陽極反應和通過水分擴散的反應物。因此,如表I所示,使用改進的有機介電材料和優化的RDL工藝條件制備的樣品通過了BHAST測試。這些改進的介電材料和優化的工藝條件被用于成功展示具有4層RDL的S-SWIFT封裝的可行性。

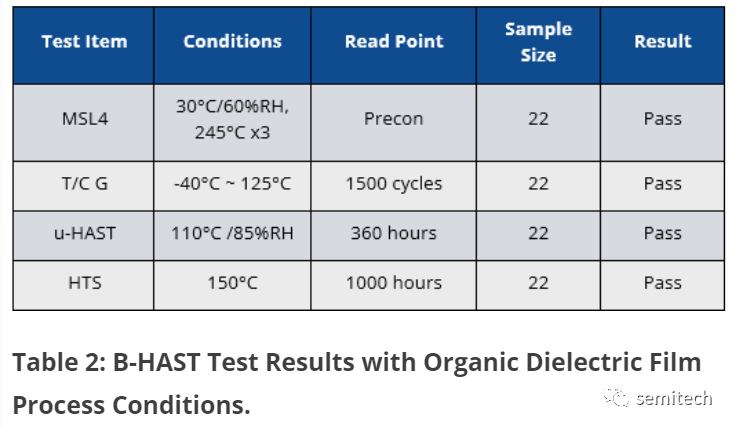

可靠性測試被用于評估S-SWIFT封裝中的ETR結構。所有可靠性測試條件,包括濕度浸泡等級4(MSL4),溫度循環測試條件G(T/C G),非偏壓高加速應力測試(UHAST)和高溫存儲(HTS)測試都符合JEDEC標準。如表2所示,所有樣品通過了T/C G 1500個周期、UHAST 360小時和HTS 1000小時的測試。

結論

嵌入式線路RDL已經成為先進的高密度風扇封裝的RDL制造工藝,采用了一種具有減少周期時間和結構優勢的新型光刻技術。它提供了一種有效的方法來實現具有小于2/1 μm線/空間和無捕獲墊的多層RDL。由于RDL層的平整性,ETR的疊層能力已經確認可以達到6層。通過實施均勻涂覆、CMP和濕法腐蝕等創新的單元工藝技術,成功制備了ETR。通過修改介電材料和優化工藝條件的努力,改善了HAST中的可靠性。

最后,通過使用ETR技術和Flip Chip組裝實現了ASIC和HBM的異構集成,成功演示了S-SWIFT封裝。組裝的單元通過了行業標準的器件級可靠性要求。

-

嵌入式

+關注

關注

5092文章

19178瀏覽量

307691 -

封裝

+關注

關注

127文章

7996瀏覽量

143410 -

介電材料

+關注

關注

0文章

15瀏覽量

7121

原文標題:Amkor: 高密度扇出封裝與細間距嵌入式線路RDL

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Amkor:高密度扇出封裝與細間距嵌入式線路RDL

Amkor:高密度扇出封裝與細間距嵌入式線路RDL

評論