內(nèi)容提要

● Cadence 和 Samsung 的合作,使客戶能夠利用兩個公司最新的技術(shù),進(jìn)行手機、汽車、AI 和超大規(guī)模設(shè)計的創(chuàng)新

● 工程師們能夠在 PDK 上設(shè)計 IC 產(chǎn)品,這些 PDK 已經(jīng)過 SF2 和 SF3 流程認(rèn)證

●Cadence 數(shù)字全流程針對先進(jìn)節(jié)點實現(xiàn)了最佳 PPA 結(jié)果

●Cadence 定制/模擬工具,包括基于 AI 的 Virtuoso Studio,已針對最新節(jié)點進(jìn)行優(yōu)化

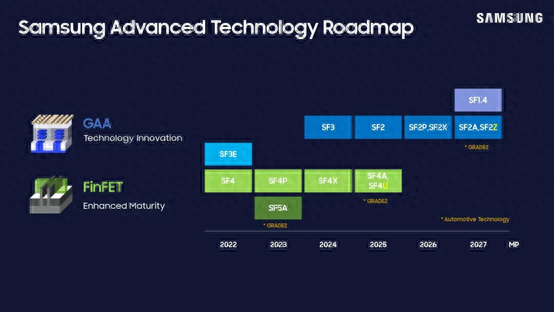

中國上海, 2023 年 7 月 5 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,其數(shù)字和定制/模擬流程已通過 Samsung Foundry 的 SF2 和 SF3 工藝技術(shù)認(rèn)證。兩家公司還合作開發(fā)了新的制程設(shè)計套件(PDK),旨在簡化于這些最新節(jié)點上的移動、汽車、AI 和超大規(guī)模 IC 產(chǎn)品的流程。雙方的共同客戶現(xiàn)正在積極使用 Cadence流程,全力開發(fā)基于 SF2 和 SF3 工藝的設(shè)計。

Cadence 數(shù)字工具

針對 SF2 和 SF3 技術(shù)進(jìn)行優(yōu)化

Cadence 全面的 Cadence RTL-to-GDS 設(shè)計流程支持 Samsung 的 SF2 和 SF3 技術(shù),可提供最佳的功率、性能和面積(PPA)結(jié)果。該流程包括 GenusSynthesis Solution、Modus DFT Software Solution、InnovusImplementation System、QuantusExtraction Solution 及 Quantus Field Solver、TempusTiming Signoff Solution 以及 Tempus ECO Option、PegasusVerification System、LiberateCharacterization Portfolio、VoltusIC Power Integrity Solution 和 Cadence CerebrusIntelligent Chip Explorer。

借助這個經(jīng)過認(rèn)證的流程,客戶能輕松實現(xiàn)先進(jìn)節(jié)點上的 IC 設(shè)計。比如支持單元交換旨在幫助設(shè)計人員對齊單元引腳,進(jìn)行直接連接,以節(jié)省布線資源;支持混合行(各種組合)解決方案,以最大化基于面積的設(shè)計規(guī)則;利用有 mask 位移的單元和在水平方向上有半軌道位移的單元,工具具有擺放和精細(xì)調(diào)整走線的能力,可以減少移位;支持各種直線型不規(guī)則形狀的標(biāo)準(zhǔn)單元,以實現(xiàn)更高的密度;以及插入增強過的、兼顧 trim metal 的通孔釘,以減少壓降。

Cadence 定制/模擬工具

針對 SF2 和 SF3 技術(shù)經(jīng)過優(yōu)化

Cadence 定制和模擬工具針對 Samsung 的 SF3 和 SF2 節(jié)點經(jīng)過優(yōu)化,包括基于 AI 的 VirtuosoStudio 設(shè)計工具——Virtuoso Schematic Editor、Virtuoso ADE Suite 及 Cadence Virtuoso Layout Suite——SpectreSimulation Platform——Spectre X Simulator、Spectre FX 及 Spectre RF,以及 Voltus-XFi Custom Power Integrity Solution。

定制/模擬設(shè)計工具是客戶的得力助手,可提供更好的工藝角仿真管理、統(tǒng)計分析、中心化設(shè)計和電路優(yōu)化;支持在現(xiàn)代計算集群、私有云及公共云配置上并行操作;在整個 layout 環(huán)境中提供更好的性能和可擴展性;混合信號 OpenAccess 設(shè)計套件與 Innovus Implementation 的擺放和布線引擎無縫集成,提高結(jié)果質(zhì)量;匯總 EM-IR 信息,高亮違例和詳細(xì)的電阻值、金屬層、寬度和長度信息;提供電路性能和可靠性方面的反饋。

“得益于此次與 Cadence 的合作,已有客戶成功利用 Cadence 經(jīng)過認(rèn)證的設(shè)計流程和我們先進(jìn)的 SF2 和 SF3 工藝技術(shù)提高了生產(chǎn)力,”Samsung Electronics 代工廠設(shè)計技術(shù)團隊副總裁 Sangyun Kim說,“利用新的 PDK,開發(fā)人員在開發(fā)下一代移動、汽車、人工智能和超大規(guī)模設(shè)計的時候能更簡單、更快地將創(chuàng)新產(chǎn)品推向市場。”

“Cadence 研發(fā)團隊與 Samsung Foundry 團隊精誠合作,針對 Samsung 的 SF2 和 SF3 工藝技術(shù)精細(xì)調(diào)整我們相應(yīng)的數(shù)字和定制/模擬流程,以幫助客戶提高設(shè)計效率,”Cadence 數(shù)字和簽核事業(yè)部副總裁 Vivek Mishra表示,“我們的數(shù)字流程有PPA方面的優(yōu)勢,而我們的定制/模擬流程依托 Virtuoso Studio,為定制 IP 開發(fā)設(shè)定了新的標(biāo)準(zhǔn),助力雙方的共同客戶利用 Samsung 的 SF2 和 SF3 工藝技術(shù)推進(jìn)產(chǎn)品創(chuàng)新。”

Cadence 的數(shù)字和定制/模擬設(shè)計流程支持 Cadence 的智能系統(tǒng)設(shè)計(Intelligent System Design)戰(zhàn)略,旨在實現(xiàn)系統(tǒng)級芯片(SoC)的卓越設(shè)計。

-

IC設(shè)計

+關(guān)注

關(guān)注

38文章

1302瀏覽量

104286 -

Cadence

+關(guān)注

關(guān)注

65文章

930瀏覽量

142454 -

人工智能

+關(guān)注

關(guān)注

1796文章

47673瀏覽量

240289

原文標(biāo)題:Cadence 數(shù)字和定制/模擬設(shè)計流程獲得 Samsung Foundry SF2 和 SF3 工藝技術(shù)認(rèn)證

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

三星3nm良率僅20%,仍不放棄Exynos 2500處理器,欲打造“十核怪獸”

三星SF4X先進(jìn)制程獲IP生態(tài)關(guān)鍵助力

Banana Pi BPI-RV2 RISC-V路由開發(fā)板采用矽昌通信SF2H8898芯片

兩種原理的六氟化硫(SF6)傳感器技術(shù)解析?

六氟化硫SF6氣體泄漏報警監(jiān)測系統(tǒng):紅外監(jiān)測,高效嚴(yán)謹(jǐn)

Cadence與Samsung Foundry開展廣泛合作

SF6 N2混合氣體回收分離設(shè)備的操作順序——每日了解電力知識

Cadence與Intel Foundry的戰(zhàn)略合作取得重大成果

概倫電子NanoSpice通過三星代工廠3/4nm工藝技術(shù)認(rèn)證

新思科技物理驗證解決方案已獲得臺積公司N3P和N2工藝技術(shù)認(rèn)證

XeF2和SF6可以相互替換嗎?XeF2和SF6對硅腐蝕的區(qū)別?

Cadence數(shù)字和定制/模擬流程通過Samsung Foundry的SF2、SF3工藝技術(shù)認(rèn)證

Cadence數(shù)字和定制/模擬流程通過Samsung Foundry的SF2、SF3工藝技術(shù)認(rèn)證

評論