01

概述

(1)定義:信號在傳輸線傳播的過程中遇到阻抗不連續時造成部分信號回彈的現象,稱之為反射。

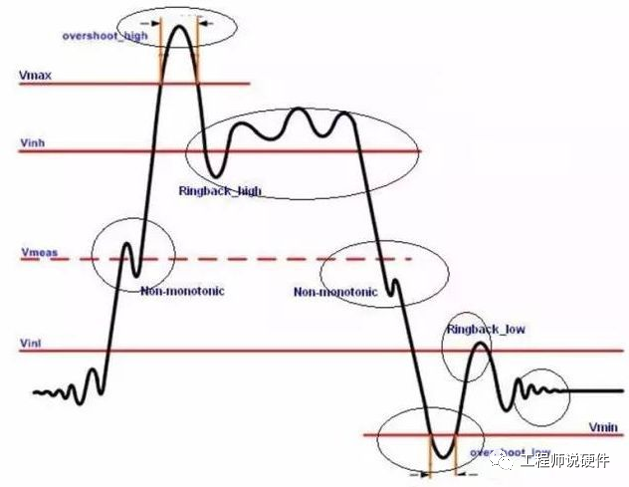

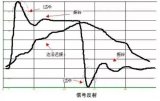

反射的影響:反射會帶來過沖、振鈴、回溝等一系列現象,容易造成器件失效、邏輯判斷出錯、EMI等問題。

圖1 反射問題示意圖

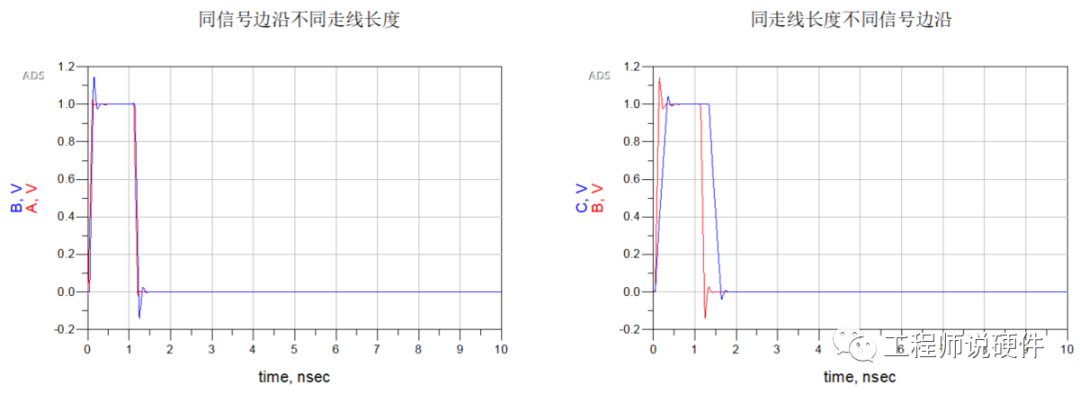

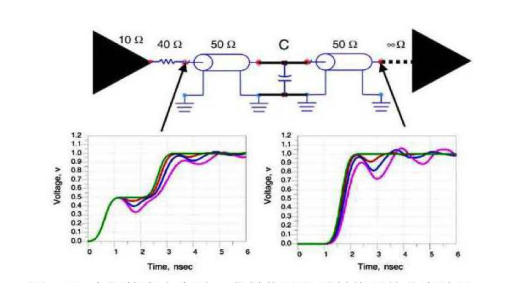

(2)什么時候需要考慮反射:只有當走線的長度達到高速信號定義時需要考慮反射(信號邊沿小于4~6倍的走線時延)。如果走線很短,產生的反射會被掩蓋在邊沿之中。

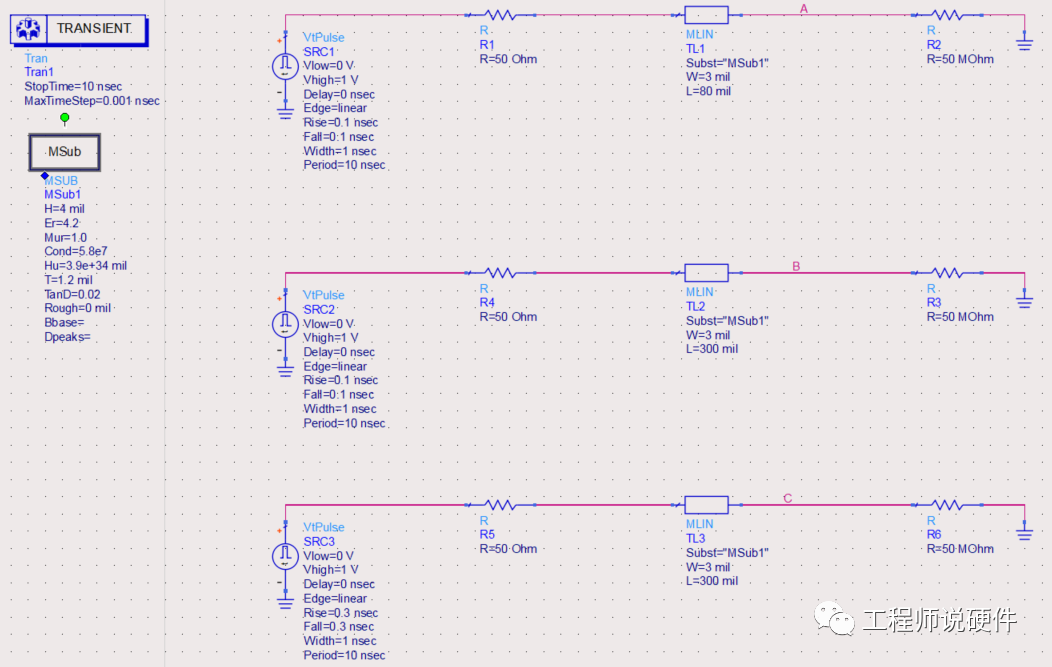

如下圖邊沿時間為0.1ns和0.3ns的信號在60mil和300mil走線不連續情況下的仿真結果。

圖2、3 ADS仿真:不同邊沿和走線長度對信號的影響

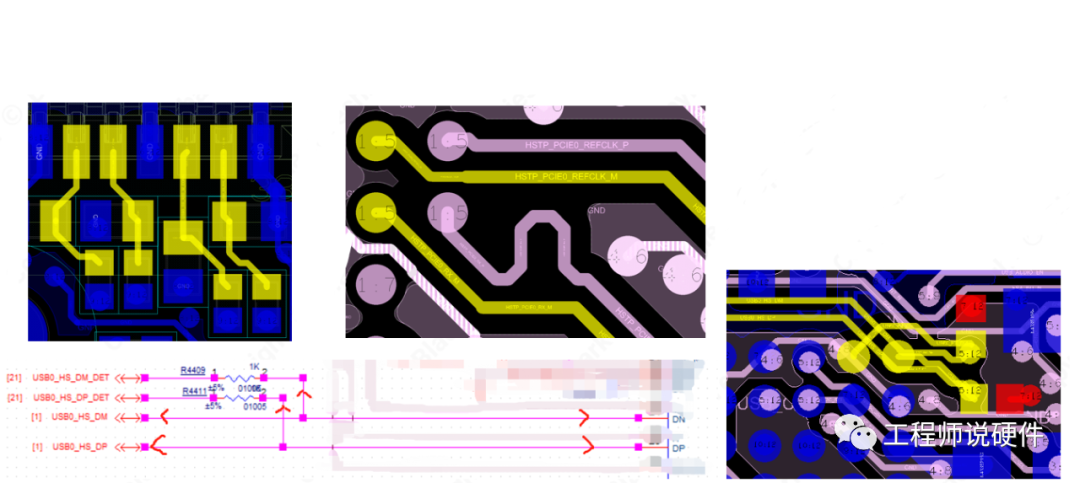

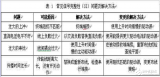

(3)傳輸過程中任何不均勻都會導致阻抗不連續,從而產生反射,比如線寬變化、過孔、連接器、走線分支等。

實際設計中,對于高速走線需要盡量減少過孔數量、同一層盡量保證走線寬度一致、減少走線分支。

圖4 PCB中造成反射的常見案例

02

正負反射

(1)反射系數:反射信號與入射信號的比值,反射系數為正,則該反射為正反射。反射系數為負,該反射為負反射。

公式:

-

連接器

+關注

關注

98文章

14661瀏覽量

137241 -

emi

+關注

關注

53文章

3602瀏覽量

128202 -

信號完整性

+關注

關注

68文章

1417瀏覽量

95635 -

ADS仿真

+關注

關注

1文章

71瀏覽量

10506

原文標題:信號完整性基礎--反射(一)[20230705]

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高速互連信號串擾的分析及優化

信號完整性(五):信號反射

基于PCB信號完整性的反射設計

信號完整性簡介及protel信號完整性設計指南

信號完整性:反射是如何產生的?

10個和高速PCB設計相關的重要知識分享

信號完整性基礎-反射

信號完整性基礎-反射

評論