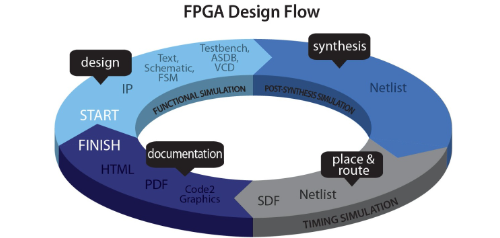

FPGA是一種可編程芯片,因此FPGA的設計方法包括硬件設計和軟件設計兩部分。硬件包括FPGA芯片電路、存儲器、輸入輸出接口電路等器件。軟件是對應的VHDL程序和VerilogHDL程序。FPGA采用自上而下的設計方法,從系統級設計開始,然后逐漸分為二級單元和三級單元,直到知道基本邏輯單元或IP核可以直接操作。通常,設計過程包含以下步驟:

1.功能定義/設備選擇

在FPGA設計項目開始之前,必須有系統功能的定義和模塊的劃分。此外,根據任務要求,如系統功能和復雜性,工作速度與電線的資源、成本和分配性應保持平衡。然后選擇正確的設計方案和適當的設備類型。

2.Design輸入

設計輸入包括原理圖輸入和硬件描述語言輸入。原理圖輸入直觀,但不容易仿真。此外,它效率低下且難以維護。它不利于模塊構建和重用。主要缺點是其便攜性差。當芯片升級時,所有原理圖都需要更改。硬件語言包括VHDL,VerilogHDL,SystemC等。硬件描述語言輸入的共同特點是語言與芯片技術無關,有利于自上而下設計,便于分區和移植模塊。它們具有良好的便攜性,強大的邏輯描述和模擬功能。

3.功能仿真

功能仿真,也稱為預仿真,用于在編譯之前驗證用戶設計的電路的邏輯功能。此時,沒有延遲信息,只有函數的初始檢測。

4.合成

所謂綜合,就是把上層抽象層次的描述轉化為下層的描述。集成優化可以根據邏輯連接產生的分層設計平面,優化目標和要求,實現FPGA布局和布線軟件。在當前級別,綜合是將設計輸入編譯成一個邏輯連接網絡表,該網絡表由基本邏輯單元(如AND門、析取門、逆變器、RAM、觸發器等)組合在一起。它不是一個真正的柵極電路。

5.Post合成模擬

仿真是為了檢查合成結果是否與原始設計一致。在仿真中,當將合成生成的標準延遲文件去標記到合成仿真模型中時,可以估計柵極延遲的影響。但是,這一步無法估計線路的延遲,因此與布線后的實際情況仍有一定的差距,這不是很準確。

6.實現和布局路由

布局路由可以理解為使用實現工具將邏輯映射到目標設備結構的資源,以確定邏輯的最佳布局,并選擇該邏輯以連接到連接到輸入/輸出功能的布線通道并生成適當的文件(諸如配置文件和相關報告)。實現方式是在特定FPGA芯片上配置合成生成的邏輯網絡表。

7.時序模擬

時序仿真又稱后仿真,是指將布局布線的時延信息標注回設計網絡表,以檢測是否存在任何時序不規則(即不滿足時序約束或器件固有的時序規則,如建立時間、維護時間等)。時序仿真中包含的延遲信息是最完整和準確的,可以更好地反映芯片的實際運行情況。

8.板級仿真和驗證

板級仿真主要用于高速電路設計。分析了高速系統的信號完整性、電磁干擾等特性,一般由第三方工具進行仿真和驗證。

9.芯片編程與調試

設計的最后一步是芯片編程和調試。芯片編程是數據文件的生成(比特流文件/比特流生成)。然后將程序數據下載到FPGA芯片。邏輯分析儀是FPGA設計的主要調試工具。但是需要很多測試引腳,而且LA很昂貴。目前,主流FPGA芯片制造商都提供嵌入式在線邏輯分析儀。

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606067 -

FPGA設計

+關注

關注

9文章

428瀏覽量

26632 -

可編程芯片

+關注

關注

0文章

52瀏覽量

18655

發布評論請先 登錄

相關推薦

fpga設計流程包含哪幾個部分

fpga設計流程包含哪幾個部分

評論