濾波器是信號(hào)處理技術(shù)繞不過(guò)的內(nèi)容,而在BSPK的實(shí)現(xiàn)框圖中,也需要用到濾波器。

m序列的時(shí)域波形是一個(gè)矩形,矩形在頻譜上是所有奇次諧波之和,為了節(jié)省帶寬資源,這里需要使用FIR濾去諧波,留下基波。

本文會(huì)講到Vivado 中FIR IP核的使用方法,會(huì)涉及到MATLAB的部分內(nèi)容。

因?yàn)槲覀儾皇褂锰呒?jí)的功能,只使用最基礎(chǔ)的功能,濾波。所以,最關(guān)鍵的內(nèi)容就是coe參數(shù)文件的生成,可以使用MATLAB幫助我們生成這個(gè)文件。

在MATLAB的命令窗口,輸入fdatool(新版MATLAB為filterDesigner)回車,

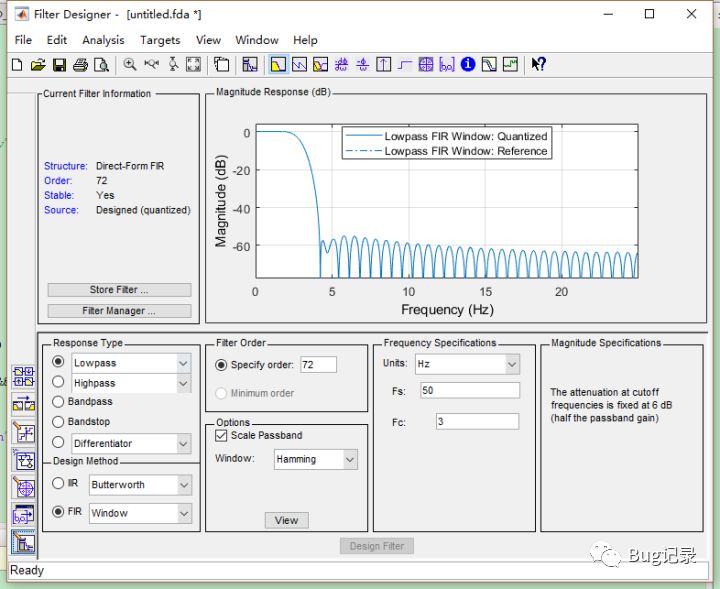

濾波器設(shè)置界面

這里選擇低通FIR,窗函數(shù)選常用的幾個(gè),這里選擇了漢明窗;濾波器階數(shù)選擇72,階數(shù)越高濾波效果越好,但資源占用越多;FS/FC(采樣率/截止頻率)為50:3,點(diǎn)擊Design Filter會(huì)顯示相應(yīng)的頻率響應(yīng)圖,由于FIR濾波器抽頭的特性,當(dāng)輸入的采樣率為50M時(shí),濾波器的截止頻率為3M,兩者之間保持比例關(guān)系。

濾波器數(shù)值表示

點(diǎn)擊如上圖紅框內(nèi)的圖標(biāo),將Filter arithmetic修改為Fixed-point,將濾波器的參數(shù)數(shù)值表示修改為定點(diǎn)數(shù)表示,方便FPGA處理,也只有這樣能生成coe文件。

濾波器生成coe文件

點(diǎn)擊上圖菜單欄的Target,然后生成coe文件。

在Vivado中IP Catalog中找到FIR IP核,

FIR IP核界面

在Filter Coefficient里面選擇使用COE FILE,文件選擇剛才生成的COE文件。

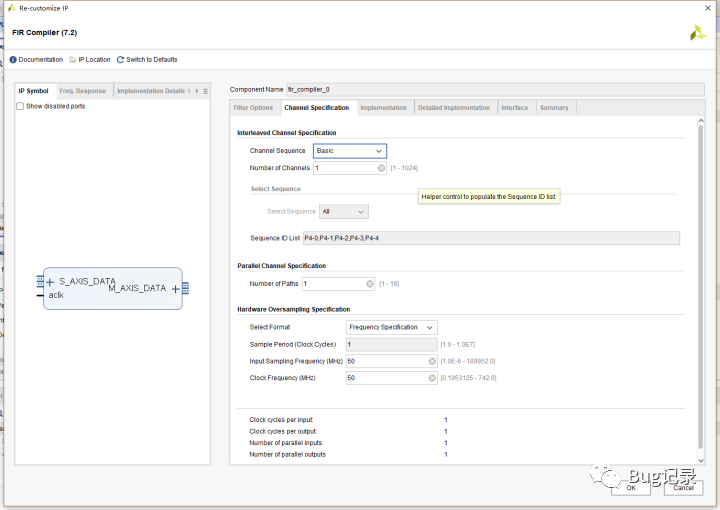

FIR IP核界面

在Channel Specification,設(shè)置輸入的采樣率為50M。

FIR IP核界面

Implementation里面,濾波器系數(shù)類型選擇有符號(hào)型,輸入數(shù)據(jù)也是有符號(hào)型,輸入數(shù)據(jù)位寬選擇2位,小數(shù)部分位數(shù)為0,GUI顯示出輸入數(shù)據(jù)位寬21位,這些數(shù)值后面有用。

一路默認(rèn),F(xiàn)IR IP核生成后,可以看到相關(guān)的端口定義。

fir_compiler_0 your_instance_name (

.aclk(aclk), // input wire aclk

.s_axis_data_tvalid(s_axis_data_tvalid), // input wire s_axis_data_tvalid

.s_axis_data_tready(s_axis_data_tready), // output wire s_axis_data_tready

.s_axis_data_tdata(s_axis_data_tdata), // input wire [7 : 0] s_axis_data_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata) // output wire [23 : 0] m_axis_data_tdata

);

可以看到,輸入數(shù)據(jù)位寬為8位,而我們?cè)贔IR GUI界面設(shè)置的是2位,為了不影響最終的輸入數(shù)據(jù),需要對(duì)輸入數(shù)據(jù)進(jìn)行符號(hào)位擴(kuò)展。

而輸出數(shù)據(jù)位寬有24位,但是FIR GUI界面顯示輸出數(shù)據(jù)位寬為21位,這說(shuō)明FIR的輸出數(shù)據(jù)也進(jìn)行了符號(hào)位擴(kuò)展,這里可以截取符號(hào)位。

相關(guān)的符號(hào)位擴(kuò)展和截取符號(hào)位可以見(jiàn)下代碼塊。

fir_compiler_0 fir_inst (

.aclk(clk_50m), // input wire aclk

.s_axis_data_tvalid(1'b1), // input wire s_axis_data_tvalid

.s_axis_data_tready(), // output wire s_axis_data_tready

.s_axis_data_tdata({{6{code_c[1]}},code_c}), // input wire [7 : 0] s_axis_data_tdata

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(fir_out) // output wire [23 : 0] m_axis_data_tdata 19-8

);

xbip_dsp48_macro_0 dsp_product_inst (

.CLK(clk_50m), // input wire CLK

.A(fir_out[19:8]), // input wire [11 : 0] A

.B(cos_o[13:2]), // input wire [11 : 0] B

.P(duc_data) // output wire [23 : 0] P

);

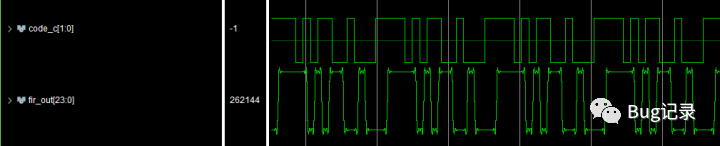

最后的濾波效果如圖:

濾波效果圖

濾波效果可以繼續(xù)調(diào)節(jié),這里可以看到圖里的濾波效果確實(shí)達(dá)到了,但可能效果不是那么好,實(shí)際的濾波參數(shù)需要仿真后看效果才可以確定。

FIR濾波相對(duì)于IIR濾波而言,沒(méi)有極點(diǎn)或者說(shuō)極點(diǎn)與零點(diǎn)抵消了,更加穩(wěn)定。但如果有時(shí)候我們想用IIR濾波器怎么辦呢,后續(xù)會(huì)談到如何實(shí)現(xiàn)IIR濾波器。

-

濾波器

+關(guān)注

關(guān)注

161文章

7862瀏覽量

178936 -

MATLAB仿真

+關(guān)注

關(guān)注

4文章

176瀏覽量

19998 -

GUI

+關(guān)注

關(guān)注

3文章

662瀏覽量

39893 -

FIR濾波

+關(guān)注

關(guān)注

0文章

6瀏覽量

9860 -

Vivado

+關(guān)注

關(guān)注

19文章

815瀏覽量

66892

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA的IP軟核使用技巧

IP核簡(jiǎn)介

使用quartusII fir ip核沒(méi)有輸出?

quartus ii 中fir數(shù)字濾波器IP核如何設(shè)置參數(shù)

Rapid IO IP核生成不了

quartus II 13.1調(diào)用FIR 這個(gè)IP核生成時(shí)一直卡著,怎么解決?

設(shè)計(jì)單位增益FIR IP核

關(guān)于fir compiler生成IP核后各項(xiàng)文件的具體說(shuō)明

altera FIR IP核使用過(guò)程中程序下載失敗的問(wèn)題

關(guān)于altera系列芯片FIR IP核在使用過(guò)程中的問(wèn)題

關(guān)于xilinx中fir濾波器IP核使用

基于FPGA的FIR濾波器IP仿真實(shí)例

基于IP核的FIR低通濾波器該怎么設(shè)計(jì)?

如何申請(qǐng)xilinx IP核的license

FIR IP核的基礎(chǔ)功能使用總結(jié)

FIR IP核的基礎(chǔ)功能使用總結(jié)

評(píng)論