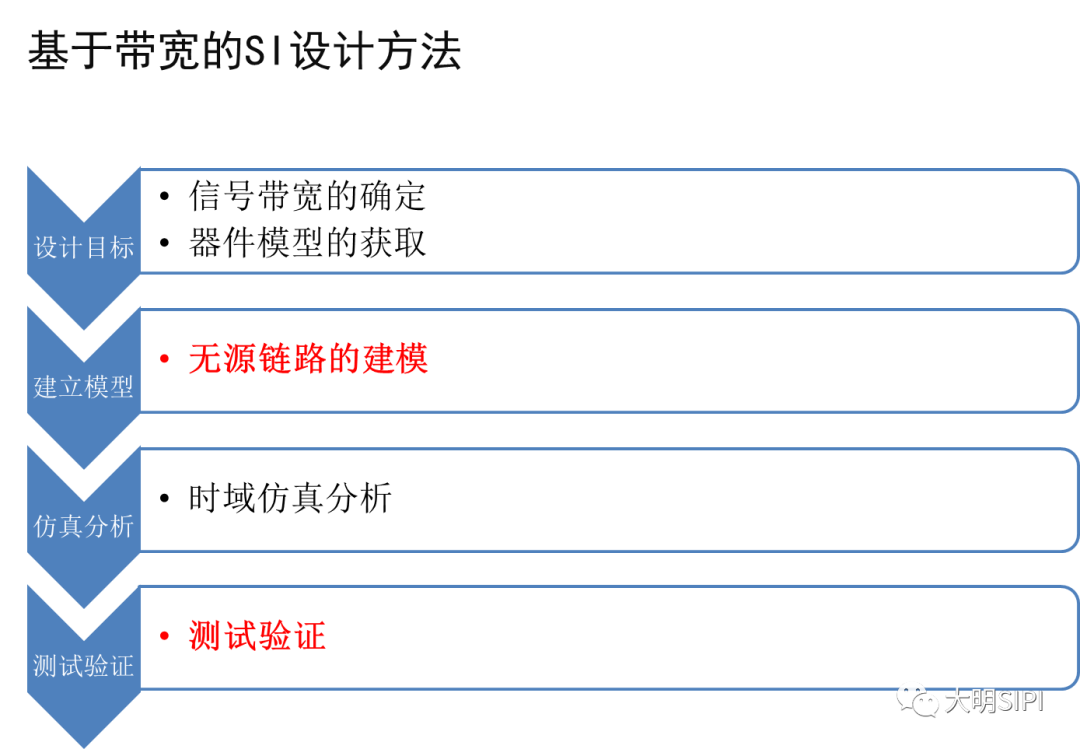

信號完整性分析的兩個維度--時域和頻域,而帶寬是連接時域和頻域的橋梁。同樣,帶寬也將信號的特性、傳輸通道、測試設備聯系在一起,可見帶寬是信號完整性分析中非常重要的一個概念。這一節就為大家介紹一下基于帶寬的信號完整性分析方法。

設計目標

我們面對一個SI分析項目,首先我們要通過對系統方案的了解以及datasheet的閱讀等渠道知道待分析的信號的特征:

- 是什么類型的接口,DDR還是Serdes?

- 數據速率有多高?

- 驅動器和接收器的電平標準?

弄明白這些問題,我們就大概知道信號的帶寬,就能夠對無源通道的設計提出具體明確的要求;我們也能驅動器和接收器的信號質量、時序的需求,也就能夠正確的判別時域仿真結果是否能夠滿足要求。

此外就是獲取芯片廠家提供的仿真模型,為時域的電路仿真做準備。一般來說廠家的模型無論是IBIS還是Spice模型都是和信號帶寬相匹配的,我們是可以放心使用的。

確立設計目標的過程其實也是為后續的頻域建模和時域的仿真做準備的過程。

建立模型

** 建模其實是一個頻域分析的過程。

**

對于無源鏈路需要工程師借助仿真軟件進行建模。

第一,建模的過程中必須保證模型的準確度,也就是模型必須能夠準確地反映了無源鏈路的真實特征。這就要求SI工程師能夠根據所設計的總線接口的特性選擇合適的軟件工具(2D、2.5D、3DEM工具)以及仿真建模方法(hfss建模端口的設置為lumped port還是wave port、設置在什么位置)。

第二,無源鏈路的性能要能夠滿足信號帶寬的要求。SI工程師需要通過對模型進行仿真優化使模型在信號的帶寬范圍內具有良好的損耗和反射性能,如果無源鏈路的性能不能滿足要求,工程師就需要對無源鏈路的材料或者結構進行調整以提高模型帶寬。

通常情況下,對于DDR等并行總線并沒有對無源通道的頻域特性給出特殊的要求,只給出了信號質量的要求(眼圖、過沖等)。因此這一步可以省略,直接進行時域電路仿真,如果信號質量不滿足要求再回過頭來優化傳輸通道以及芯片的OCD、ODT的配置。

對于Serdes接口,比如PCIe、Ethernet等接口的spec中都定義了插損(insert loss)、回損(return loss)等無源通道的指標。我們就需要根據這些指標對無源channel進行優化直到滿足Spec要求為止。

第一點就是保證模型的準確,保證使用這個模型進行仿真的結果和實際測試結果的偏差可控。第二點包含的意思就是我們需要通過對無源鏈路的優化來達到信號完整性最優的效果。

如果無源鏈路的模型帶寬太低會出現什么情況呢?

為了解釋這個問題,我們再來看一下帶寬的計算公式:BW= 0.35/Trise,

可以導出Trise = 0.35/BW。應用在互連線模型中,Trise就代表了互連線的本征上升時間。互連線的帶寬為1GHz,那么它能傳輸信號的最短上升時間就是350ps,這個350ps就是這條互連線的本征上升時間。驅動器輸出一個上升時間為Trise_drv的信號輸入到一條本征上升時間為Trise_interconnect的互連線,在接收器處接收到的信號上升時間為Trise_rev,則有如下關系:

不難看出,由于互連線的本征上升時間導致接收器接收到的信號上升時間Trise_rev相對于Trise_drv增大了,我們通常也說信號經過互連線傳輸之后發生了邊沿退化。如果互連線的帶寬太低,其本征上升時間就會比較長,那么接收器接收到的信號上升時間就會比較大,也就是說信號在傳輸過程中發生的邊沿退化就越嚴重。

仿真分析

通過前面兩個步驟我們已經準備好了驅動器和接收器的仿真模型,也對無源通道進行了建模,那么我們就可以搭建出完整的時域仿真電路。

時域仿真分析就是在無源模型上加入激勵源進行仿真從而觀測時域仿真結果。對于信號完整性仿真將芯片的有源模型(IBIS、Spice或者AMI模型)、傳輸路徑的無源模型搭建成仿真電路,在驅動器端添加激勵在接收器端直接觀測信號波形和眼圖,并對仿真結果進行分析。對于電源完整性則需要加入電流負載以及VRM模型仿真觀測負載端的電源噪聲。有些情況下無法獲取芯片的電流模型,此時就不能進行精確的電源完整性時域仿真,此時要求PI頻域仿真有足夠的裕量,時域仿真也是可以缺省的。

我們需要知道,時域仿真結果是SI的最終評判標準,時域仿真分析目的有兩個:

一是更加直觀地判斷信號、電源質量是否滿足要求;

二是確定芯片buffer選型、加重、均衡等各項參數配置為后續測試調試工作提供參考。

測試驗證

測試驗證是在產品生產完成后,在實際的系統中進行信號質量測試。測試驗證的目的有兩個,一是驗證接收端信號質量是否滿足要求;二是與前期的仿真結果進行對比進行差異分析,優化仿真建模方法。

測試儀器會對測試結果產生影響。對于高速信號的測試要選擇帶寬高、本征上升時間最夠小的探頭。

測試驗證要得到正確的測試結果需要注意以下事項:

- 根據信號帶寬選擇合適的示波器和探頭;

- 測試點位置選擇需靠近接收芯片管腳,往往選擇PCB上的過孔。但我們選擇的測試點并不是芯片實際的接收端,因此測試波形會受到封裝內部布線的影響。此時需要使用“去嵌入”技術消除封裝內部布線的影響。

**基于帶寬的SI設計流程

**

基于面的介紹,我們這里對信號完整性分析設計流程進行歸納總結,整個過程大體可分為前期準備(確定設計目標、獲取模型)、無源鏈路建模、時域仿真分析、測試驗證四個環節。其中前期準備是基礎、無源鏈路建模和時域仿真分析是核心、并通過測試驗證形成閉環。后續篇幅會針對高速并行總線、高速串行總線的信號完整性、以及電源完整性設計詳細介紹設計流程。

-

驅動器

+關注

關注

53文章

8272瀏覽量

147074 -

接收器

+關注

關注

14文章

2481瀏覽量

72219 -

信號完整性

+關注

關注

68文章

1417瀏覽量

95636 -

VRM

+關注

關注

0文章

30瀏覽量

12720 -

PCB

+關注

關注

1文章

1825瀏覽量

13204

發布評論請先 登錄

相關推薦

高速電路信號完整性分析與設計—高速信號完整性的基本理論

什么是信號完整性!信號完整性分析

介紹一下基于帶寬的信號完整性分析方法

介紹一下基于帶寬的信號完整性分析方法

評論