引言過去18個月,關于半導體制造以及美國國內芯片制造方面落后的充分擔憂,已經有了大量的書面報道和討論。

針對這一問題,美國政府頒布了《CHIPS和科學法案》。這項法案提供的資金旨在推動美國國內芯片制造的更快發展。

雖然,這一切的初衷都很好,但一旦這些先進的芯片被制造出來,它們將何去何從?正如人們所說,“光有芯片也沒用”。

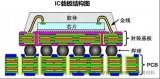

這些芯片需要高階PWB來支持這些封裝。PWB和IC載板是這些芯片、微處理器、電容器、存儲器、邏輯等安裝和互連的物理平臺。

如果沒有高可靠性、高密度的平臺,芯片將無處可去。這正是必須采用關鍵技術、工藝和材料來支持芯片生產和高階封裝的原因。

定位和材料選擇

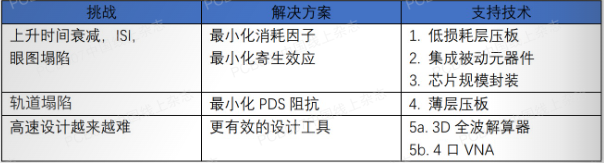

HDI板的特點是特征更小和對準更嚴苛。為此,特征補償和縮放比普通電路板更重要。HDI板也用于高頻應用,因此,滿足這些需求為工程設計、定位部門帶來了新的挑戰。表1顯示了工程設計高頻板的三大挑戰。

表1:高速HDI板面臨三大挑戰

材料選擇同樣重要,特別是因為無鉛組裝溫度及其對層壓板分層和可靠性的影響。重要的新功能包括:

使用“共面波導”和共面帶狀線模型的高頻板的阻抗計算和堆疊。

新型酚醛環氧樹脂和無鹵FR-4的特性和放大、特征補償。

能夠添加局部基準以對準激光鉆孔CCD相機。

根據直徑、深度和材料類型存儲激光鉆孔參數的系統。

塞孔的特征,以確定埋孔的放置是否會產生問題。

從材料的角度來看,低Dk和低損耗層壓材料是首選的層壓材料。需要滿足信號完整性和阻抗匹配要求。最小化高頻信號損耗對于支持高階封裝的IC載板技術至關重要。這使人們能夠更好地理解導通孔形成和去鉆污、去金屬化。

小孔、小孔微導通孔形成

雖然HDI通常與激光鉆孔相關,但也可以通過機械鉆孔和化學蝕刻形成小盲孔。重要的是確保每個板都能接收到正確的微導通孔鉆孔參數。理想情況下,形成的導通孔形狀時在通孔頂部有更寬的開口,向下逐漸變細。

導通孔的形狀對于實現均勻鍍銅至關重要。電鍍操作的流體動力學要求不斷補充關鍵電鍍添加劑,以確保更換新鮮電解液以減少濃度極化。隨著濃度極化,擴散層會缺少銅離子和其他添加劑。

注意,盲孔的直徑在頂部略窄。此外,整體導通孔的質量受到影響,是過度去除粘合劑材料。在這種情況下,電解液到盲孔的層流被破壞,進一步影響均勻電鍍。

需要考慮的其他重要因素和條件包括:

確保外層的層壓厚度一致,否則將嚴重影響激光鉆孔。

注意能級,以免在盲孔底部產生分層或環氧樹脂殘留物。仔細選擇要激光鉆孔的電介質(可激光鉆孔的半固化片)。

檢查激光鉆孔設備的景深,以驗證可以激光鉆孔的最厚板材。

制造商必須投資最新的對準和導通孔形成設備。

可能存在孔和導通孔的定位精度問題

可用于預測材料移動的系統

去鉆污和金屬化

從純材料的角度來看,這些高性能樹脂更難去鉆污和金屬化。因為模量更高,材料更脆。這些材料也更耐化學工藝,包括堿性高錳酸鹽化學工藝。人們不能依賴常見的具有較低Tg材料樹脂的高表面積和蜂巢狀結構。

然而,為了確保清除鉆屑和其他碎屑,堿性高錳酸鹽工藝還必須活化樹脂和玻纖,以確保后續鍍銅的附著力。松散的碎屑和光滑的樹脂表面將無法提供足夠的附著力,因而無法承受熱偏移和機械沖擊。

精細走線成像、顯影

光刻法是高階封裝和IC載板生產的基石。激光直接成像現在是生產高密度與超高密度載板的必備技術。在不斷突破超高密度技術極限的過程中,傳統的接觸式印制技術顯現出了不足之處,于是促進了激光直接成像(laser direct imaging,簡稱LDI)技術的發展與應用。

與接觸式印制技術相比,LDI系統有諸多優勢。例如使用LDI技術生產的PCB具有更小的對準容差,直接通過CAD系統印制圖形也不再需要使用底片。

而使用接觸式印制技術時,底片或面板的尺寸變化會引起對準錯誤。尺寸之所以發生變化是因為掩模和面板材料(如FR-4)尺寸會隨著溫度及濕度(在一般的工廠環境下分別控制在±2°C和±5%RH)的變化而變化。

下方列出了制造電路時的5個步驟:

表面制備

抗蝕劑貼合

曝光

顯影

蝕刻

先來看曝光工藝。

在使用LED、LDI技術時,總是能聽到“焦距”(depth of focus,簡稱DOF)這個術語。設置正確的DOF是實現最佳分辨率的關鍵。反之,如果DOF設置不當,就會導致線寬或線距增加、斷開或出現走線扭曲缺陷。所以說一定要確保DOF準確無誤。

另一個必不可少的步驟是找到成像工藝中的應力點。可以使用精細走線螺旋或精細走線和細間距等測試圖形找到應力點。其中包括標有刻度的精細走線和線距,例如100、75、50和25微米的精細走線和線距。這種評估還有助于深入了解其他會影響成像分辨率的工藝參數。

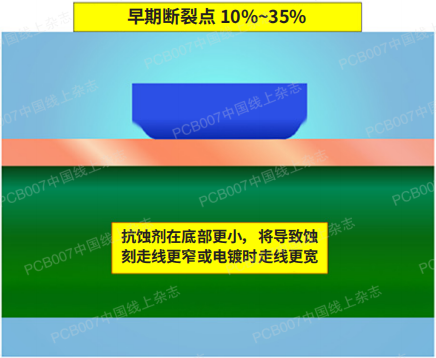

例如較高的曝光能量會增強抗蝕劑的附著力。此外,銅箔類型(ED、RTF、RA)、表面制備方式和顯影點提前都會影響成像的分辨率。千萬不要低估顯影點的威力。圖1示意圖中展示了顯影點提前。

圖1:顯影過程中早期形成的斷裂點(來源:Tim Blair,Tim Blair LLC)

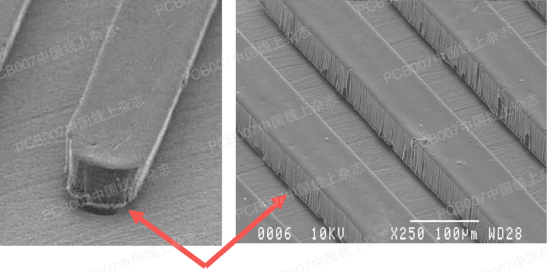

即便使用了理想的曝光能量和表面制備方式,抗蝕劑寬度減少的風險也是相當高的。圖2顯示了此類問題的實際掃描電子顯微圖。顯影點提前會導致顯影過度和側蝕問題,而這種情況會進一步導致內層走線寬度變窄。

圖2:早期形成斷裂點會導致顯影過度(來源:Tim Blair,Tim Blair LLC)

蝕刻

可以說顯影和蝕刻是相通的。萬事萬物皆有聯系,這是排除故障時的基本規則。值得注意的是,無論是使用堿性蝕刻液還是酸性蝕刻液,蝕刻都是各向同性的。這就意味著Z軸的銅被蝕刻去除后,側面的銅也會被橫向去除。

一定要嚴格控制蝕刻的關鍵工藝參數。堿性氨水蝕刻技術可用于蝕刻內層和外層。但控制精細走線蝕刻工藝的關鍵參數是堿性蝕刻溶液的pH值。將溶液的pH值保持在8.0~8.2之間有助于降低橫向蝕刻和側蝕。當然,溶液的比重也很重要。將溶液比重保持在上限水平附近有助于減輕橫向蝕刻。

另外,像氯化銅這樣的酸性蝕刻劑只能用于內層。這種蝕刻劑與金屬抗蝕劑不兼容。但與堿性蝕刻技術相比,酸性蝕刻具備更理想的蝕刻因數和側蝕。有報告稱,將酸性蝕刻劑控制在很低的游離酸常態下可以提高蝕刻系數。

還有其他研究對比了不同蝕刻蝕和不同光致抗蝕劑厚度下的蝕刻因數。T.Yamamot等人的早期研究證明了蝕刻通道加寬、抗蝕劑變薄之后產生的有利影響。以上引用的研究也證實了:與堿性蝕刻劑相比,銅蝕刻劑在側蝕方面具備的優勢。

減成法蝕刻加工出的電路密度是有極限的。這是眾所周知的常識。蝕刻劑去除目標位置銅的過程越長,就越有可能出現側蝕和走線寬度變窄。改用半加成型工藝并減小銅箔厚度,或使用介質薄膜可大幅提高蝕刻因數。

審核編輯:湯梓紅

-

芯片

+關注

關注

456文章

51192瀏覽量

427305 -

電容器

+關注

關注

64文章

6256瀏覽量

100242 -

封裝

+關注

關注

127文章

7997瀏覽量

143413 -

HDI板

+關注

關注

2文章

55瀏覽量

15666 -

IC載板

+關注

關注

5文章

54瀏覽量

15905

原文標題:生產高階封裝使用IC載板的初步挑戰

文章出處:【微信號:actSMTC,微信公眾號:actSMTC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

邁開3D IC量產腳步 半導體廠猛攻覆晶封裝

IC制造商克服精度挑戰的技術有哪些?

26億紅板5G高階HDI和IC載板項目簽約江西

UHDI及高階封裝技術對檢測系統的挑戰

生產高階封裝使用IC載板的初步挑戰

生產高階封裝使用IC載板的初步挑戰

評論