1、簡介

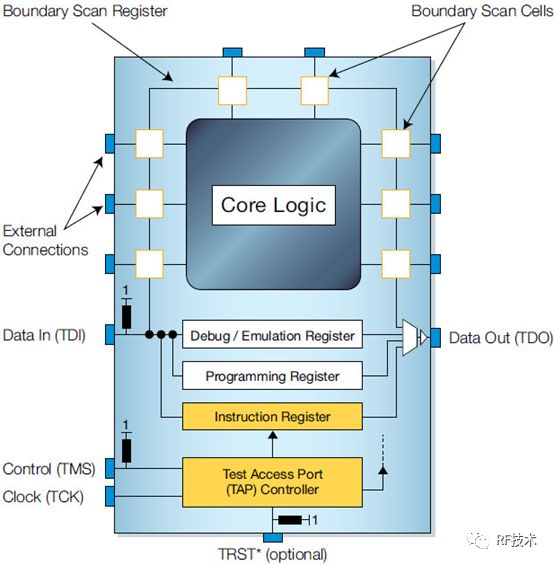

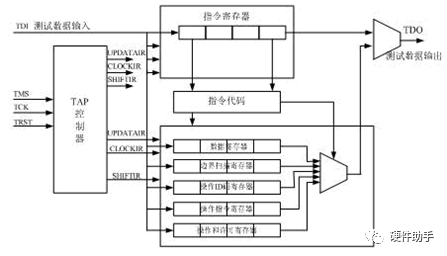

JTAG的英文名稱為Joint Test Action Group,中文名字叫做聯合測試工作組,是一種國際標準測試協議(IEEE 1149.1兼容),主要用于芯片內部測試及對系統進行在線仿真、調試,它在芯片內部封裝了專門的測試電路 TAP ( Test Access Port ,測試訪問口),通過專用的JTAG測試工具對芯片進行測試。現在多數的高級器件都支持JTAG協議,如以以ARM為核心的手機CPU、DSP、FPGA等芯片都會帶JTAG接口。標準的JTAG接口是4線:TMS、TCK、TDI、TDO,分別為模式選擇、時鐘、數據輸入和數據輸出線。

?? ? ? ? ? ? ? ? ? ? ??

?? ? ? ? ? ? ? ? ? ? ??

2、接口

JTAG技術是一種嵌入式調試技術,JTAG最初是用來對芯片進行測試的,JTAG的基本原理是在器件內部定義一個TAP(Test Access Port;測試訪問口)通過專用的JTAG測試工具對內部節點進行測試。JTAG測試允許多個器件通過JTAG接口串聯在一起,形成一個JTAG鏈,能實現對各個器件分別測試。如今,JTAG接口還常用于實現ISP(In-SystemProgrammer,在系統編程),對FLASH等器件進行編程。

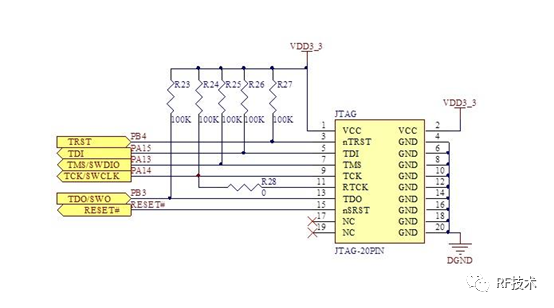

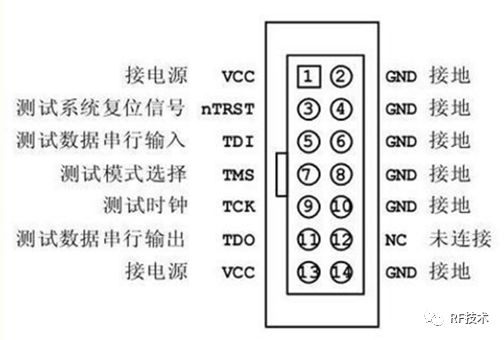

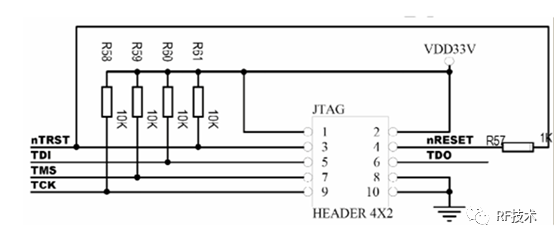

JTAG調試接口有TMS、TCK、TDI、TDO四根調試信號,可選信號腳為:TRST、RESET復位信號和RTCK(同步時鐘)。

TRST:JTAG復位,連接到目標CPU的nTRST引腳,用于復位CPU調試接口的TAP控制器;目標板上應將此腳上拉到高電位,避免意外復位;

3、JTAG功能

JTAG是最基本的通訊協議之一,大家可以理解為與RX、TX以及USB的道理一樣,只是一種通訊手段,但與RX TX以及USB有很重大的不同,那就是這個JTAG協議是最底層的,說的通俗一點,一般來說,手機里邊,CPU是老大,妥妥的吧?但在JTAG面前,他就變得不那么回事了,JTAG協議就是用來控制CPU的,在JTAG面前CPU變成嘍啰了。一般的協議是求著CPU讀寫字庫的程序,但JTAG可以讀寫CPU的程序,命令讓CPU啥活都干,擒賊先擒王,JTAG就是屠龍刀。

所有的手機CPU都支持JTAG協議,也必須支持JTAG協議,因為CPU里邊的數據只有通過JTAG功能才能寫入,在內部數據錯亂的時候或者其他部分重要數據錯亂的時候,CPU可能就不理會RX TX或者USB了,在這個時候,用JTAG協議功能,強制手機CPU乖乖的干活。

說的簡單一點,讓大家理解,就是在CPU由于軟件原因不聯機的時候,JTAG是唯一能夠恢復這部分軟件的工具。JTAG能夠指揮CPU干任何事,在JTAG面前CPU只是一個馬仔。

A.下載器,即燒寫軟件到FLASH里;

B.用于調試程序,通過JTA接口可以調試電路板上的程序,跟醫生的聽診器似的,可探聽芯片內部小心思;

C.邊界掃描,可以訪問芯片內部的信號邏輯狀態,還有芯片引腳的狀態等等。

4、JTAG的引腳定義

a)Test Clock Input (TCK)------測試時鐘輸入,TCK在IEEE1149.1標準里是強制要求的;

b)Test Mode Selection Input (TMS) ----測試模式選擇,TMS用來設置JTAG口處于某種特定的測試模式,TMS信號在TCK的上升沿有效,TMS在IEEE1149.1標準里也是強制要求的;

c)Test Data Input (TDI)------測試數據輸入,所有的數據都是通過TDI接口串行輸入的,TDI在IEEE1149.1標準里是強制要求的;

d)Test Data Output (TDO)------測試數據輸出,所有的數據都是通過TDO接口串行輸出的,TDO在IEEE1149.1標準里是強制要求的;

e)Test Reset Input (TRST)------測試復位,輸入引腳,低電平有效,這個信號接口在IEEE 1149.1標準里是可選的,并不是強制要求的。

f)(VTREF) -----參考電壓信號,這個引腳一般直接連接VCC。用于檢查目標板是否供電,直接與目標板VDD聯,并不向外輸出電壓,這個引腳也是強制要求的;

g)目標板參考電壓信號。Return Test Clock (RTCK) ----由芯片返回給仿真器的時鐘信號,用來同步TCK信號的產生,不使用時直接接地,不是必選的;

h)System Reset ( nSRST)------與目標板上的系統復位信號相連,可以直接對目標系統復位,同時可以檢測目標系統的復位情況,為了防止誤觸發應在目標端加上適當的上拉電阻;

i)GND------公共地信號。

雖然TRST、nSRST是可選的信號;但一般都建議接上,使得仿真器能夠在連接器件前對器件進行復位,以獲得較理想的初始狀態,便于后續仿真。

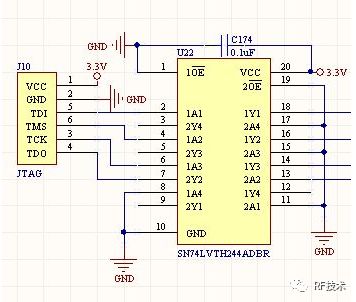

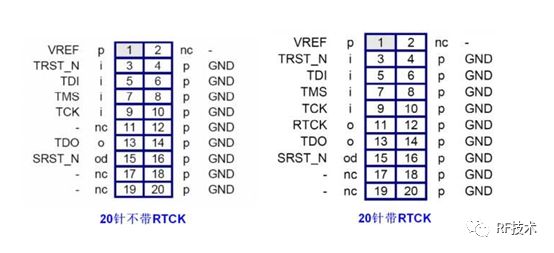

由于JTAG在實驗室調試的時候經常使用排線連接,為了增強抗干擾能力,在每條信號線間加上地線就出現了這種20針的接口。但事實上,RTCK、USERIN、USER OUT一般都不使用,于是還有一種14針的接口。對于實際開發應用來說,由于實驗室電源穩定,電磁環境較好,干擾不大。

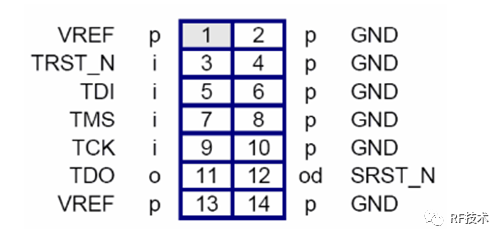

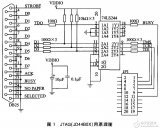

5、20、14、10 pin JTAG的引腳關系

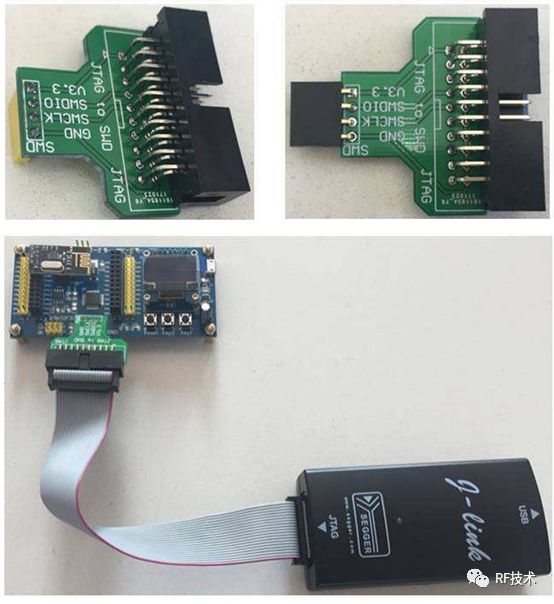

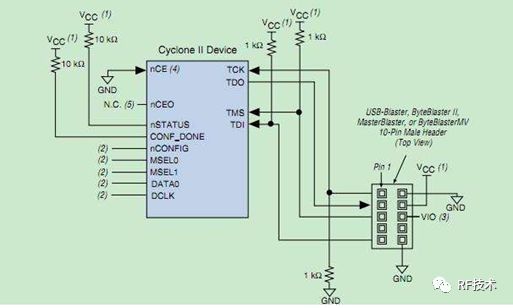

值得注意的是,不同的IC公司會自己定義自家產品專屬的Jtag頭,來下載或調試程序。嵌入式系統中常用的20、14、10pin JTAG的信號排列如下:

需要說明的是,上述JTAG管腳的名稱是對IC而言的。例如TDI腳,表示該腳應該與IC上的TDI腳相連,而不是表示數據從該腳進入download cable。實際上10針的只需要接4根線,4號是自連回路,不需要接,1,2接的都是1管腳,而8,10接的是GND,也可以不接。

責任編輯:彭菁

-

JTAG

+關注

關注

6文章

401瀏覽量

71840 -

編程

+關注

關注

88文章

3637瀏覽量

93981 -

調試技術

+關注

關注

0文章

7瀏覽量

6652

原文標題:JTAG簡介

文章出處:【微信號:ZGDZGCS,微信公眾號:電子萬花筒】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

硬件接口協議技術:JTAG內部狀態機——TAP控制器

如何實現對JTAG口的控制。。。。

【轉】JLINK與JTAG的區別

JTAG基本原理

JTAG的基本原理(共31頁pdf課件下載)

JTAG口的基本原理是什么?四核芯片S698PM的連接方法和注意事項是什么?

線性電源的基本原理是什么

無線充電的基本原理是什么

JTAG的基本原理與測試總結

ARM JTAG調試的基本原理

JTAG基本原理及仿真器性能比較

jtag的基本原理與調試原理

JTAG的基本原理

JTAG的基本原理

評論