上升沿檢測電路

01

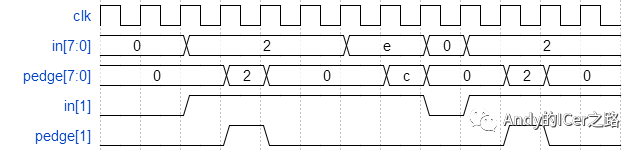

題目:對于8位向量中的每個(gè)位,檢測輸入信號何時(shí)從一個(gè)時(shí)鐘周期的0變?yōu)橄乱粋€(gè)時(shí)鐘周期的1(類似于上升沿檢測)。應(yīng)在從0到1的跳變發(fā)生后的周期內(nèi)設(shè)置輸出位。

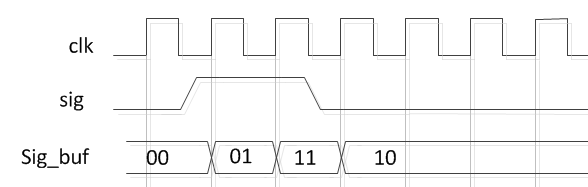

以下為例子, 為了清楚起見,分別顯示了in [1]和pedge [1]。

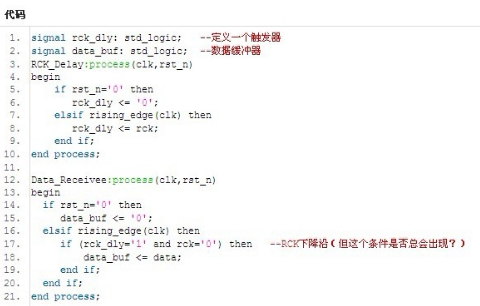

module top_module(

input clk,

input [7:0] in,

output reg [7:0] pedge);

reg [7:0] d_last;

always @(posedge clk) begin

d_last <= in;

pedge <= in & ~d_last; // A positive edge occurred if input was 0 and is now 1.

end

endmodule

第九行 d_last <= in ; 是記錄信號in上一個(gè)cycle的狀態(tài);

第十行 pedge <= in & ~d_last; 檢測上升沿,簡答來說就是檢測input由0變1。

雙邊沿檢測電路

02

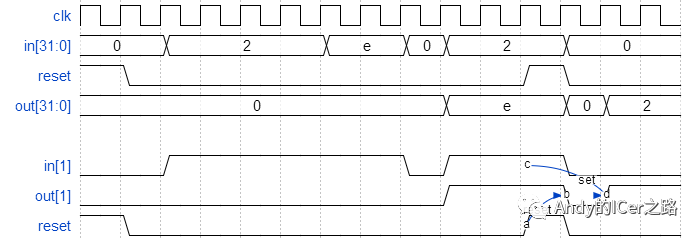

題目:對于8位向量中的每個(gè)位,檢測輸入信號何時(shí)從一個(gè)時(shí)鐘周期更改為下一個(gè)時(shí)鐘周期(檢測任何邊沿)。應(yīng)在從0到1的跳變發(fā)生后的周期內(nèi)設(shè)置輸出位。

module top_module (

input clk,

input [7:0] in,

output [7:0] anyedge

);

reg [7:0] d_old;

always@(posedge clk)begin

d_old <= in;

anyedge <= d_old^in;

end

endmodule

第八行 d_old <= in ; 是記錄信號in上一個(gè)cycle的狀態(tài);

第九行 anyedge <= d_old^ in ; 即現(xiàn)在的信號in與上一個(gè)狀態(tài)不一樣的話,輸出1(異或是兩個(gè)信號不一樣置1),這樣該電路就可以雙邊沿檢測。

-

檢測電路

+關(guān)注

關(guān)注

13文章

308瀏覽量

58268 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110396 -

狀態(tài)機(jī)

+關(guān)注

關(guān)注

2文章

492瀏覽量

27649 -

時(shí)鐘域

+關(guān)注

關(guān)注

0文章

52瀏覽量

9574

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA設(shè)計(jì)中的邊沿檢測問題

fpga應(yīng)用篇(二):邊沿檢測

微弱光檢測的電路設(shè)計(jì)

FPGA學(xué)習(xí)系列:12. 邊沿檢測設(shè)計(jì)

Verilog系統(tǒng)函數(shù)和邊沿檢測

如何設(shè)計(jì)邊沿采樣的觸發(fā)器呢?

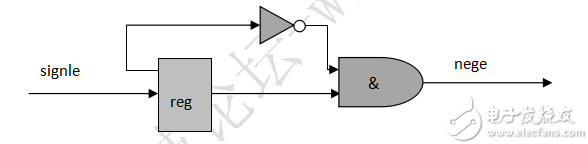

Verilog實(shí)現(xiàn)邊沿檢測的原理

邊沿檢測電路設(shè)計(jì)

邊沿檢測電路設(shè)計(jì)

評論