最近有群友問我system Verilog 和C怎么交互,在網(wǎng)上搜了一圈發(fā)現(xiàn)資料比較少,今天這里就和大家講講system Verilog 和C的交互。話不多說直接上干活。

第一種 Verilog 通過PLI調(diào)用C函數(shù)。

PLI全稱 Program Language Interface,程序員可以通過PLI在verilog中調(diào)用C函數(shù),這種訪問是雙向的。這些用戶定義的系統(tǒng)任務(wù)和函數(shù)的名稱必須以美元符號(hào)"" 開頭。大家用得比較多的PLI函數(shù)有display,$finish等。

用戶可以自定義PLI函數(shù),下面是一個(gè)簡(jiǎn)單的PLI應(yīng)用例子。

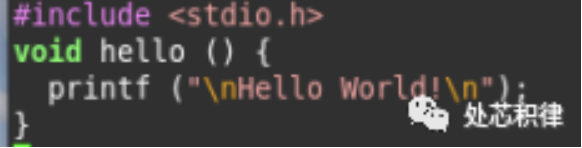

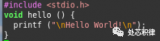

以下是一段C代碼

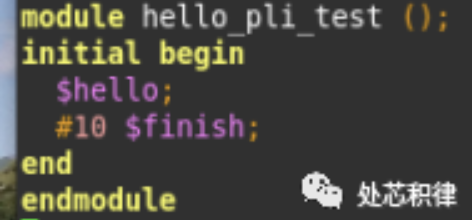

下面是一段調(diào)用C的verilog的代碼

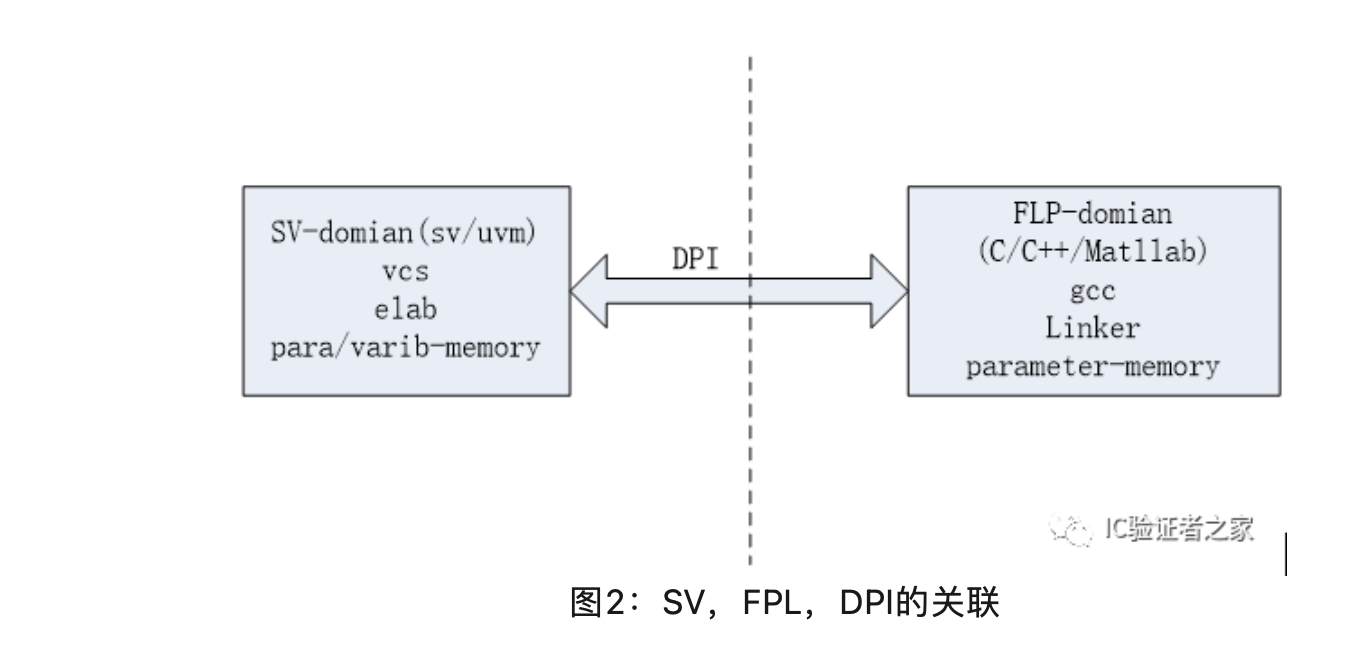

第二種 System Verilog 通過DPI和C進(jìn)行交互

為了更加簡(jiǎn)潔的連接C,system verilog 引入了DPI(Direct Programming Interface)。只要使用import聲明和使用,導(dǎo)入一個(gè)C子程序,就可以像調(diào)用System Verilog中的子程序一樣來(lái)調(diào)用它。相反,如果C想用system verilog里面的函數(shù)用export 聲明即可。下面是一個(gè)簡(jiǎn)單的例子。

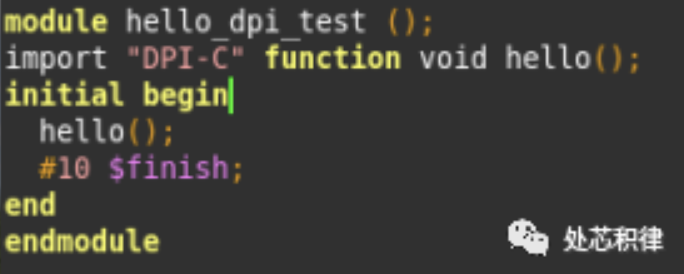

在System Verilog 里面調(diào)用C函數(shù)

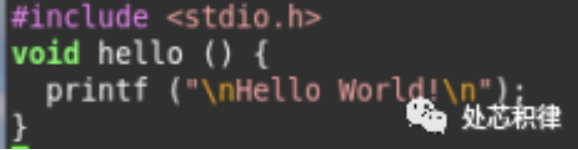

C代碼和上面一樣

System Verilog的代碼如下

在C中調(diào)用System Verilog 函數(shù)

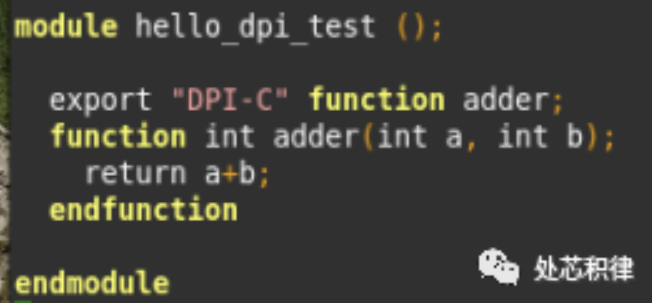

System Verilog 的代碼如下

C代碼如下

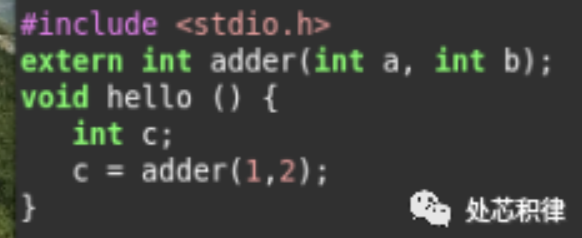

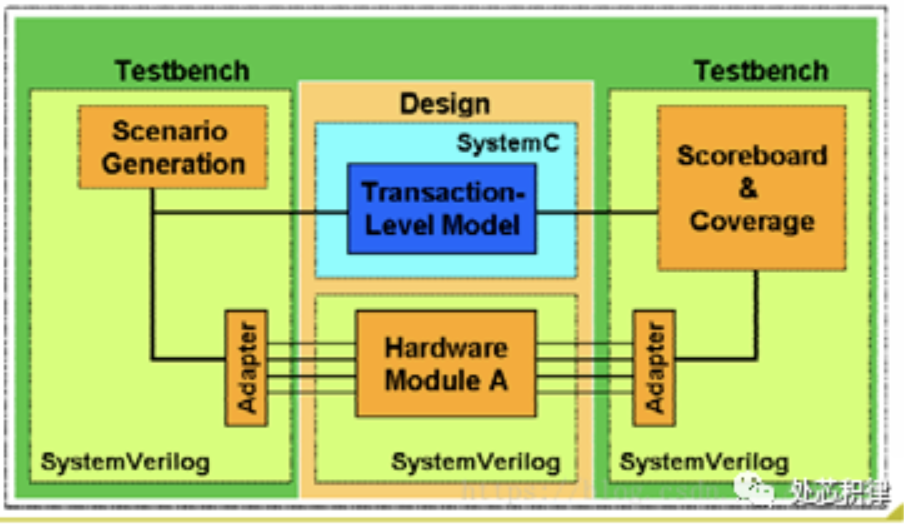

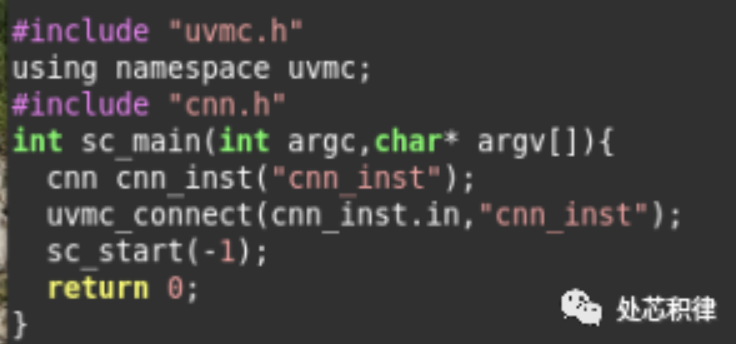

第三中 System Verilog 和C的交互方式是通過TLM1.0或者TLM2.0 進(jìn)行交互。

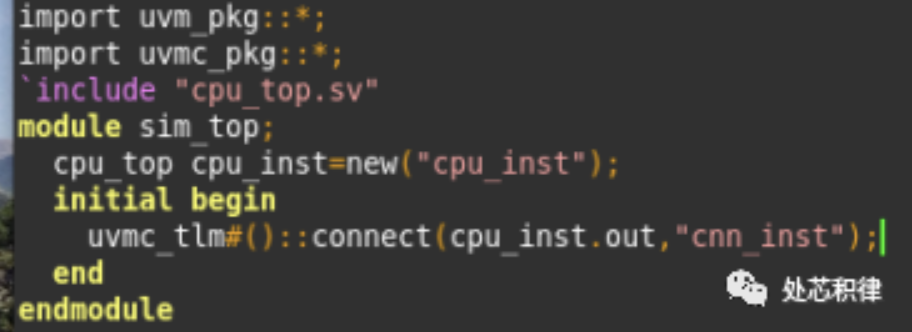

這種交互方式主要應(yīng)用在System Verilog 和systemc 上。對(duì)于systemc一般人用得比較少,所以這類交互也比較少用。下面是一個(gè)簡(jiǎn)單的例子

Systemc 的編碼,其中cnn_inst的接口in是tlm1/tlm2類型port。

System verilog 的編碼,cpu_inst.out 為tlm1/tlm2類型的port。

第四種交互方式,通過CPU執(zhí)行C代碼,從而實(shí)現(xiàn)verilog 和C的交互。

C代碼通過工具鏈編譯成CPU可以執(zhí)行的匯編指令,再將匯編指令轉(zhuǎn)成對(duì)應(yīng)的指令代碼,然后通過CPU讀取指令代碼產(chǎn)生激勵(lì),實(shí)現(xiàn)C代碼所描述的功能。

以上是Verilog/System Verilog 和C的幾種交互模式,小伙伴們學(xué)會(huì)了嗎?

-

編碼器

+關(guān)注

關(guān)注

45文章

3667瀏覽量

135235 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110390 -

TLM

+關(guān)注

關(guān)注

1文章

32瀏覽量

24780 -

DPI

+關(guān)注

關(guān)注

0文章

37瀏覽量

11542

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

System Verilog常見問題及語(yǔ)言參考手冊(cè)規(guī)范

System Verilog問題和語(yǔ)言參考手冊(cè)規(guī)范

Verilog Digital System Design

VHDL,Verilog,System verilog比較

verilog是什么_verilog的用途和特征是什么

淺談Verilog-95、Verilog-2001與System Verilog之間的區(qū)別

System Verilog與verilog的對(duì)比

學(xué)會(huì)這些System Verilog方法,芯片驗(yàn)證入門沒問題

淺談System Verilog的DPI機(jī)制

談?wù)?/b>system Verilog 和C的交互

談?wù)刅erilog/System Verilog和C的幾種交互模式

談?wù)刅erilog/System Verilog和C的幾種交互模式

評(píng)論