前期我們從工作電壓,頻率,容量等產品規格,prefetch/burst length內部訪問方式的角度介紹了DDR3/DDR4/LPDDR4(X)的一些主要feature及區別。

【芯科普】從DDR3到LPDDR4(X),看產品細分差異優化發展

話題一

DDR3/DDR4/LPDDR4接口差異

今天我們從接口實現上看一下其差異,通過上一篇對于其三者區別的分析,可以看到三者的不同點從外部來看主要是通過不同的接口來實現。因此我們今天具體來從接口實現上來分析之間的差異。

1DDR3

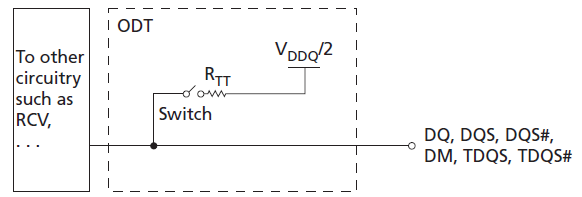

DDR3的接口為SSTL(Stub Series Terminated Logic),匹配電阻上拉到VDDQ/2。

2DDR4

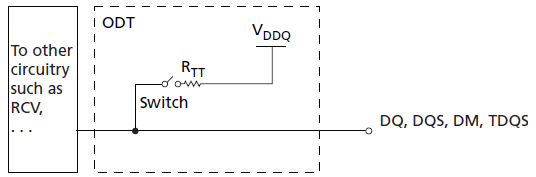

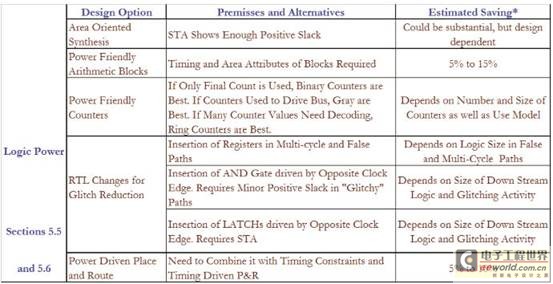

DDR4匹配電阻上拉到VDDQ,可稱為POD(Pseudo Open Drain),用以減少IO電流消耗。對DDR4的POD來說,drive High(logic level ”1” )幾乎不耗電,可以用這特點搭配DBI(Data bus inversion)來降低功耗。當一個字節里的 ”0” bits比 ”1” bits多時,可以使能DBI,將整個字節的“0”和“1”反轉,這樣 “1” bits就會比“0” bits多,達到省電的效果。

3LPDDR4

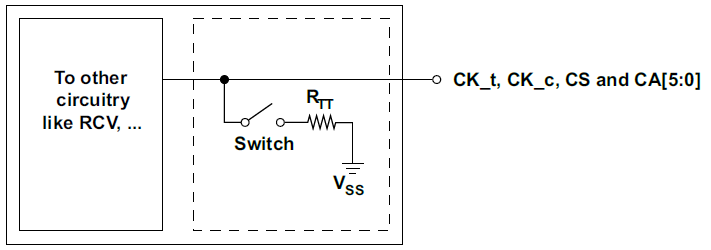

LPDDR4的匹配電阻下拉到VSSQ, 稱為LVSTL(Low Voltage Swing Terminated Logic), 這樣可以更省電,LPDDR4靠NMOS 晶體管pull up,也可以工作在更低的電壓。

從上述DDR3到LPDDR4接口設計的演變的呈現,其目的主要是是為了滿足產品對低功耗的要求,因此其工作電壓也變得越來越低。

除此之外,對速度的要求需要越來越高的頻率來實現,這對信號質量要求就會更高,因此用ODT(On Die Termination) 來實現impedance matching,減少反射波的影響,優化數據眼(Data eye),在高速信號的傳輸中提高信號質量。DDR2的termination開始放在芯片上,之后output driver可與ODT的電路共用,靠電路控制實現Output driver與ODT的電路切換。信號質量有多方面因素的影響,DDRPHY上的skew及Jitter,cross talk,inter symbol interface等等。

話題二

什么是DQS信號?

DDR(Double Data Rate) 在訪問時接口上的DQS信號是源同步時鐘,在接收端使用DQS來讀出相應的數據DQ, 上升沿和下降沿都能讀寫,稱為Double data rate。

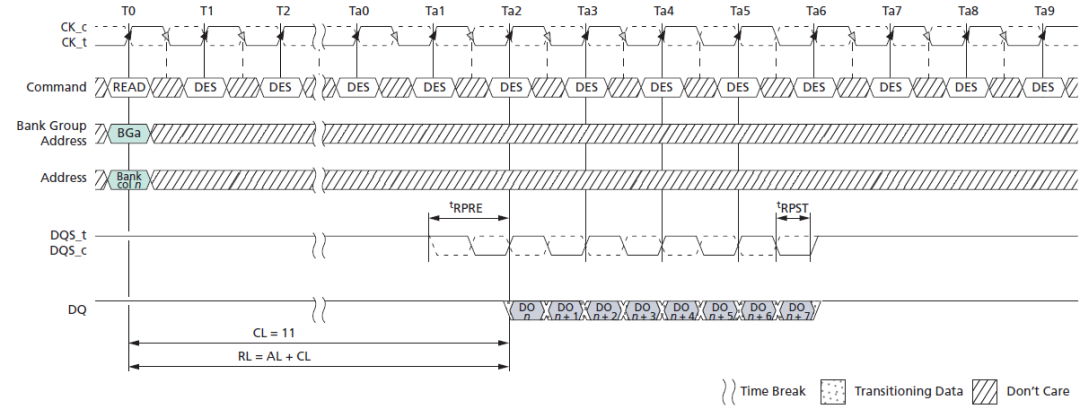

讀

1在讀的階段

DQS由DRAM產生并發送給DDRPHY的控制器,DQS和DQ都和CLK的邊沿對齊(edge aligned),然后將數據傳給DDRPHY。

依時序從DRAM讀出數據傳給DDRPHY,在DDRPHY的接收器(Receiver)接收到信號后,會將DQS delay 90°,delay后的DQS邊沿和DQ的中心對齊(center-aligned),最后用DQS的上升沿與下降沿來采樣數據。

寫

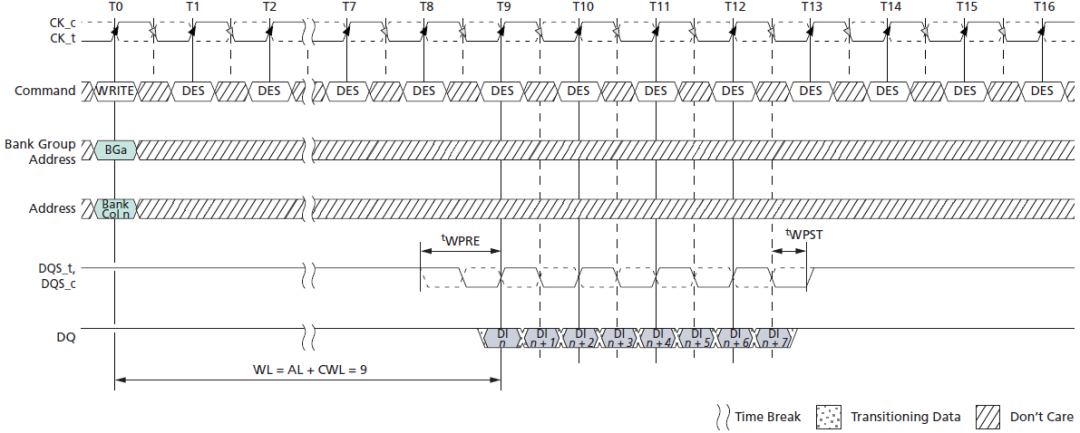

在寫的階段

DQS由DDRPHY控制器產生并發送給DRAM,DQS和CLK的邊沿對齊(edge aligned),而DQ和CLK是中心對齊的(edge-aligned),DRAM就可以直接用DQS的上升沿和下降沿來采樣數據。

這期我們簡單介紹了DDR接口的一些實現方式,主要區別以及高速信號的基本讀寫操作。東芯半導體的DRAM產品都是符合國際接口規范的標品,替換無壓力。具體的規格如下,歡迎關注并咨詢。

·DDR3(L)

| 密度/Density | 1Gb/2Gb/4Gb |

| 電壓/Voltage | 1.5V/1.35V |

| 溫度/Temperature | 0℃/-40℃~95℃ |

| 線寬/Bus Width | x8/x16 |

| 速度/Speed | 800Mhz/933Mhz |

| 封裝/Package | 78/96ball FBGA |

·LPDDR

| 密度/Density |

LPDDR1 128Mb/256Mb/512Mb/1Gb/2Gb LPDDR2 1Gb/2Gb/4Gb LPDDR4X 1Gb/2Gb |

| 電壓/Voltage |

LPDDR1 1.8V LPDDR2 1.8V/1.2V LPDDR4X 1.1V/0.6V |

| 溫度/Temperature | -40℃~85℃ |

| 線寬/Bus Width |

LPDDR1 x16/x32 LPDDR2 x16/x32 LPDDR4X x16/x32 |

| 速度/Speed |

LPDDR1 166Mhz/200MHz LPDDR2 400MHz/533MHz LPDDR4X 1600Mhz/1866Mhz/2133MHz |

| 封裝/Package |

LPDDR1 60/90ball FBGA/KGD LPDDR2 134ball FBGA LPDDR4X 200ball FBGA |

東芯,為日益發展的存儲需求提供高效可靠的解決方案。

關于東芯

東芯半導體以卓越的MEMORY設計技術,專業的技術服務實力,通過國內外技術引進和合作,致力打造成為中國本土優秀的具有自主知識產權的存儲芯片設計公司。

-

DRAM

+關注

關注

40文章

2325瀏覽量

183865 -

DDR3

+關注

關注

2文章

276瀏覽量

42385 -

接口

+關注

關注

33文章

8691瀏覽量

151912 -

低功耗

+關注

關注

10文章

2418瀏覽量

103895 -

DDR4

+關注

關注

12文章

322瀏覽量

40956

原文標題:【芯科普】DRAM產品低功耗設計與演化

文章出處:【微信號:東芯半導體,微信公眾號:東芯半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

介紹無線通信產品的低功耗設計

做低功耗產品主要把握哪幾點呢

便攜式產品具有低功耗意識的FPGA設計方法

專為5G和AI設計的低功耗DDR5 DRAM

MCU低功耗設計(三)產品

使用HT32產品及如何安排低功耗模式

DRAM產品低功耗設計與演化

DRAM產品低功耗設計與演化

評論