Verilog 最常用的 2 種數(shù)據(jù)類型就是線網(wǎng)(wire)與寄存器(reg),其余類型可以理解為這兩種數(shù)據(jù)類型的擴展或輔助。

線網(wǎng)(wire)

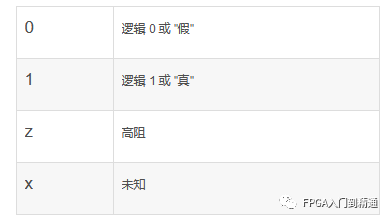

wire 類型表示硬件單元之間的物理連線,由其連接的器件輸出端連續(xù)驅(qū)動。如果沒有驅(qū)動元件連接到 wire 型變量,缺省值一般為 “Z”。舉例如下:

wire interrupt ;

wire flag1, flag2 ;

wire gnd = 1'b0 ;

線網(wǎng)型還有其他數(shù)據(jù)類型,包括 wand,wor,wri,triand,trior,trireg 等。這些數(shù)據(jù)類型用的頻率不是很高,這里不做介紹。

寄存器(reg)

寄存器(reg)用來表示存儲單元,它會保持數(shù)據(jù)原有的值,直到被改寫。聲明舉例如下:

reg clk_temp;

reg flag1, flag2 ;

例如在 always 塊中,寄存器可能被綜合成邊沿觸發(fā)器,在組合邏輯中可能被綜合成 wire 型變量。寄存器不需要驅(qū)動源,也不一定需要時鐘信號。在仿真時,寄存器的值可在任意時刻通過賦值操作進行改寫。例如:

reg rstn ;

initial begin

rstn = 1'b0 ;

#100 ;

rstn = 1'b1 ;

end

向量

◆當(dāng)位寬大于1時,wire 或 reg 即可聲明為向量的形式。例如:

reg [3:0] counter ; //聲明4bit位寬的寄存器counter

wire [32-1:0] gpio_data; //聲明32bit位寬的線型變量gpio_data

wire [8:2] addr ; //聲明7bit位寬的線型變量addr,位寬范圍為8:2

reg [0:31] data ; //聲明32bit位寬的寄存器變量data, 最高有效位為0

◆對于上面的向量,我們可以指定某一位或若干相鄰位,作為其他邏輯使用。例如:

wire [9:0] data_low = data[0:9] ;

addr_temp[3:2] = addr[8:7] + 1'b1 ;

◆Verilog 支持可變的向量域選擇,例如:

reg [31:0] data1 ;

reg [7:0] byte1 [3:0];

integer j ;

always@* begin

for (j=0; j<=3;j=j+1) begin

byte1[j] = data1[(j+1)*8-1 -: 8];

//把data1[7:0]…data1[31:24]依次賦值

//給byte1[0][7:0]…byte[3][7:0]

end

end

◆Verillog 還支持指定 bit 位后固定位寬的向量域選擇訪問。

[bit+: width] : 從起始 bit 位開始遞增,位寬為 width。

[bit-: width] : 從起始 bit 位開始遞減,位寬為 width。

//下面 2 種賦值是等效的

A = data1[31-: 8] ;

A = data1[31:24] ;

//下面 2 種賦值是等效的

B = data1[0+ : 8] ;

B = data1[0:7] ;

◆對信號重新進行組合成新的向量時,需要借助大括號。例如:

wire [31:0] temp1, temp2 ;

assign temp1 = {byte1[0][7:0], data1[31:8]}; //數(shù)據(jù)拼接

assign temp2 = {32{1'b0}}; //賦值32位的數(shù)值0

整數(shù),實數(shù),時間寄存器變量

整數(shù),實數(shù),時間等數(shù)據(jù)類型實際也屬于寄存器類型。

◆整數(shù)(integer)

整數(shù)類型用關(guān)鍵字 integer 來聲明。聲明時不用指明位寬,位寬和編譯器有關(guān),一般為32 bit。reg 型變量為無符號數(shù),而 integer 型變量為有符號數(shù)。例如:

reg [31:0] data1 ;

reg [7:0] byte1 [3:0]; //數(shù)組變量,后續(xù)介紹

integer j ; //整型變量,用來輔助生成數(shù)字電路

always@* begin

for (j=0; j<=3;j=j+1) begin

byte1[j] = data1[(j+1)*8-1 -: 8];

//把data1[7:0]…data1[31:24]依次賦值

//給byte1[0][7:0]…byte[3][7:0]

end

end

此例中,integer 信號 j 作為輔助信號,將 data1 的數(shù)據(jù)依次賦值給數(shù)組 byte1。綜合后實際電路里并沒有 j 這個信號,j 只是輔助生成相應(yīng)的硬件電路。

◆實數(shù)(real)

實數(shù)用關(guān)鍵字 real 來聲明,可用十進制或科學(xué)計數(shù)法來表示。實數(shù)聲明不能帶有范圍,默認值為 0。如果將一個實數(shù)賦值給一個整數(shù),則只有實數(shù)的整數(shù)部分會賦值給整數(shù)。例如:

real data1 ;

integer temp ;

initial begin

data1 = 2e3 ;

data1 = 3.75 ;

end

initial begin

temp = data1 ; //temp 值的大小為3

end

** ◆時間(time)**

Verilog 使用特殊的時間寄存器 time 型變量,對仿真時間進行保存。其寬度一般為 64 bit,通過調(diào)用系統(tǒng)函數(shù) $time 獲取當(dāng)前仿真時間。例如:

time current_time ;

initial begin

#100 ;

current_time = $time ; //current_time 的大小為100

end

數(shù)組

在 Verilog 中允許聲明 reg, wire, integer, time, real 及其向量類型的數(shù)組。

數(shù)組維數(shù)沒有限制。線網(wǎng)數(shù)組也可以用于連接實例模塊的端口。數(shù)組中的每個元素都可以作為一個標量或者向量,以同樣的方式來使用,形如:<數(shù)組名>[<下標>]。對于多維數(shù)組來講,用戶需要說明其每一維的索引。例如:

integer flag [7:0] ; //8個整數(shù)組成的數(shù)組

reg [3:0] counter [3:0] ; //由4個4bit計數(shù)器組成的數(shù)組

wire [7:0] addr_bus [3:0] ; //由4個8bit wire型變量組成的數(shù)組

wire data_bit[7:0][5:0] ; //聲明1bit wire型變量的二維數(shù)組

reg [31:0] data_4d[11:0][3:0][3:0][255:0] ; //聲明4維的32bit數(shù)據(jù)變量數(shù)組

下面顯示了對數(shù)組元素的賦值操作:

flag [1] = 32'd0 ; //將flag數(shù)組中第二個元素賦值為32bit的0值

counter[3] = 4'hF ; //將數(shù)組counter中第4個元素的值賦值為4bit 十六進制數(shù)F,等效于counter[3][3:0] = 4'hF,即可省略寬度;

assign addr_bus[0] = 8'b0 ; //將數(shù)組addr_bus中第一個元素的值賦值為0

assign data_bit[0][1] = 1b'1; //將數(shù)組data_bit的第1行第2列的元素賦值為1,這里不能省略第二個訪問標號,即 assign data_bit[0] = 1'b1; 是非法的。

data_4d[0][0][0][0][15:0] = 15'd3 ; //將數(shù)組data_4d中標號為[0][0][0][0]的寄存器單元的15~0bit賦值為3

雖然數(shù)組與向量的訪問方式在一定程度上類似,但不要將向量和數(shù)組混淆。向量是一個單獨的元件,位寬為 n;數(shù)組由多個元件組成,其中每個元件的位寬為 n 或 1。它們在結(jié)構(gòu)的定義上就有所區(qū)別。

存儲器

存儲器變量就是一種寄存器數(shù)組,可用來描述 RAM 或 ROM 的行為。例如:

reg membit[0:255] ; //256bit的1bit存儲器

reg [7:0] mem[0:1023] ; //1Kbyte存儲器,位寬8bit

mem[511] = 8'b0 ; //令第512個8bit的存儲單元值為0

參數(shù)用來表示常量,用關(guān)鍵字 parameter 聲明,只能賦值一次。例如:

parameter data_width = 10'd32 ;

parameter i=1, j=2, k=3 ;

parameter mem_size = data_width * 10 ;

通過模塊例化的方式,可以更改參數(shù)在模塊中的值。此部分以后會介紹。

局部參數(shù)用 localparam 來聲明,其作用和用法與 parameter 相同,區(qū)別在于它的值不能被改變。所以當(dāng)參數(shù)只在本模塊中調(diào)用時,可用 localparam 來聲明。

字符串

字符串保存在 reg 類型的變量中,每個字符占用一個字節(jié)(8bit)。因此寄存器變量的寬度應(yīng)該足夠大,以保證不會溢出。

字符串不能多行書寫,即字符串中不能包含回車符。如果寄存器變量的寬度大于字符串的大小,則使用 0 來填充左邊的空余位;如果寄存器變量的寬度小于字符串大小,則會截去字符串左邊多余的數(shù)據(jù)。例如,為存儲字符串 “run.runoob.com”, 需要 14*8byte 的存儲單元:

reg [0: 14*8-1] str ;

initial begin

str = "run.runoob.com";

end

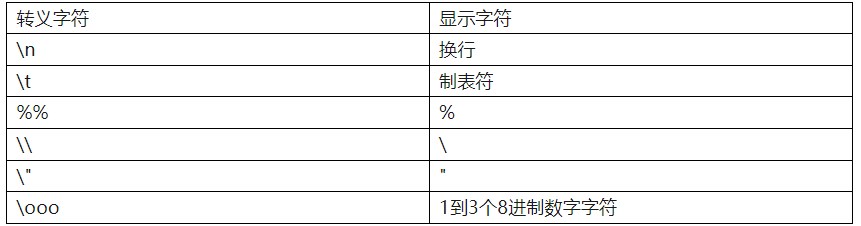

有一些特殊字符在顯示字符串中有特殊意義,例如換行符,制表符等。如果需要在字符串中顯示這些特殊的字符,則需要在前面加前綴轉(zhuǎn)義字符 “\\”。

其實,在 SystemVerilog(主要用于 Verilog 仿真的編程語言)語言中,已經(jīng)可以直接用關(guān)鍵字 string 來表示字符串變量類型,這為 Verilog 的仿真帶來了極大的便利。有興趣的學(xué)者可以簡單學(xué)習(xí)下 SystemVerilog。

-

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

121155 -

ROM

+關(guān)注

關(guān)注

4文章

575瀏覽量

85987 -

RAM

+關(guān)注

關(guān)注

8文章

1369瀏覽量

114999 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110390 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2003瀏覽量

61346

發(fā)布評論請先 登錄

相關(guān)推薦

Python中常用的數(shù)據(jù)類型

【FPGA學(xué)習(xí)】Verilog HDL 語言的標識符和數(shù)據(jù)類型有哪些?

Verilog 變量聲明與數(shù)據(jù)類型二

Verilog 變量聲明與數(shù)據(jù)類型一

type( ) 函數(shù)查詢數(shù)據(jù)類型是什么

什么是數(shù)據(jù)類型轉(zhuǎn)換

Verilog中的基本數(shù)據(jù)類型

細說redis十種數(shù)據(jù)類型及底層原理

Verilog最常用的2種數(shù)據(jù)類型

Verilog最常用的2種數(shù)據(jù)類型

評論