隨著電子技術(shù)的飛速發(fā)展,集成電路正沿著三個方向發(fā)展:一是集成電路芯片的特征尺寸向不斷縮小的方向發(fā)展;二是大量的不同需求催生多種類型的集成電路芯片;三是為滿足小型化而朝著系統(tǒng)集成方向發(fā)展。因此國際上提出,一方面,半導(dǎo)體技術(shù)將延續(xù)摩爾定律(More Moore)發(fā)展,不斷增強系統(tǒng)級芯片(SoC)的功能和集成度;另一方面,更多類型、更多功能的芯片或器件將通過系統(tǒng)級封裝(SiP)實現(xiàn)集成,向著超越摩爾定律的方向發(fā)展。

SoC 和SiP 技術(shù)是兩種有效的系統(tǒng)集成解決方案,各有優(yōu)缺點,也有各自特定的應(yīng)用場景,為持續(xù)改善電子系統(tǒng)的性能、功耗、成本和尺寸提供了新的發(fā)展途徑。隨著半導(dǎo)體器件尺寸的特續(xù)縮小,SoC 將會面臨諸如工藝波動嚴重、光刻成本增加、器件性能變差、器件功耗增加等嚴峻挑戰(zhàn)。由于工藝不同,SoC將模擬、射頻、數(shù)字甚至光電 功能整合在一起的難度很大,天線、MEMS 等徽機械結(jié)構(gòu)的集成更加困難。而且在大多數(shù)情況下,SoC 的成本要高于不同功能分立器件的總和,因此 SiP 技術(shù)越來越受到業(yè)界重視。SP 技術(shù)是基于 SoC 技術(shù)發(fā)展起來的,具有靈活、易于擴展的特點,是SoC 技術(shù)的有效補充,但不會替代 SoC技術(shù)。以光電集成技術(shù)為例,限于當(dāng)前光電子技術(shù)和集成制造工藝發(fā)展水平的限制,完全實現(xiàn)高性能的單片光電集成還有很多技術(shù)難題需要攻克,光子和電子混合集成在設(shè)計、加工、性能等方面仍舊具有巨大的優(yōu)勢。光子集成電路和電子集成電路技術(shù)的成熟和進步,推動了光電混合集成 SiP 成為光電組件及光模塊的關(guān)鍵技術(shù)。而通信容量的增加,以及光電網(wǎng)絡(luò)的升級改造,對光電混合集成的帶寬、功耗等方面提出了嚴格的要求,進而推動光子集成電路和電子集成電路在帶寬、功耗、制造工藝及集成方式等關(guān)鍵技術(shù)的進步,以滿足光電組件.光電模塊和光電系統(tǒng)的指標(biāo)要求。

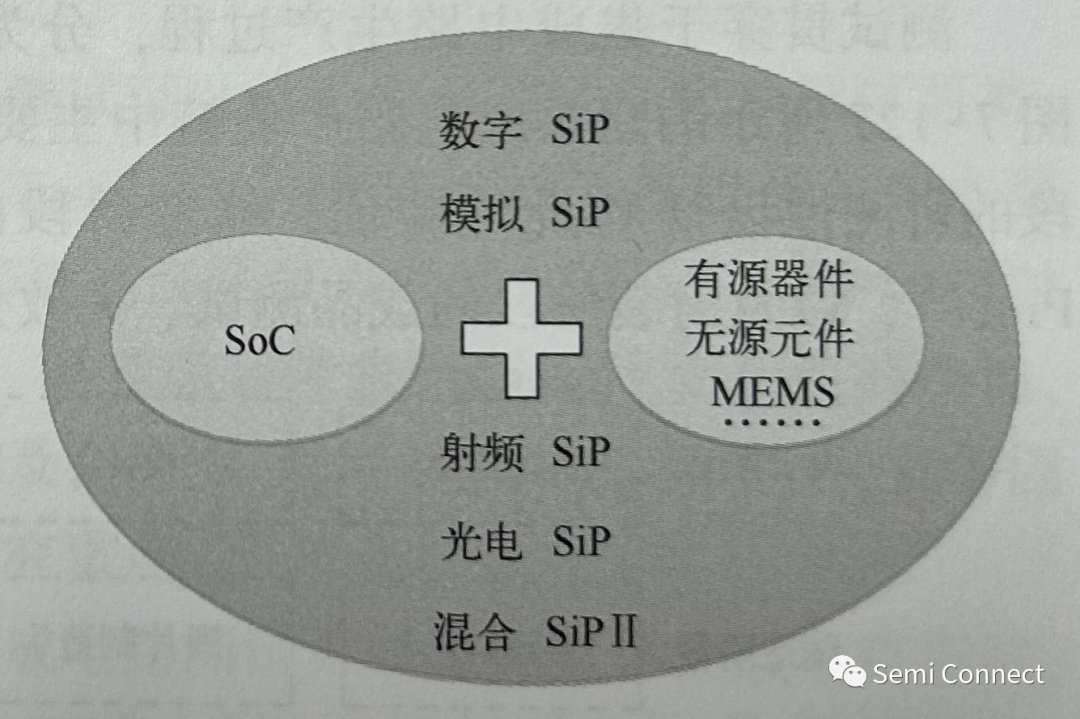

隨著新原理、新方法的采用,硬件與軟件聯(lián)合設(shè)計,以及制造工藝水平工藝兼容性的提高,SoC 的功能將會得到快速發(fā)展,對 SiP 技術(shù)工藝能力的需求也越來越高。高性能 SiP 的實現(xiàn)也會對 SoC 的引腳布局、物理尺寸、材料體系KGD (Known Good Die) 等提出要求。制造設(shè)備的提升,新型材料的引入,以及封裝工藝能力的不斷提升,也會支撐 SiP 技術(shù)擴展到基于更高端 SoC 的系統(tǒng)異質(zhì)集成的應(yīng)用。在基于 SoC 進行系統(tǒng)級封裝的過程中,許多新的封裝形式和封裝技術(shù)被相繼提出,這對 SoC 和SiP 從設(shè)計、材料、工藝、測試等多方面提出了新的挑戰(zhàn),因而需要 SoC和 SiP 在諸如信號完整性、熱管理可靠性、測試及互連制造技術(shù)等方面協(xié)同設(shè)計、互為補充、共同發(fā)展SoC 和 SiP 技術(shù)融合示意圖如圖所示。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

456文章

51170瀏覽量

427233 -

集成電路

+關(guān)注

關(guān)注

5392文章

11622瀏覽量

363175 -

SiP

+關(guān)注

關(guān)注

5文章

506瀏覽量

105455 -

soc

+關(guān)注

關(guān)注

38文章

4204瀏覽量

219090 -

制造工藝

+關(guān)注

關(guān)注

2文章

181瀏覽量

19812

原文標(biāo)題:SiP 和 SoC 的協(xié)同發(fā)展,SiP 和 SOC 的同展Co-development of SiP and SoC

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

一文讀懂SIP與SOC封裝技術(shù)

SoC與SiP混合設(shè)計出多樣化手機

SOC設(shè)計領(lǐng)域的核心技術(shù)-軟/硬件協(xié)同設(shè)計

簡單介紹SoC與SiP中芯片解密的應(yīng)用

系統(tǒng)級封裝(SiP)的發(fā)展前景(上)

從互操作看WCDMA/GSM雙網(wǎng)協(xié)同發(fā)展

SiP的特點與SOC的區(qū)別和SiP的應(yīng)用和發(fā)展方向的參考資料

如何促進5G+車聯(lián)網(wǎng)協(xié)同發(fā)展

“5G+車聯(lián)網(wǎng)”的車路協(xié)同發(fā)展模式促進智能汽車與智慧城市協(xié)同發(fā)展

數(shù)據(jù)中心與智能電網(wǎng)如何協(xié)同發(fā)展

中國6個城市首批試點智能網(wǎng)聯(lián)汽車協(xié)同發(fā)展

關(guān)于HIC、MCM、SIP封裝與SOC的區(qū)別

數(shù)字產(chǎn)業(yè)協(xié)同發(fā)展的意義和作用

數(shù)字產(chǎn)業(yè)協(xié)同發(fā)展的例子及主要內(nèi)容

多網(wǎng)協(xié)同發(fā)展探討

SiP和SoC的協(xié)同發(fā)展

SiP和SoC的協(xié)同發(fā)展

評論