本文是本系列的第三篇,本文主要介紹FPGA常用運(yùn)算模塊-乘加器,xilinx提供了相關(guān)的IP以便于用戶進(jìn)行開(kāi)發(fā)使用。

乘加器

乘加器核提供使用DSP片的乘加實(shí)現(xiàn)。 它執(zhí)行兩個(gè)操作數(shù)的乘法,并將全精度乘積加(或減)到第三個(gè)操作數(shù),執(zhí)行P = C +/- A * B的操作。 乘加器模塊對(duì)有符號(hào)或無(wú)符號(hào)數(shù)據(jù)進(jìn)行操作。 該模塊可以流水線化。 支持二補(bǔ)符號(hào)和無(wú)符號(hào)操作。 支持從1到52位無(wú)符號(hào)或2到53位有符號(hào)的乘數(shù)輸入和從1到105位無(wú)符號(hào)或2到106位有符號(hào)的加減操作數(shù)輸入。 可選時(shí)鐘啟用和同步清除。

乘加器IP在許多配置中比單獨(dú)的乘和加操作更有效,因?yàn)樗褂肈SP48原語(yǔ)。 可以在許多應(yīng)用程序中使用這個(gè)IP,特別是那些基于多項(xiàng)式算法的應(yīng)用程序,如FIR和IIR實(shí)現(xiàn)。

IP核圖示以及端口介紹

| Name | I/O | Description |

|---|---|---|

| A[N:0] | Input | A輸入(乘法操作數(shù)1) |

| B[M:0] | Input | B輸入(乘法操作數(shù)2) |

| C[L:0] | Input | C輸入(加減操作數(shù)) |

| PCIN | Input | 級(jí)聯(lián)輸入 |

| SUBTRACT | Input | 控制加/減操作(1=減法,0=加法) |

| CE | Input | 時(shí)鐘使能 (高有效) |

| CLK | Input | 時(shí)鐘信號(hào),上升沿有效 |

| SCLR | Input | 同步復(fù)位,高有效 |

| PCOUT | Output | 輸出級(jí)聯(lián) |

| P[Q:0] | Output | 輸出端口 |

操作指南

流水操作

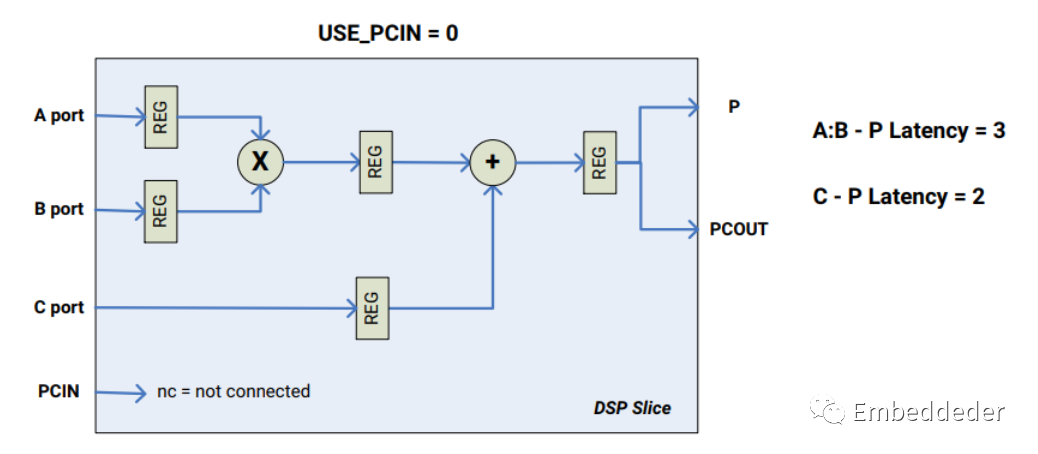

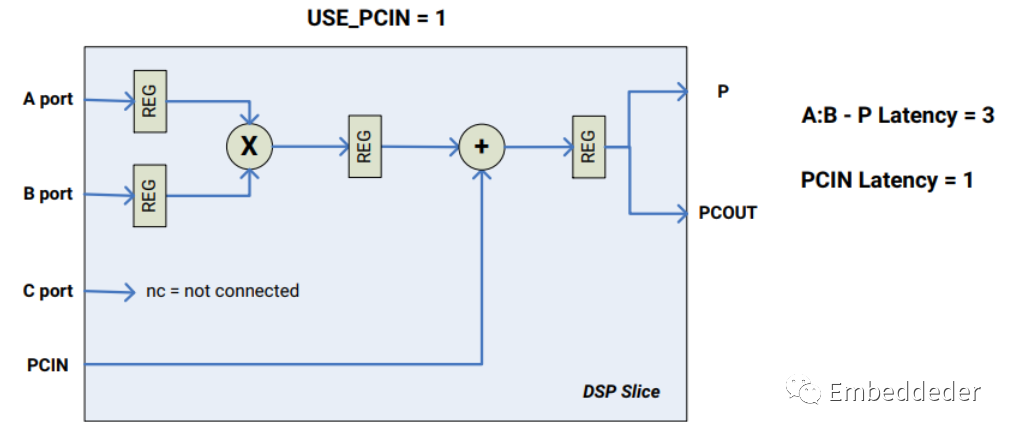

乘法器核心考慮了兩種不同的延遲路徑; 一個(gè)是從A和B輸入到P輸出,另一個(gè)是從C/PCIN輸入到P輸出。 這些延遲被定義為A:B - P延遲和C - P延遲。

這些延遲只能采用兩個(gè)值:0 表示無(wú)延遲或 -1 表示最大/最佳延遲。 如果這兩個(gè)延遲中的任何一個(gè)指定為 -1,則它們都被視為 -1; 對(duì)于完全組合的設(shè)計(jì),兩者都必須設(shè)置為 0。

級(jí)聯(lián)的PCIN端口的使用也會(huì)影響延遲。

不用級(jí)聯(lián)輸入:

使用級(jí)聯(lián)輸入:

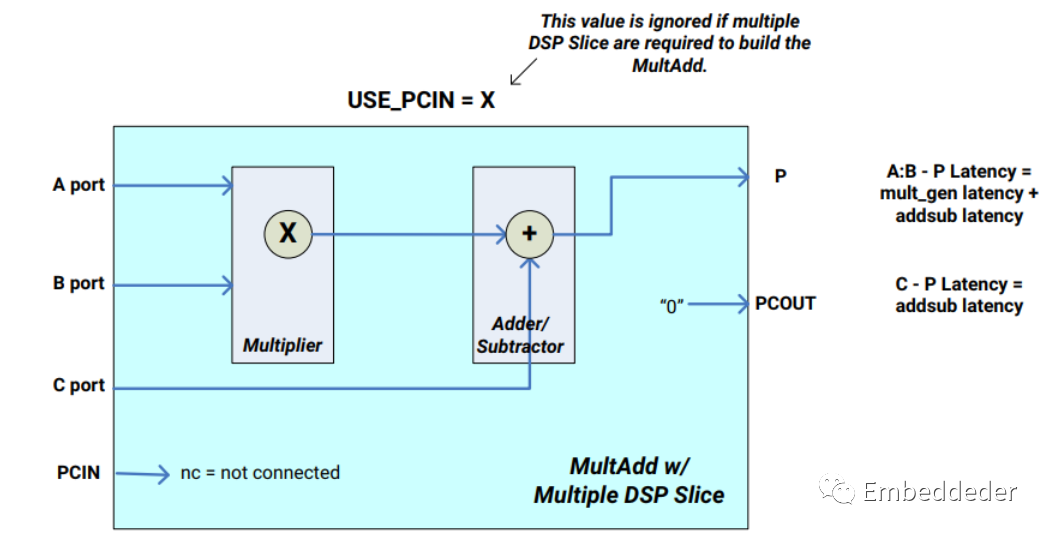

下圖顯示了乘加器的內(nèi)部結(jié)構(gòu),在內(nèi)部相當(dāng)于引用了一個(gè)乘法器和一個(gè)加減法器。 從該結(jié)構(gòu)中可以清楚的看出,A:B - P 延時(shí)和C - P延時(shí)路徑。

數(shù)據(jù)調(diào)整

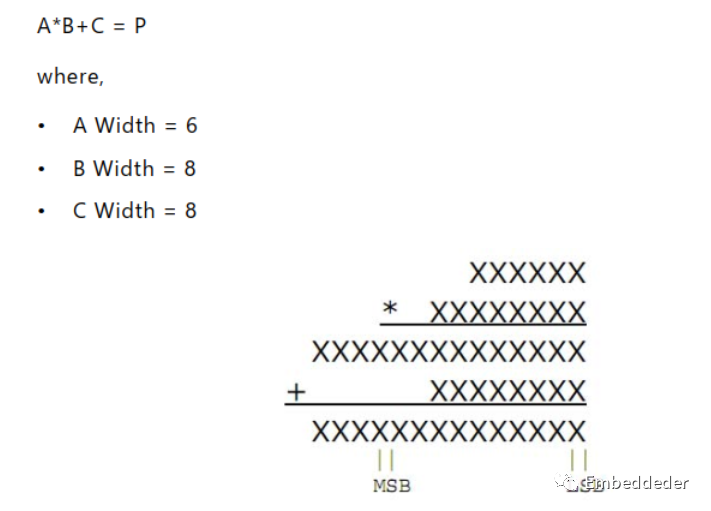

當(dāng)傳遞給IP輸入時(shí),所有輸入都是右對(duì)齊的。 必須設(shè)置輸入的正確 LSB 或 MSB 填充或符號(hào)擴(kuò)展(相當(dāng)于二進(jìn)制小數(shù)點(diǎn))。

在乘法加法器中,乘法器輸出沒(méi)有截?cái)嗷蛏崛耄?這是一個(gè)完整的精確結(jié)果。 C 輸入被添加到乘積中。 下面的例子實(shí)現(xiàn)了切片操作的功能。 切片選取輸出的0到11位。

向量相乘的例子

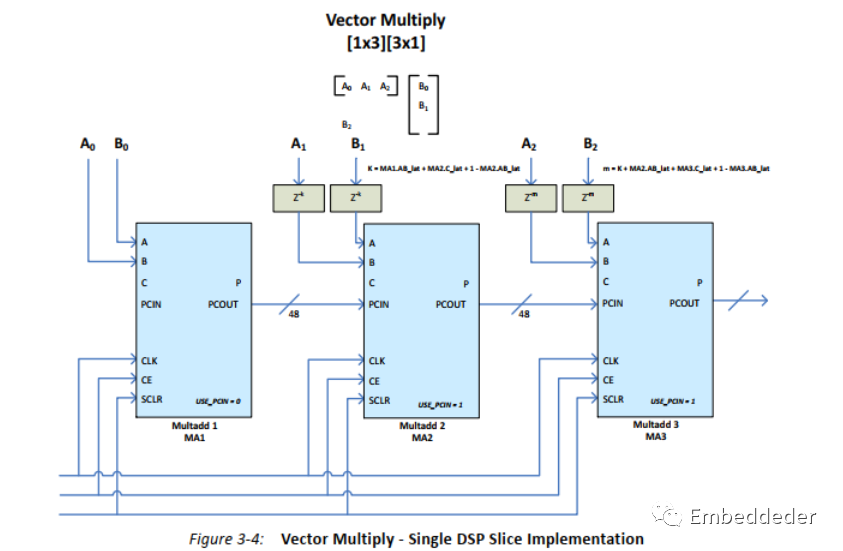

圖3-4(單DSP片實(shí)現(xiàn))和圖3-5(多DSP片實(shí)現(xiàn))實(shí)現(xiàn)了一個(gè)簡(jiǎn)單的矢量乘法。在3-4圖中,如果使用單DSP片實(shí)現(xiàn)向量相乘,則按照該圖示連接進(jìn)行實(shí)現(xiàn)。采用級(jí)聯(lián)操作,將級(jí)聯(lián)是輸入輸出相互連接。此時(shí)不能進(jìn)行設(shè)置C的輸入。

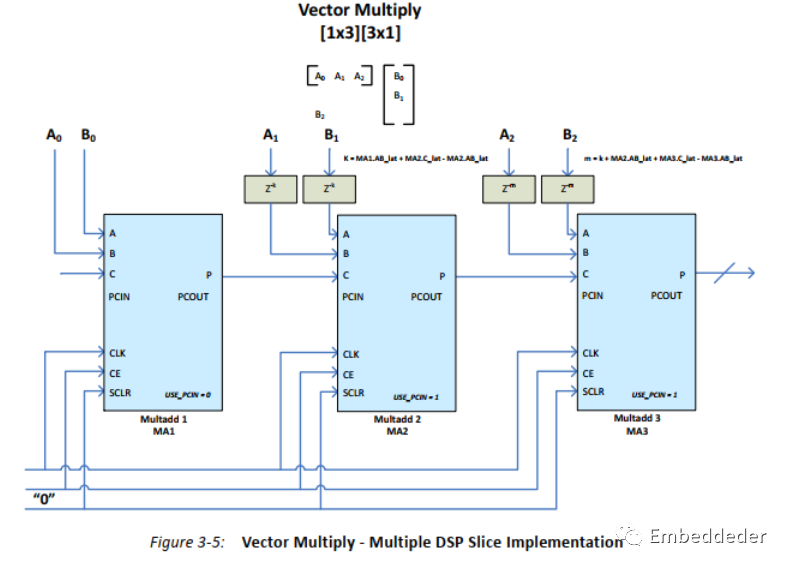

在3-5圖中,如果使用多DSP片實(shí)現(xiàn),則按照該圖示連接進(jìn)行實(shí)現(xiàn)。此時(shí)可以進(jìn)行設(shè)置C的輸入,級(jí)聯(lián)操作通過(guò)連接P和C端相互連接。

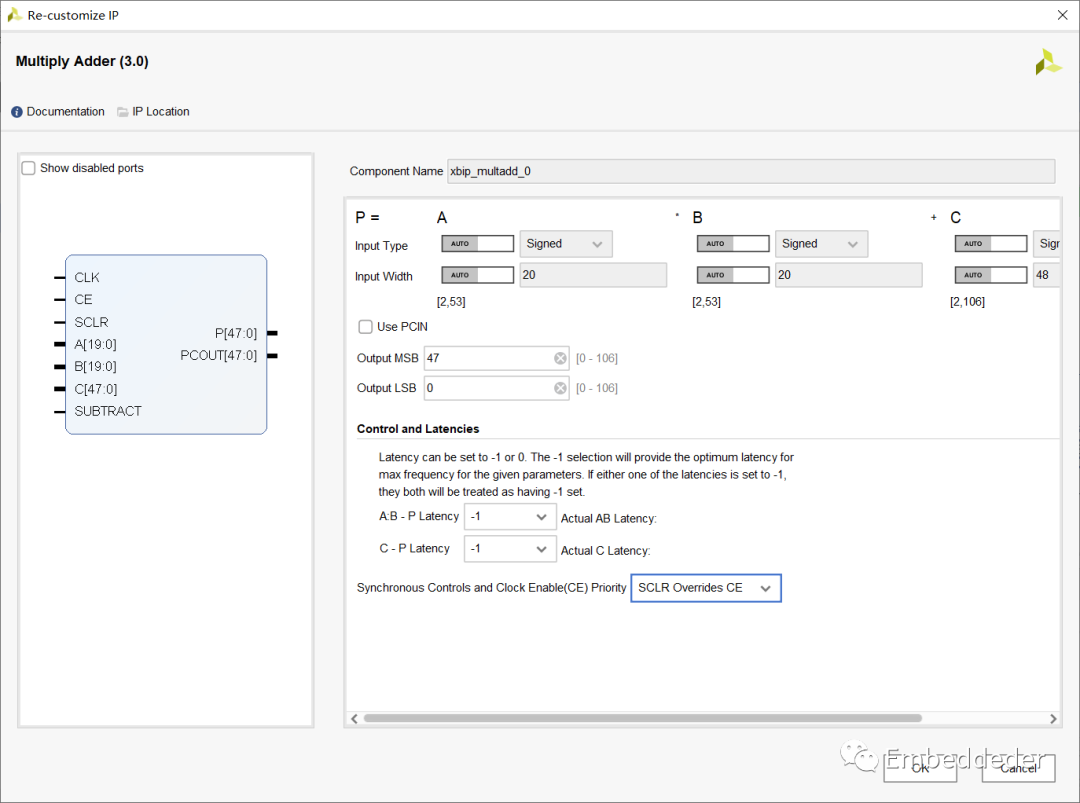

乘加器IP配置

在乘加器IP配置界面,可以對(duì)輸入輸出的位寬進(jìn)行配置,以及相關(guān)IP的配置。

A/B Input Width :設(shè)置端口A或者B輸入的寬度。有效的范圍是1 ~ 52無(wú)符號(hào)和2 ~ 53有符號(hào)。默認(rèn)值為18。該值在IP中自動(dòng)設(shè)置,可以手動(dòng)設(shè)置。

C Input Width :設(shè)置端口C(加/減操作數(shù))輸入的寬度。有效的范圍是1到105無(wú)符號(hào)和2到106有符號(hào)。默認(rèn)值為48。該值在IP中自動(dòng)設(shè)置,可以手動(dòng)設(shè)置。

A/B/C Input Type :設(shè)置端口A、B 、C數(shù)據(jù)的類型。0表示有符號(hào),1表示無(wú)符號(hào)。默認(rèn)值為0。該值在IP中自動(dòng)設(shè)置,可以手動(dòng)設(shè)置。

Output MSB / Output LSB :設(shè)置輸出的切片位寬范圍。

Use PCIN :當(dāng)該參數(shù)設(shè)置為1時(shí),使用PCIN 端口。 PCIN 端口是 加法器/減法器操作數(shù)的級(jí)聯(lián)輸入端口。設(shè)置為0時(shí),PCIN 端口為 忽略。設(shè)置為 1 時(shí),C 輸入寬度限制為 48 位。

Sync Control CE Priority :此參數(shù)控制 SCLR和CE信號(hào)的優(yōu)先級(jí)當(dāng)該信號(hào)為0時(shí),Sync Control CE Priority。當(dāng)該信號(hào)為1時(shí),SCLR 僅在 CE 為高電平時(shí)有效。這默認(rèn)值為0。

A:B - P Latency : A、B端口到輸出端口P的時(shí)延。 取值如下: -1, 0。 默認(rèn)值為-1。

C - P Latency :從 C 或 PCIN 端口到輸出端口 P 的延遲。 取值如下: -1, 0。 默認(rèn)值為-1。

-

dsp

+關(guān)注

關(guān)注

554文章

8059瀏覽量

350415 -

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605997 -

Xilinx

+關(guān)注

關(guān)注

71文章

2171瀏覽量

122132 -

IP核

+關(guān)注

關(guān)注

4文章

331瀏覽量

49635 -

乘加器

+關(guān)注

關(guān)注

0文章

4瀏覽量

6048

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于FPGA的實(shí)時(shí)互相關(guān)運(yùn)算器

基于改進(jìn)的CORDIC算法的FFT復(fù)乘及其FPGA實(shí)現(xiàn)

stm32f407進(jìn)行一次32*32的乘加運(yùn)算需要多少ns

機(jī)器學(xué)習(xí)處理器單元支持浮點(diǎn)的乘加運(yùn)算

基于51單片機(jī)的5乘4計(jì)算器設(shè)計(jì)

基于流水線重構(gòu)技術(shù)的16x16位乘加器的設(shè)計(jì)

HT MCU 加、減、乘、除法

運(yùn)算器,運(yùn)算器的作用和原理是什么?

FPGA浮點(diǎn)數(shù)轉(zhuǎn)化為定點(diǎn)數(shù)方法

FPGA常用運(yùn)算模塊-加減法器和乘法器

FPGA常用運(yùn)算模塊-除法器

FPGA常用運(yùn)算模塊-復(fù)數(shù)乘法器

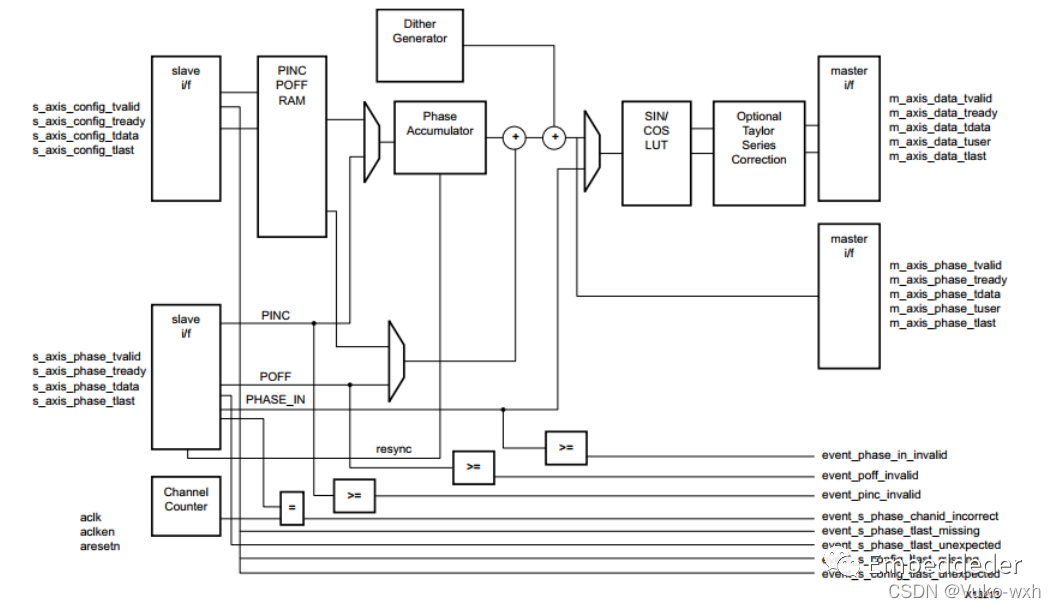

FPGA常用運(yùn)算模塊-DDS信號(hào)發(fā)生器

基于FPGA的計(jì)算器設(shè)計(jì)

FPGA常用運(yùn)算模塊-乘加器

FPGA常用運(yùn)算模塊-乘加器

評(píng)論